Последовательностные схемы

реклама

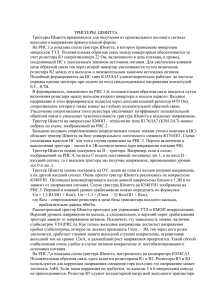

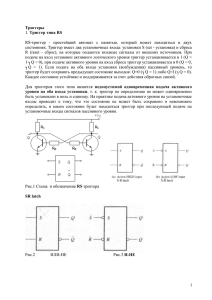

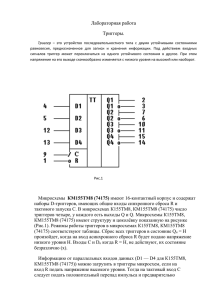

МИНИСТЕРСТВО НАУКИ, ОБРАЗОВАНИЯ И КУЛЬТУРЫ ПМР Приднестровский государственный университет им. Т. Г. Шевченко Кафедра “Вычислительные комплексы, системы и сети” Последовательностные схемы Методическое пособие по курсу “Схемотехника ЭВМ” для студентов специальности 22.01.00 “Вычислительные комплексы, системы и сети” Тирасполь, 2001 1 Данное методическое пособие содержит теоретические материалы, примеры построения цифровых схем, контрольные вопросы и задания по разделу “Последовательностные схемы” курса “Схемотехника ЭВМ”. Пособие отвечает требованиям программы высшего учебного заведения по данному курсу. Рекомендуется для преподавателей и студентов 3-го курса специальности “Вычислительные комплексы, системы и сети”. Составитель: Варзяев А. В. Утверждено Научно-методическим советом ПГУ им. Т. Г. Шевченко. Приднестровский государственный университет им. Т. Г. Шевченко, 2001 2 Содержание Глава 1. Триггеры 4 Асинхронный RS-триггер на элементах ИЛИ-НЕ 4 Асинхронный RS-триггер на элементах И-НЕ 5 Синхронный RS-триггер 6 Статический D-триггер 7 Динамический D-триггер 8 Двухступенчатый триггер 9 JK-триггер 10 T-триггер (счетный триггер) 11 Глава 2. Регистры 12 Параллельный регистр 12 Последовательный регистр 14 Универсальный регистр 15 Глава 3. Счетчики. 16 Асинхронный счетчик с последовательным переносом 16 Увеличение разрядности счётчиков 19 Реверсивные счётчики 20 Асинхронный счетчик с параллельным переносом 21 Синхронный счетчик с параллельным переносом 23 Счетчик с произвольным коэффициентом счёта 25 Счётчик с предварительной установкой 26 Список литературы 30 3 Последовательностные схемы (автоматы) – это схемы, выходные сигналы которых зависят не только от входных сигналов, но и от внутреннего состояния схемы в данный момент времени. Последовательностные схемы всегда имеют обратные связи. Теория построения и описания таких схем была изучена в дисциплине “Теория автоматов”. Глава 1. Триггеры Триггер является основным элементом последовательностной логики. Триггер это устройство с двумя устойчивыми состояниями равновесия, предназначенное для записи и хранения информации. Как правило, триггер имеет 2 выхода: прямой Q и инверсный Q . Число входов зависит от выполняемых функций. По способу записи информации триггеры делятся на асинхронные изменяться в и синхронные. любой момент синхронизируемых триггерах определенные В асинхронных времени при триггерах изменении информация входных может сигналов. В информация на выходе может изменяться только в моменты времени, задаваемые дополнительным синхронизирующим сигналом. Асинхронный RS-триггер на элементах ИЛИ-НЕ Асинхронный RS-триггер может быть построен на двух элементах ИЛИ-НЕ, охваченных цепями обратных связей. Схема и условное обозначение его показаны на рис.1. R 1 Q S T R Триггер имеет 2 входа: S (от англ. set - установка) и R Рис. 1 1 S (reset - сброс). Q Рассмотрим его работу. Активным уровнем на входе триггера является состояние лог. “1”. Пусть на обоих входах уровни сигналов не активны, т. е. S = R = 0. Тогда триггер находится в одном из устойчивых состояний Q = 0 Q = 1 или наоборот, Q = 1 Q = 0, в чем легко убедиться по схеме. Теперь, пусть на входе S уровень равен 1. 4 Тогда Q = 0, и, следовательно, Q = 1. Триггер установлен. Единица на выходе Q, в свою очередь, по цепи обратной связи поддерживает выход Q в состоянии 0. По этой причине триггер будет находиться в состоянии "1" даже после снятия лог. "1" на выходе S. После того, как на вход S будет подан не активный уровень лог. "0", триггер будет находиться в состоянии хранения информации. В силу симметрии схемы, аналогичные процессы будут происходить при подаче активного сигнала лог. "1" на вход R. Триггер будет сброшен (т. е. установлен в состояние "0"). Состояние, когда на оба входа подан активный уровень (т. е. S = R = 1), является запрещенным и в работе не используется. Как легко видеть из схемы, в этом случае на обоих выходах схемы будет состояние лог. "0", т. е. выходы не являются инверсными друг другу. Работа триггеров (и других последовательностных устройств) описывается так называемой диаграммой состояний. Состояние после воздействия входных сигналов обозначаются Qn+1 (т. е. в n+1-й момент времени), а состояние до воздействия входных сигналов – Qn. (Либо, соответственно, Qn и Qn-1). Диаграмма состояний асинхронного RS-триггера на элементах ИЛИ-НЕ: S R Qn+1 Режим 0 0 Qn Хранение 0 1 0 Сброс 1 0 1 Установка 1 1 X Запрещенное состояние Асинхронный RS-триггер на элементах И-НЕ Схема, условное обозначение и диаграмма состояний показаны на рис. 2. S & Q S T R Рис. 2 & R Q 5 S R Qn+1 Режим 0 0 Qn Запрещенное состояние 0 1 0 Установка 1 0 1 Сброс 1 1 X Хранение Логика работы этого триггера совершенно аналогична работе триггера на элементах ИЛИ-НЕ. Отличием является то, что активным уровнем на входах является уровень лог. "0", состояние хранения – S = R = 1, а запрещенное состояние – S = R = 0. RS-триггеры, выпускаемые в виде ИМС, обозначаются буквами ТР. Примерами являются ИМС 555ТР2 (4 RS-триггера с инверсными входами) и 561ТР2 (4 RSтриггера с тремя состояниями выхода). Синхронный RS-триггер. Синхронный RS-триггер отличается от асинхронного тем, что изменение информации в нем может происходить только при наличии определенного синхронизирующего сигнала, обычно обозначаемого буквой C (clock). В отсутствие синхросигнала триггер всегда находится в состоянии хранения. Пример синхронного RS-триггера, его условное обозначение и диаграмма состояний изображены на рис. 3. & 1 S & 3 Q S T C С R R 6 & 2 & 4 C S R Qn+1 0 X X Qn 1 0 0 Qn 1 0 1 0 1 1 0 1 1 1 1 X Q Рис. 3 Когда С = 0, выходы лог. элементов 1 и 2 находятся в состоянии "1" независимо от сигналов на входах S и R и RS-триггер на элементах 3 и 4 всегда находится в состоянии хранения информации. В случае С = 1, сигналы S и R инвертируются элементами 1 и 2 и поступают на входы элементов 3 и 4, т. е. при С = 1 триггер работает как обычный асинхронный RS-триггер на элементах И-НЕ, за исключением того, что входы S и R инвертируются. Естественно, можно построить другие варианты синхронных RS-триггеров с использованием других логических элементов, например: ИЛИ-НЕ, И, ИЛИ, имеющих свои диаграммы состояний. В случае, если разрешение дается сигналом С = 0, то на входе С ставится кружок- символ инверсии. Задания. Постройте различными самостоятельно комбинациями различные прямых и схемы инверсных синхронных входов С RS-триггеров и с Схемы RS. минимизировать. Статический D-триггер Другие названия: называется синхронный триггер-защелка, триггер, имеющий прозрачная защелка. 2 входа: вход D-триггером данных D и вход синхронизации С. Он переключается по сигналу на входе C в состояние, в котором в данный момент находится вход D. Схема, условное обозначение и диаграмма состояний этого триггера (см. рис. 4) похожи на схему синхронного RS-триггера, у которого входы S и R всегда инверсны и заменены одним входом D (сравнить с рис. 3). D & & Q Данную С минимизировать & схему и можно получить более компактную (см. рис. 5.). & Q 1 Рис. 4 7 D & & Q С & C D Qn+1 0 X Qn 1 0 0 1 1 1 & Q Рис. 5 В случае, когда С = 0, триггер находится в состоянии хранения. Если С = 1, то выход Q повторяет состояние входа D. При С = 1 защелка прозрачна: любое изменение входа D вызывает изменение выхода Q. При переходе сигнала на входе С из "1" в "0" триггер-защелка фиксирует (защелкивает) последнее состояние входа D. При С = 1 свойство запоминания информации проявляться не будет и триггер будет представлять собой просто повторитель входного сигнала D. В некотором смысле D-триггер задерживает прохождение поступившего на D-вход сигнала, откуда и произошло название триггера (англ. delay - задержка). Динамический D-триггер Другое название: триггер Вебба. Динамический триггер исключает сквозную передачу сигнала с D-входа на выход триггера во время действия синхроимпульса. Информация записывается только в момент перепада напряжения (или фронта) на входе С. Схема такого триггера значительно сложнее, а условное обозначение отличается тем, что динамический вход С изображается наклонной чертой, либо стрелкой (см. рис. 6). Микросхемы D-триггеров обозначаются буквами ТМ. Многие микросхемы имеют дополнительные RS-входы. Примерами являются очень распространенные ИМС 555ТМ2 и 561ТМ2. (555ТМ2 будет исследоваться в лабораторной работе). Задание. Рассмотрите самостоятельно работу триггера Вебба (рис. 6). 8 & & Q & С T D & C & Q Рис. 6 & D Двухступенчатый триггер Другое название - MS-триггер (от англ. Master-Slave: хозяин-раб). Он представляет собой два последовательно включенных синхронных RS-триггера. Первый из них называется ведущим или M-триггером, а второй - ведомым или S-триггером. Вариант схемы двухступенчатого триггера изображен на рис. 7. S T C R S T C R Из схемы видно, что при С = 1 происходит запись информации в первый триггер, 1 Рис. 7 а второй находится в состоянии хранения, т. к. на его входе в результате инверсии С = 0. При С = 0 прекращается запись информации в первый триггер и происходит запись состояния первого триггера во второй. Данный триггер непрозрачен по входам S и R, хотя каждая его ступень прозрачна. Один из триггеров всегда является запертым по входу С. Смена информации происходит только в момент заднего фронта синхросигнала С. 9 JK-триггер Синхронный JK-триггер с динамическим управлением (по фронту синхросигнала С) можно построить на базе двухступенчатого триггера, как показано на рис. 8а. Изображенный триггер синхронизируется задним фронтом сигнала С. При J = K = 0 состояние триггера не изменяется - хранение. Если J = 1, K = 0, то выход установится в состояние Qn+1 = 1; а) в случае, если предыдущее состояние Qn = 1, Qn~ = 0, то открыт нижний элемент И и разрешена запись по входу K, однако K = 0, следовательно, состояние триггера не меняется; б) в случае, если предыдущее состояние Qn = 0, Qn~ = 1, открыт верхний элемент И и происходит запись 1 по входу S, т. к. J = 1. Аналогично, при J = 0, K = 1 триггер установится в состояние Qn+1=0. В случае J = K = 1 состояние триггера изменится на противоположное Qn+1 = Qn, т. к., в любом случае, будет открыт тот из элементов И, который разрешает запись противоположного состояния. Из диаграммы состояний (рис. 8б) видно, что работа JK-триггера аналогична работе RS-триггера (вход J эквивалентен входу S, а вход K - входу R) за исключением того, что в состоянии J = K = 1, которое для RS-триггера является запрещенным, состояние JK-триггера инвертируется, т. е. меняется на противоположное. & J S С C C R R K & T S T Q J T C K Q 1 Рис. 8а Микросхемы, содержащие JK-триггеры, обозначаются буквами ТВ. Часто они так же как и D-триггеры имеют дополнительные приоритетные входы R и S. Примерами таких ИМС являются 555ТВ9 (рис. 9) и 561ТВ1. 10 C J K 0 0 0 1 1 0 1 1 0 X X 1 X X Qn+1 S T Qn J0 C K1 Qn R Qn Рис. 9 Qn Рис. 8б. Задания Постройте самостоятельно из ЛЭ различные схемы JK-триггеров с прямыми и инверсными входами J и K, переключающиеся по переднему и по заднему фронту синхросигнала С. T-триггер (счетный триггер) T-триггер (от англ. toggle – кувыркаться) имеет один управляющий вход T. При появлении положительного (или отрицательного) фронта на входе T, состояние на выходе изменяется на противоположное. Счетный триггер строится на основе JK-триггера путем объединения входов J и K. Как легко видеть из диаграммы состояний JK-триггера, в этом случае реализуются только 2 строки: J = K = 0 и J = K = 1. Другой вариант построения T-триггера - на основе динамического D-триггера. Примеры построения T-триггеров показаны на рис. 10. T T «1» J T K C T C D Рис. 10. Задания. Поясните, почему в схеме на рис. 10 должен использоваться обязательно динамический, а не статический D-триггер. Как будет работать схема, если использовать триггер-защелку? 11 Глава 2. Регистры Регистром (от англ. – Register, сокращенно - RG) наз. цифровой узел, предназначенный для запоминания (хранения) двоичных чисел. Все регистры можно разделить на два основных типа: параллельные и последовательные. Параллельный регистр В простейшем случае параллельный регистр или регистр памяти представляет собой несколько (4 или 8) D-триггеров с общим входом синхронизации С. На рис. 11 показаны схема построения и условное обозначение ИМС 555ТМ8. Сходным образом построены ИМС 555ТМ7, 555ТМ9, 564ТМ3. D0 D T C Q0 Q0 R D1 RG Q0 Q1 Q2 D T C Q1 C R Q3 Q1 R D2 D0 D1 D2 D3 Рис. 11 D T C Q2 Q2 R D3 D T C C R R Q3 Q3 За исключением приведенных, микросхемы регистров обозначаются буквами ИР. Параллельные регистры могут строиться с использованием как статических, так и динамических триггеров. Регистры, называются: «регистр-защелка». 12 построенные на триггерах-защелках, так и Кроме входа сброса R, регистры могут иметь вход разрешения записи Е, вход управления третьим состоянием выхода CS или OE. Различные ИМС регистров могут иметь различные комбинации перечисленных входов. В качестве примера можно привести 8-разрядный регистр 555ИР35, условное обозначение и таблица истинности для i-го разряда которого приведены на рис. 12. 0 1 2 3 4 5 6 7 RG 0 1 2 3 4 5 6 7 C R R 0 1 1 1 C Х 0,1 Di Х Х 0 1 Q (n+1),i 0 Q (n),i 0 1 Режим работы Сброс Хранение Запись «0» Запись «1» Рис. 12 Очень распространенным в микропроцессорной технике является изображенный на рис. 13 8-разрядный регистр-защелка с тремя состояниями выходов 8282 (отечественный аналог – 580ИР82). ИМС 8283 (580ИР83) отличается тем, что имеет инверсные выходы. 0 1 2 3 4 5 6 7 STB OE RG 0 1 2 3 4 5 6 7 OE STB 1 Х 0 0 0 1 0 1 Di Х Х 0 1 Q (n+1),i Z Q (n),i 0 1 Режим работы Хранение Хранение Запись «0» Запись «1» Рис. 13 13 Существует целый ряд параллельных регистров: 555ИР15, ИР22, ИР23, ИР27 и других, описанных в [1] - [4]. Задания Используя изученные ранее ИМС D-триггеров и ЛЭ, построить различные типы параллельных регистров с различными комбинациями входов: сброс (прямой и инверсный), CS (прямой и инверсный), с использованием статических и динамических триггеров и т. д. Последовательный регистр Последовательный или сдвиговый регистр (shift register) – это регистр, содержимое которого может сдвигаться в сторону младших или старших разрядов. В качестве примера рассмотрим 4-разрядный сдвиговый регистр 564ИР2, структурная схема и условное обозначение которого показаны на рис. 14 (ИМС 564ИР2 содержит два изображенных регистра). D C R D C R T D C R T D C R T D C R T D0 D C RG R D1 0 1 2 3 Рис. 14 D2 D3 D2 D1 D0 D D3 Из схемы видно, что выход каждого триггера соединяется со входом D последующего. Входной разряд данных подается на вход D 1-го триггера. В момент 14 переднего фронта сигнала С состояние входа D записывается в 1-й триггер, состояние 1-го – во 2-й, 2-го – в 3-й и т. д. Т. о., каждый раз с приходом фронта синхросигнала С значение регистра сдвигается на 1 разряд влево. При этом в младший разряд записывается значение входа D, старший разряд – теряется. Если на входе D лог. «0», то в каждом такте происходит умножение содержимого регистра на 2, за n тактов значение регистра умножается на 2n. Таблица истинности 564ИР2 приведена в [3]. Аналогично можно построить сдвиговый регистр для сдвига вправо. При этом за n тактов происходит деление на 2n. Существуют регистры, которые могут производить сдвиг как вправо, так и влево (555ИР8). В вычислительной технике распространенной является передача информации в последовательном коде. В этом случае сдвиговый регистр может использоваться для преобразования последовательного кода в параллельный. Задания Построить самостоятельно 4-разрядный регистр, производящий сдвиг влево. Более сложное задание: построить регистр, который, в зависимости от управляющего разряда V, будет производить сдвиг вправо или влево. Можно ли использовать рассмотренный регистр 564ИР2 для сдвига вправо? Должны ли триггеры в сдвиговом регистре быть обязательно непрозрачными или возможно применение любых? Универсальный регистр В настоящее время промышленностью выпускается большое число разнообразных регистров, сочетающих в себе возможности как параллельного, так и последовательного регистров [1], [3]. В качестве примера рассмотрим универсальный сдвиговый регистр с последовательно-параллельным вводом и параллельным выводом информации 555ИР11. Условное обозначение его и упрощенная таблица истинности (полная информация и структурная схема приведены в [3]) показаны на рис. 15. Режим работы регистра зависит от управляющего кода S0, S1. Изменение информации на выходах происходит по переднему фронту сигнала С. При S0 = S1 = 0 информация в регистре не изменяется. 15 При S0 = S1 = 1 ИМС работает в режиме параллельной записи, состояния входов DR и DL - безразличны. При S0 = 0, S1 = 1 регистр работает в режиме «сдвиг влево». В младший разряд записывается состояние входа DL. При S0 = 1, S1 = 0 регистр работает в режиме «сдвиг вправо». В старший разряд записывается состояние входа DR. Примерно так же работает 555ИР16. DL RG 0 1 2 3 DR 3 0 1 2 DR 3 C S0 S1 R 0 1 1 1 1 S0 Х 0 1 0 1 Сдвиг вправо 2 1 0 Сдвиг влево S1 Х 0 1 1 0 C Х Х DL Режим работы Сброс Хранение Параллельная запись Сдвиг влево Сдвиг вправо R Рис. 15 0.0 1.0 2.0 3.0 MS 0.1 1.1 2.1 3.1 16 SE C Рис. 16 0 Регистры часто входят в состав других устройств на ИМС. Например, на рис. 16 изображена ИМС 555КП13 – 1 четыре мультиплексора 2х1 с запоминанием. Логика работы ее 2 очевидна: 3 по заднему фронту сигнала разрядный код запоминается в регистре. С выходной 4- Другим примером является 555ИР30 – дешифратор 3х8 с регистром на выходе. Регистры входят в состав и других ИМС: сумматоров, шинных драйверов и др. [1], [3]. Глава 3. Счетчики Счётчиками называются цифровые автоматы, предназначенные для счёта импульсов. Счётчик имеет счётный вход, на который поступает последовательность импульсов, и n выходов, на которые он выдаёт код, соответствующий количеству поступивших на вход импульсов. При поступлении импульса на вход, выходной код изменяется на единицу. В случае, если выходной код увеличивается на 1, счётчик называется суммирующим или счётчиком прямого счёта. Если же наоборот, код уменьшается на 1, то счётчик называется счетчиком обратного счёта. Число состояний счётчика называется модулем пересчёта k или ёмкостью счётчика. Для двоичного n-разрядного счётчика k = 2n . Счётчик строится на основе T–триггеров (т. е. на основе динамических D–триггеров или JK-триггеров). Для установки в исходное (нулевое) состояние счётчик имеет вход сброса R. Асинхронный счетчик с последовательным переносом Пример структурной схемы, обозначения и временной диаграммы 3-разрядного суммирующего счётчика показан на рис. 17а и 17б соответственно. 17 +1 T R R Q1 T +1 T R Q2 T 1 2 4 Рис. 17а R T Cт Q3 T R 0 |1 |2 |3 |4 | 5 |6 |7 |0 |1 | +1 Q1 Q2 Рис. 17б. Q3 При наличии активного уровня (в данном случае «1») на входе R счётчик сбрасывается, т. е. все входы устанавливаются в 0. Для 3-разрядного счётчика k = 23 = 8. Через каждые 8 импульсов состояния счётчика повторяется. Из временной диаграммы легко видеть, что код на выходе счётчика соответствует числу импульсов, поступивших на вход. Например, после переднего фронта 3-го импульса, состояние выходов Q1 = 1, Q2 = 1, Q3 = 0, что соответствует десятичному числу 3 (011). При поступлении на вход сигнала с частотой f на выходах Q1, Q2, Q3 присутствуют сигналы с частотами f/2, f/4, f/8, т. е. счётчик можно использовать в качестве делителя частоты. 18 Структурная схема и временная диаграмма вычитающего двоичного счётчика изображены на рис. 18а и 18б соответственно. Схема отличается только тем, что на входы триггеров подаётся сигнал с прямого, а не с инверсного выхода предыдущего триггера. -1 T R Q1 T R -1 T R Q2 T Cт 1 2 4 Рис. 18а R T Q3 T R 0 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | 7 | 6 -1 Инт егральные Q1 микросхем Q2 ы счетчиков обозначаю Рис. 18б Q3 тся буквами ИЕ и практически всегда имеют 4 разряда, т. е. k = 16. Примером может являться ИМС 555ИЕ19 +1 R Ст 1 2 4 8 Рис. 19 (рис. 19) , включающая 2 изображенных счетчика. Задания Можно ли построить вычитающий (суммирующий) счетчик, имея в наличии только ИМС суммирующего (вычитающего) счетчика и ЛЭ? Как будут работать схемы счетчиков на рис. 17а и 18а, если в них использовать триггеры, срабатывающие по заднему фронту? Постройте соответствующие временные диаграммы. 19 Построить счетчик, используя схему инкрементора и параллельный регистр. Увеличение разрядности счётчиков Как правило, когда k >16, необходимо иметь способ наращивания счётчиков, т. е. увеличения разрядности. Для этой цели счётчик имеет выход CR (англ. сarry нести), называемый выходом переноса для суммирующего счётчика или заём – BR (borrow - занимать) для вычитающего счётчика. Сигнал на выходе CR появляется обычно в момент окончания цикла счёта, т. е. для 4-разрядного счётчика между состояниями 15 и 0 (см. рис. 20). Для вычитающего счетчика сигнал BR возникает между состояниями 0 и 15 (см. рис. 21). 13 | 14 | 15 | 0 |1 +1 -1 Q1 Q1 Q2 Q2 Q3 Q3 Q4 Q4 CR ВR 2 |1 R +1 R Ст | 15 | 14 Рис. 21 Рис. 20 +1 |0 CR 1 2 4 8 +1 Ст R CR 1 2 4 8 Рис. 22 Для получения счетчика с большим числом разрядов выход переноса (заема) подается на тактовый вход следующего счетчика как показано на рис. 22. Так можно увеличивать число разрядов до любого значения. 20 Для корректной работы схемы необходимо, чтобы фронт сигнала CR (BR) совпадал с фронтом, по которому срабатывает счетчик и должен появляться в момент перехода из 15 в 0 для суммирующего (4-разрядного) счетчика и в момент перехода из 0 в 15 для вычитающего (4-разрядного) счетчика. В данном случае (рис. 20-22) выход переноса инверсный, т. к. счетчик срабатывает по переднему фронту. Реверсивные счётчики Реверсивными изменяться. называются Реверсивный счётчик счётчики, может направление работать и счёта как которых суммирующий, может и как вычитающий. Как правило, существуют два тина реализации управления реверсивными счётчиками: 1) Существует один счётный вход 1 (или С) и один вход управления направлением счёта V. Если V = 0, то счётчик работает как суммирующий, а, если V = 1 - как вычитающий (условное обозначение показано на рис. 23). 1 +1 V -1 Рис. 23 Рис. 24 2) Имеются два счётных входа: +1 и –1 (см. рис. 24). В зависимости от того, на какой вход поступают импульсы, счётчик считает вверх или вниз. Асинхронный счетчик с параллельным переносом Все рассмотренные выше счетчики (рис. 17, 18) являются асинхронными счетчиками с последовательным переносом. Недостатком таких счетчиков является большое время задержки, т. к. все триггеры переключаются последовательно. Если время задержки одного триггера равно , то для n-разрядного асинхронного счетчика с последовательным переносом время задержки tзд = n, т. е. задержка растет пропорционально числу разрядов. 21 Т1 +1 Пример реализации 3-разрядQ1 Т Т ного асинхронного счетчика с параллельным переносом приведен на рис. 25, временная диаграмма – 1 Т2 на рис. 26. Проанализировав схему Q2 Т Т и временную диаграмму, легко видеть, что в данной схеме tзд = 1 Т3 tздЛЭ + , Q3 Т Т т. е. время задержки не зависит от числа разрядов. Рис. 25 0 1 2 3 4 5 +1 Q1 Q1 T2 Q2 Q2 T3 Q3 Т1 +1 & & Т2 Т3 Т Рис. Т 26 Q1 Т Т Q2 Т Т Q3 22 Рис. 27 6 7 0 1 Другой вариант схемы (каждый триггер переключается по заднему фронту) изображен на рис. 27, а временная диаграмма – на рис. 28. При необходимости увеличения разрядности используется параллельный перенос между разрядами внутри одной ИМС и последовательный перенос между группами разрядов, т. е. между отдельными микросхемами. Сигнал CR (BR) формируется так же, как и в счетчике с последовательным переносом (подробнее – см. далее). 0 1 2 3 4 5 6 7 0 1 +1 Q1 T2 Q2 T3 Q3 Рис. 28 Задания Построить самостоятельно схемы 3-разрядных вычитающих асинхронных счетчиков с параллельным переносом и их временные диаграммы для случаев, когда триггеры срабатывают по переднему либо по заднему фронту. Синхронный счетчик с параллельным переносом 23 T1 СЕ J T K +1 На рис. 29 приведен пример Q1 C 3-разрядного суммирующего синхронного счетчика. T2 & построения J T K В Q2 синхронном используются счетчике синхронные Т- триггеры на базе JK-триггеров. В C счетчиках такого типа используется параллельный & T3 J T K перенос как между разрядами, так и между группами Q3 разрядов, т. е. между отдельными ИМС. C Данный счетчик имеет вход СЕ (count enable – разрешение счета). & Из схемы легко видеть, что, если CR СЕ = 0, то счет запрещен, т. к. на Рис. 29 всех входах J и K присутствуют лог. нули. Микросхемы основном, в счетчиков, сериях КМОП. построенные Примером по может данному являться принципу, ИМС имеются, 564ИЕ11. в При необходимости увеличения разрядности, выход переноса CR соединяется со входом СЕ следующей ИМС как показано на рис. 30. 24 С +1 Cт 1 2 4 8 1 2 3 …. 15 +1 «1» CE CR CR С Cт CE 1 2 4 8 CR Рис. 30 Задания Построить самостоятельно временную диаграмму работы синхронного счетчика, изображенного на рис. 29. Построить схему и временную диаграмму для аналогичного вычитающего счетчика. Как изменится работа этих схем, если использовать триггеры, переключающиеся по заднему фронту? Как можно объяснить, что ИМС синхронных счетчиков наиболее распространены именно в сериях, выполненных по технологии КМОП? Счетчик с произвольным коэффициентом счёта Часто встречаются задачи, в которых необходимо иметь возможность деления частоты на число, не кратное 2n , (например на 10). 25 Для решения этой задачи используется логическая схема, дешифрующая нужное значение коэффициента деления и сбрасывающая счётчик не после окончания цикла счёта, а раньше. Например, изображенный на рис. 31 3-разрядный счётчик осуществляет деление частоты на 8 (k = 8). В случае, если нам необходимо делить входную частоту, например, на 5, мы создаём схему, которая будет сбрасывать счётчик, как только он достигнет состояния 5. Код счётчика будет изменяться так: 0 – 1 – 2 – 3 – 4 – 0 – 1 и т. д. f Ст +1 R 1 2 4 Дешифратор кода К f/K Рис. 31 Можно использовать стандартную ИМС дешифратора, подавая на вход R сигнал с соответствующего выхода, или строить логическую схему для дешифрации кода К. Рассмотрим пример. Пусть необходимо разделить частоту на 3 (см. схему на рис. 32 и временную диаграмму на рис. 33). f +1 Ст R & 1 2 4 f/3 Рис. 32 0 1 2 3 0 1 f Q1 Q2 R Рис. 33 Элемент И реализует дешифрацию состояния «3». Как только состояние на выходе счетчика станет равным: Q1 = Q2 = 1, с некоторой задержкой на выходе элемента И появится «1», которая по цепи обратной связи подается на вход R, сбрасывая счетчик в состояние «0». Как только счетчик 26 будет сброшен, состояние Q1 = Q2 = 0 через ЛЭ И с некоторой задержкой установит R = 0. Время задержки определяется задержкой в используемых микросхемах. Проанализировав схему и временную диаграмму, легко видеть, что частота на выходе Q2 и на выходе элемента И равна f/3. Описанная схема, в принципе может применяться, но имеет определенные недостатки. При переходных процессах во время переключения счетчика возможно кратковременное возникновение кода 3, что приведет к сбоям, т. е. преждевременному сбросу счетчика. Кроме того, длительность импульса на входе R может оказаться слишком малой, меньше допустимого паспортного значения для данного типа ИМС. Задания Построить схемы деления частоты на произвольное число (например 5, 7), используя ИМС дешифраторов, а также с использованием кодового компаратора. Постройте аналогичные схемы, если используется вычитающий счетчик. Счётчик с предварительной установкой Такой счётчик кроме обычных входов имеет n входов D, на которые подаётся код предварительной установки. Кроме них имеется вход записи C. Такой счётчика можно предварительно установить не только в нулевое состояние по входу R, а в любое заданное состояние. На входе счетчика имеется параллельный регистр, в который можно записывать любой код. Примером такой ИМС является очень распространенный 4-разрядный реверсивный счетчик 555ИЕ7 (см. рис. 34) – асинхронный счетчик с параллельным переносом. Схема и временные диаграммы его приведены в [3]. При С = 0 счетчик находится в состоянии предварительной установки и 4разрядный код на входах D записывается на выход независимо от состояния входов R, +1 СТ CR E-1 BR -1 E+1 1 2 4 8 +1, -1. Счет в этом случае невозможен. При С = 1, R = 1 счетчик сбрасывается, т. е. устанавливается в «0». Счет возможен только в случае C = 1, 1 2 R = 0. При этом разрешением счета по входу «+1» является наличие лог. «1» на входе «-1» и наоборот. 4 8 C R Рис. 34 27 C 0 1 1 1 1 1 R X 1 0 0 0 0 D Dn X X X X X +1 X X 1 0 Схемы +1 Q1 Q2 Q3 Q4 1 CR -1 Q1 Q2 Q3 Q4 -1 X X 1 0 Qn+1 Dn – запись 0 – сброс +1– увеличение кода на 1 Qn – хранение -1– уменьшение кода на 1 Qn - хранение формирования сигналов переноса CR и BR показаны на рис. 1 BR 35, временные диаграммы соответствуют изображенным на рис. 20, 21. Рис. 35 Задания Верно ли утверждение: если на входе R будет присутствовать лог. «1» или на входе С лог. «0», то на выходах CR и BR всегда будет «1»? Счетчик с предварительной установкой наиболее удобен для деления частоты на произвольный код. Один из вариантов схемы приведен на рис. 36, а временная диаграмма – на рис. 37. В качестве примера выбрана схема деления на N = 5. На входы D предварительной установки счетчика код N (в данном случае - 0101). Выход CR подается на вход записи С. Т. о., как только счетчик достигает состояния «0», сигнал появляющийся на выходе BR, поступая на вход С, устанавливает счетчик в состояние «5». 28 +1 СТ CR E-1 BR «1» f 1 2 4 8 «0» Правильное и точное понимание работы данной схемы требует внимания. -1 E+1 «1» f/5 1 Повторите логику формирования сигналов 2 переноса. Импульс на выходе BR будет очень f/5 4 8 коротким определяется и длительность задержкой его счетчика аналогично схеме на рис. 32. C «0» R Рис. 36 3 2 1 0 5 4 3 2 1 0 5 -1 1 2 4 C/BR Рис. 37 Данная схема имеет тот же недостаток, что и схема на рис. 32 – малую длительность импульса BR/C. Кроме того, неудобством является наличие двух состояний счетчика (в данном случае «0» и «5») в течение одного такта. Поэтому такая схема используется только для деления частоты, т. е. в случае, когда сам выходной код не используется. Задания Проанализируйте внимательно временную диаграмму на рис. 37. Определите точную последовательность появления фронтов всех сигналов. Как построить аналогичную схему, используя суммирующий счетчик? Постройте схему для деления на 5. Какая из схем удобнее и почему? 29 Постройте схемы для деления частоты на число, большее 16, т. е. с использованием нескольких ИМС счетчиков. Как будет работать схема на рис. 36, если задать код деления, равный 0? Другой вариант схемы приведен на рис. 38, временная диаграмма – на рис. 39. На входы предварительной установки подан тот же код N = 5. В схему добавлен триггер, благодаря которому сигнал С счетчика появляется синхронно с окончанием импульса BR (см. временную диаграмму). Как S «1» f «1» «0» «1» «0» 1 2 4 8 1 2 C R Рис. 38 -1 BR C Рис. 39 30 из цикл счета повторяется через (N+1) «0» C D «1» R состояние состояние (т. к. добавляется «0»). Т. выходная частота определяется по формуле: 4 8 «0» видно диаграммы, +1 СТ CR E-1 BR -1 E+1 T fвых = f / (N+1) о. Список литературы 1. Пухальский Г. И., Новосельцева Т. Я. Цифровые устройства: Учебное пособие для втузов.- СПб.: Политехника, 1996. 2. Потемкин И. С. Функциональные узлы цифровой автоматики.- М.: Энергоатомиздат,1988. 3. Цифровые интегральные микросхемы: Справочник/ П. П. Мальцев, Н. С. Долидзе, М. И. Критенко и др. – М.: Радио и связь, 1994. 4. Ямпольский В. С. Основы автоматики и электронно-вычислительной техники. – М.: Просвещение, 1991. 31