Подсистема прерываний и программируемого таймера

реклама

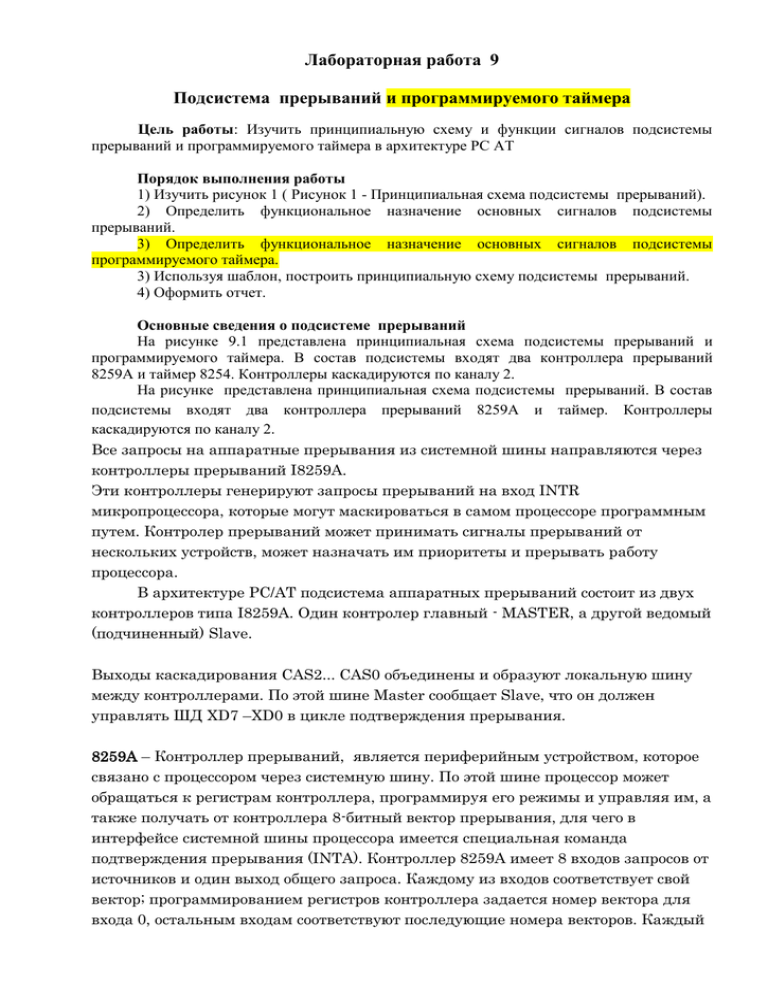

Лабораторная работа 9 Подсистема прерываний и программируемого таймера Цель работы: Изучить принципиальную схему и функции сигналов подсистемы прерываний и программируемого таймера в архитектуре PC AT Порядок выполнения работы 1) Изучить рисунок 1 ( Рисунок 1 - Принципиальная схема подсистемы прерываний). 2) Определить функциональное назначение основных сигналов подсистемы прерываний. 3) Определить функциональное назначение основных сигналов подсистемы программируемого таймера. 3) Используя шаблон, построить принципиальную схему подсистемы прерываний. 4) Оформить отчет. Основные сведения о подсистеме прерываний На рисунке 9.1 представлена принципиальная схема подсистемы прерываний и программируемого таймера. В состав подсистемы входят два контроллера прерываний 8259А и таймер 8254. Контроллеры каскадируются по каналу 2. На рисунке представлена принципиальная схема подсистемы прерываний. В состав подсистемы входят два контроллера прерываний 8259А и таймер. Контроллеры каскадируются по каналу 2. Все запросы на аппаратные прерывания из системной шины направляются через контроллеры прерываний I8259А. Эти контроллеры генерируют запросы прерываний на вход INTR микропроцессора, которые могут маскироваться в самом процессоре программным путем. Контролер прерываний может принимать сигналы прерываний от нескольких устройств, может назначать им приоритеты и прерывать работу процессора. В архитектуре PC/AT подсистема аппаратных прерываний состоит из двух контроллеров типа I8259А. Один контролер главный - MASTER, а другой ведомый (подчиненный) Slave. Выходы каскадирования CAS2... CAS0 объединены и образуют локальную шину между контроллерами. По этой шине Master сообщает Slave, что он должен управлять ШД XD7 –XD0 в цикле подтверждения прерывания. 8259A – Контроллер прерываний, является периферийным устройством, которое связано с процессором через системную шину. По этой шине процессор может обращаться к регистрам контроллера, программируя его режимы и управляя им, а также получать от контроллера 8-битный вектор прерывания, для чего в интерфейсе системной шины процессора имеется специальная команда подтверждения прерывания (INTA). Контроллер 8259A имеет 8 входов запросов от источников и один выход общего запроса. Каждому из входов соответствует свой вектор; программированием регистров контроллера задается номер вектора для входа 0, остальным входам соответствуют последующие номера векторов. Каждый вход может быть программно замаскирован — тогда он не будет вызывать сигнал общего запроса. Контроллер занимает два адреса в пространстве ввода/вывода, программное обращение по этим адресам обеспечивает выполнение следующих функций: управление режимами работы контроллера; управление приоритетами и масками запросов; идентификацию запросов прерывания без вырабатывания общего запроса — обслуживание прерываний по опросу (полинг). В контроллере имеется три регистра: IRR, IMR и ISR. С каждым входом запроса в контроллере связано по одному биту каждого из этих регистров; бит 0 каждого из этих регистров относится к входу 0, бит 1 — к входу 1, бит 7 — ко входу 7. Регистры имеют следующие назначения: IRR (Interrupt Request Register) — регистр запросов прерываний, в котором бит устанавливается при обнаружении сигнала прерывания на соответствующем входе, независимо от маски; IMR (Interrupt Mask Register) — регистр масок прерываний. Единичное значение бита означает замаскированность данного входа — по запросу с замаскированного входа общий запрос прерывания не генерируется; ISR (Interrupt Service Register) — регистр обслуживаемого прерывания. Во время цикла подтверждения (INTA) в регистре устанавливается бит, соответствующий наиболее приоритетному запросу и, соответственно, формируемому вектору прерывания. В этот же момент обнуляется соответствующий бит запроса в регистре IRR. Бит в ISR обнуляется по получении контроллером команды EOI, а в режиме автоматического подтверждения (по команде AEOI) он обнуляется сразу после передачи вектора прерывания. 8254-2 – системный таймер. Программируемый таймер предназначен для получения программноуправляемых временных задержек и генерации времязадающих функций. Таймер позволяет повысить эффективность программирования процессов управления и синхронизации внешних устройств, особенно в реальном масштабе времени. Таймер содержит 3 независимых канала, каждый из которых может быть запрограммирован в одном из 6 режимов. На каждый канал могут подаваться входные синхросигналы, а на выходе будет получен сигнал, частота которого равна частоте входного сигнала деленной на произвольное 16-разрядное число. В PC/AT для всех 3 каналов синхросигналы поступают от единого источника с частотой 1,19 Мгц. Выход канала 1 OUT1 генерирует сигнал запроса регенерации динамической памяти, используя при этом режим “импульсный генератор частоты”. Выход канала 2 OUT2 генерирует тональный сигнал для динамика, используя режим “генератор прямоугольных импульсов”. SN75477 – Два нижних ключа с открытыми коллекторами и логическим управлением (ИНЕ). Микросхема предназначена äëÿ использования в системах, требующих высокого уровня напряжения, è высокого быстродействия. Эòо усòроéсòâо èìåеò диодные âхîäû и предназначенные для эксплуатации при больших токах, высоковольтные диоды Шотки íà выходных сигналах äëÿ èíäуêòèâíîé ïåрехоäíîé çàùèòû. Таблица истинности Входы A H L X S H X L Выход Y L H H F08 – Четыре логических элемента 2И. Отечественный аналог 1531ЛИ1. Микросхема содержит четыре идентичных логических элемента со стандартными активными выходами, выполняющих Булевы функции Y=D1*D2 или Y D1 D 2 в положительной логике. Таблица истинности D1 D2 Y H H H L H L H L L L L L Внешние сигналы: Источники прерываний: IRQ0 - системный таймер; IRQ1 – клавиатура; IRQ3 - последовательный интерфейс RS232С вторичный; IRQ4 - последовательный интерфейс RS232С первичный; IRQ5 – параллельный порт вторичный; RQ6 – НГМД; IRQ7 – параллельный порт первичный; IRQ 8 - часы реального времени; IRQ9–IRQ12 – резерв; IRQ13 - ошибка сопроцессора; IRQ14 – накопитель на жестких магнитных дисках (НЖМД); IRQ15 - резерв. Функциональное назначение линий: XD0 - XD7 - двунаправленная ШД; INTA - входной сигнал подтверждения прерывания; INTR - выходной сигнал, используемый для прерывания процессора; RW - сигналы чтения /записи; XA0 - XA1 - адресные линии для считывания внутренних регистров контроллера; CAS0 - СAS2 - двунаправленная шина каскадирования для объединения контролеров в каскадном режиме; SP - в подсистеме PC/AT используется в качестве входа, определяющего Master или Slave контроллеров. OPT BUF FULL – индикатор переполнения буфера T/C – Сигнал (Terminal Count - Окончание счета) разрешается контроллером ПДП т тогда, когда по какому-либо из каналов ПДП будет окончен счет числа пересылок данных, то есть все пересылки данных выполнены +5V – питание. Содержание отчета 1) Цель работы 2) Принципиальная схема подсистемы прерываний 3) Назначение основных сигналов подсистемы прерываний Тестовые вопросы 1) Схемная земля а) OSC b)CS 2) Сигнал VCC а) прерывание с) GND b)питание d) DCS с) сигнал ошибки d) сигнал записи 3) Входы передают запросы на аппаратное прерывание процессора для выполнения какого-либо обслуживания. а) DASK0- DASK7 b)IRQ3-IRQ15 с) SA0-SA7 d) SD0-SD7 4) Подчинение программе \ разрешение буфера а) T/C b)CS с) SP/EN d) DCS 5) Каким количеством связей объединены элементы 8259А Master и Slave а) 2 b)8 с) 6 d) 4 6) Сигнал маскируемого прерывания а) INTA b) INTR с) IO d) IRQ 7) Вход подключения тактового генератора а) BUSY b) CLK с) PPI d) CS 8) Сигнал CE а) выбор кристалла b) вход управления с) разрешение выходов d) чтение в порт Рисунок 9.1 – Принципиальная схема подсистемы прерываний и программируемого таймера Шаблон: