sch_exam_v2x

реклама

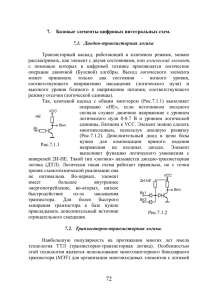

1. Логический элемент, простейшее устройство ЭВМ, выполняющее одну определённую логическую операцию над входными сигналами согласно правилам алгебры логики. Любые цифровые микросхемы строятся на основе простейших логических элементов: "НЕ" - выполняет функцию инвертирования; "И" - выполняет функцию логического умножения. "ИЛИ" - выполняет функцию логического суммирования Чаще всего в реальных логических схемах имеется несколько входов для приёма нескольких сигналов. Выход логического элемента зависит от состояния входа (входов) и выполняемой им (ими) логической функции. Функции логического элемента обычно описываются так называемой таблицей истинности. В таблице истинности представляются все возможные комбинации условий на входе, выраженных состояниями логического уровня («высокий» или «низкий», «1» или «0», для каждого входа логической схемы), вместе с соответствующим логическим уровнем на выходе («высокий» или «низкий»). 2. Функциональная схема – это схема соединения логических элементов, реализующая логическую функцию. Система простых логических функций, на основе которой можно получить любую логическую функцию, называется функционально полной. 3. 4. 5.Входная характеристика IВХ = f (UBX)— зависимость входного тока ЛЭ от входного напряжения определяет нагрузочную способность ЛЭ и режим работы линий связи. На рис. 2.3, 2.4 приведены типовые входные характеристики логических элементов ИС ЭСЛ и ТТЛ. На входной характеристике ЛЭ ЭСЛ можно выделить следующие зоны, соответствующие возможным режимам работы входной цепи ЛЭ: I, V — зоны, определяющие рабочие режимы ЛЭ, т. е. входные токи при входных напряжениях низкого и высокого уровней, при . которых входные цепи имеют большое входное сопротивление (точки А и В соответствуют нижнему и верхнему уровням напряжений ЛЭ серии К500); II и IV — зоны статической помехоустойчивости; III —зона переключения ЛЭ (опорное напряжение UОП , определяемое как среднее напряжение между высоким и низким уровнями, для ЛЭ ЭСЛ серии К500 составляет примерно — 1.3 В; зона UВ UН ограничивается пороговыми напряжениями ВХ ПОР и ВХ ПОР ); VI — зона нерабочих режимов (UВХ НАС — напряжение насыщения входного транзистора — при увеличении входного напряжения входной ток резко увеличивается). Рис. 2.3. Типовая входная характеристика ЛЭ ЭСЛ На входной характеристике ЛЭ ТТЛ (см. рис. 2.4) можно выделить следующие зоны: I, IX — зоны недопустимых входных напряжений; II.VIII— зоны предельно допустимых входных напряжений, оговоренных в технических условиях; III, VII — зоны, определяющие рабочий режим ЛЭ; наиболее характерный режим при напряжении низкого уровня («0») — точка А, при напряжении верхнего уровня — точка В; IV, VI — зоны допустимых статических помех; V — зона переключения. 6.Выходная характеристика UВЫХ = f (IВЫХ) — зависимость выходного напряжения ЛЭ от выходного тока нагрузки. Эта характеристика в совокупности с входной позволяет определить нагрузочную способность ЛЭ, режим его работы и способ согласования переходных процессов в линиях связи. Так как в каждом из двух состояний ЛЭ в активном режиме находятся различные компоненты схемы, то различают UН UВ выходные характеристики по нижнему ВЫХ и по верхнему ВЫХ уровням выходного напряжения. Точка В на графике выходной характеристики ИС ЭСЛ (рис. 2.5) расположена в рабочей зоне верхнего логического уровня, точка А — в зоне нижнего уровня. Для определения рабочих точек А и В на выходную характеристику накладывают нагрузочные характеристики (RH). Рабочие зоны выходных характеристик по верхнему и по нижнему уровням напряжения ЛЭ ТТЛ (рис. 2.6), как и ЛЭ ЭСЛ, ограничены выходными пороговыми напряжениями и допустимыми уровнями напряжений. Статическому состоянию выходного верхнего уровня при малой нагрузке соответствует точка В. Точка А, находящаяся на пересечении выходной характеристики нижнего уровня управляющего ЛЭ с входной характеристикой управляемого ЛЭ, определяет статическое состояние нижнего уровня. Входные и выходные характеристики ЛЭ ТТЛ могут использоваться для оценки уровня помех, возникающих в линиях связи при переключении ЛЭ. В частности, для оценки отражений в длинных линиях связи используют также нагрузочную характеристику линии связи. Рис. 2.4. Типовая входная характеристика ЛЭ ТТЛ Рис. 2.5. Типовая выходная характеристика ЛЭ ЭСЛ Рис. 2.6. Типовая выходная характеристика ЛЭ ТТЛ 7. Нагрузочная способность Нагрузочная способность -характеризует способность логического элемента получить сигнал от нескольких источников информации и одновременно быть источником информации для ряда других элементов. Для численной характеристики используют: - коэффициент разветвления по выходу Краз= максимальному числу входов однотипных логических элементов, которые могут быть подключены к выходу данного логического элемента, не вызывая при этом искажений формы и амплитуды его сигнала , выходящих за границы зон отображения уровней логического 0 и логической 1. Типовые значения Краз= 2,…8 . М..б. ИМС с повышенной нагрузочной способностью Краз=20,….30 . - коэффициент объединения по входу Коб= максимальному числу выходов однотипных логических элементов, которые могут быть подключены по входу данного логического элемента, не вызывая при этом искажений формы и амплитуды его сигнала, выходящих за границы зон отображения уровней логического 0 и логической 1. Коэффициент разветвления — число входов, которое может быть подключено к данному выходу без нарушения работы. Определяется отношением выходного тока к входному. Стандартная величина коэффициента разветвления при использовании микросхем одного типа (одной серии) равна 10. Нагрузочная способность — параметр выхода, характеризующий величину выходного тока, которую может выдать в нагрузку данный выход без нарушения работы. Чаще всего нагрузочная способность прямо связана с коэффициентом разветвления. 8,9. Амплитудная передаточная характеристика UВЫХ = f(UBX) определяет формирующие свойства ЛЭ, его помехоустойчивость, амплитуду и уровни стандартного сигнала. Вид характеристики зависит от типа логического элемента (ЭСЛ, ТТЛ) и может изменяться в определенных пределах в зависимости от разброса параметров схем, изменений напряжения питания, нагрузки, температуры окружающей среды. Рассмотрим типовую амплитудную передаточную характеристику (АПХ) инвертирующего ЛЭ (рис. 2.1). В статическом состоянии выходной сигнал ЛЭ может находиться либо на верхнем (UB), либо на нижнем (UH) уровне напряжения. Асимптотический верхний (т. В) и асимптотический нижний (т. А) уровни логических сигналов находятся как точки пересечения АПХ (кривая 1) с ее зеркальным отображением (кривая 2) относительно прямой единичного усиления UВЫХ = UВ U Н ВХ является логическим перепадом UЛ выходных уровней ЛЭ. На практике из-за влияния помех UВХ. Разность ВЫХ и разбросов амплитудных передаточных характеристик для каждого типа ЛЭ устанавливается минимальный логический U UВ UН UВ и UН ВЫХ ПОР ВЫХ ПОР , где ВЫХ ПОР ВЫХ ПОР - соответственно верхний и нижний уровни перепад: Л min выходного порогового напряжения. Выходные пороговые напряжения находят с помощью пороговых точек b и а на характеристике, в которых дифференциальный коэффициент усиления по напряжению KU=-1. UН Зоны статической помехоустойчивости ЛЭ по нижнему ( ПОМ )' и верхнему ( комбинационных логических цепях определяются выражениями: Н Н (U ПОМ ) U КВ U ВЫХ ПОР , В В (U ПОМ ) U ВЫХ ПОР U КВ , В U ПОМ )' уровням напряжения в где ( Н U ПОМ )', ( В U ПОМ )' характеризуют максимально допустимые уровни статической помехи на входе ЛЭ в UН UВ ВЫХ ПОР ВЫХ ПОР комбинационных логических цепях; — выходное пороговое напряжение нижнего уровня; выходное пороговое напряжение верхнего уровня. Однако из-за наличия схем с положительной обратной связью в технической документации на все ИС зоны статической помехоустойчивости по входу ограничиваются входными UН UВ ВХ ПОР ВХ ПОР пороговыми напряжениями: — по нижнему уровню и - по верхнему. Эти пороговые напряжения называются соответственно пороговым напряжением зоны переключения (порог зоны переключения) нижнего уровня и пороговым напряжением зоны переключения верхнего уровня. В зоне переключения, заключенной между пороговыми напряжениями, работа ЛЭ в статическом режиме запрещается. Рис. 2.1. Амплитудная передаточная характеристика инвертирующего ЛЭ Рис. 2.2. Разброс амплитудных передаточных характеристик логических элементов Таким образом, статическая помехоустойчивость ЛЭ по нижнему уровню входного сигнала определяется выражением U В ПОМ U Н Н Н U ПОМ U ВХ ПОР U ВЫХ ПОР В ВХ ПОР U а по верхнему уровню входного сигнала — выражением В ВЫХ ПОР . Максимальная помехоустойчивость ЛЭ по нижнему и верхнему уровням достигается при идеальной UН U В U ВХ ПОР КВ амплитудной передаточной характеристике, для которой ВХ ПОР . Реализация характеристик, близких к идеальным, связана с известными трудностями вследствие технологического разброса параметров микросхем при изготовлении, изменения пороговых напряжений в зависимости от изменения напряжения питания и температуры окружающей среды в процессе эксплуатации. Поэтому реально зоны статической помехоустойчивости для каждого типа ЛЭ устанавливают на основании статистического анализа амплитудных передаточных характеристик. На рис. 2.2 заштрихованная область соответствует возможным разбросам амплитудных передаточных характеристик ЛЭ одного типа. При сопоставлении амплитудных передаточных характеристик ЛЭ разных типов часто используют не абсолютные значения статической помехоустойчивости, а их отношение к минимальному логическому перепаду: Н Н В В К ПОМ U ПОМ / U Л , К ПОМ U ПОМ /U Л . Чем ближе амплитудная передаточная характеристика к идеальной, тем ближе значения этих коэффициентов к 0,5. 10. Помехоустойчивость базовых логических элементов оценивают в статическом и динамическом режимах. При этом статическая помехоустойчивость определяется уровнем напряжения, подаваемого на вход элемента относительно уровней логических 0 и 1, при котором состояние на выходе схемы не изменяется. Для элементов ТТЛ статическая помехоустойчивость составляет не менее 0,4 В, а для микросхем серий КМДП не менее 30% напряжения питания. Динамическая помехоустойчивость зависит от формы и амплитуды сигнала помехи, а также от скорости переключения логического элемента и его статической помехоустойчивости. 11. Диодно-транзисторная логика (ДТЛ) — технология построения цифровых схем на основе биполярных транзисторов, диодов и резисторов. Своё название технология получила благодаря реализации логических функций (например, 2И) с помощью диодных цепей, а усиления и инверсии сигнала — с помощью транзистора (для сравнения см. резисторно-транзисторная логика и транзисторно-транзисторная логика). Показанная на рисунке схема представляет собой типичный элемент 2И-НЕ: Если хотя бы на одном из входов уровень логического нуля, то ток течет через R1 и диод во входную цепь. На анодах диодов напряжение 0,7В, которого недостаточно для открывания транзистора. Транзистор закрыт. На выходе формируется уровень логической единицы. Если на все входы поступает уровень логической единицы, ток течет через R1 на базу транзистора, образуя на анодах диодов напряжение 1,4В. Поскольку напряжение уровня логической единицы больше этой величины, входы диодов обратносмещены и не участвуют в работе схемы. Транзистор открыт в режиме насыщения. В транзистор втекает ток нагрузки, по величине значительно больший тока нагрузки в состоянии логической единицы. 12,13. 14. 15. 16. 17. 18. 19. Транзисторно-транзисторная логика (ТТЛ, TTL) — разновидность цифровых логических микросхем, построенных на основе биполярных транзисторов и резисторов. Название транзисторно-транзисторный возникло из-за того, что транзисторы используются как для выполнения логических функций (например, И, ИЛИ), так и для усиления выходного сигнала (в отличие от резисторно-транзисторной и диодно-транзисторной логики). Простейший базовый элемент ТТЛ выполняет логическую операцию И-НЕ, в принципе повторяет структуру ДТЛ микросхем и в то же время за счёт использования многоэмиттерного транзистора, объединяет свойства диода и транзисторного усилителя что позволяет увеличить быстродействие, снизить потребляемую мощность и усовершенствовать технологию изготовления микросхемы. 20. Принцип работы ТТЛ с простым инвертором: Биполярные транзисторы могут работать в четырех режимах: отсечки, нормально активный, инверсно активный и насыщения. В инверсно активном режиме эмиттерный переход закрыт, а коллекторный переход открыт. В инверсном режиме коэффициент усиления транзистора значительно меньше, чем в нормальном режиме, из-за несимметричного конструктивного исполнения переходов база-коллектор и база-эмиттер. При нулевом уровне на любом входе многоэмиттерного транзистора VT1 (на упрощённой схеме — слева) он работает в нормальном режиме и формирует на базе VT2 потенциал близкий к нулю. В этом состоянии неосновные носители из базы VT2 рассасываются не только через коллектор, но и через открытый VT1. Если ноль подаётся на один из входов VT1, то наблюдается максимальный входной ток I=(E-0,7)/R1. В этом случае через другие эмиттерные переходы может наблюдаться паразитный ток. Чтобы он не был слишком велик неиспользуемые входы элемента присоединяются к источнику питания +5В, −5В через резистор с сопротивлением 1кОм, который может работать на 10 входов ТТЛ. Если свободные входы не подключаются ни к чему, то логика работы схемы сохраняется но паразитная ёмкость входных цепей будет уменьшать быстродействие цепи из расчёта 2 нс на 1 вход. Свободные входы могут воспринимать сигнал помехи, который может привести к сбою в работе схемы. Если на все входы поступает уровень логической единицы, то VT1 окажется инверсно-включенным, ток R1 течёт через коллектор VT1 в базу VT2, на выходе формируется нуль. Если резистор R2 не используется, то мы имеем дело с элементом с открытым коллектором, у которого в условном обозначении используется дополнительный символ. Логический элемент 3И-НЕ в серии микросхем 74LS(К555)[1] ТТЛ-логика (как и ТТЛШ) является прямым наследником ДТЛ и использует тот же принцип действия. Входной ТТЛтранзистор (в отличие от обычного) имеет несколько, обычно от 2 до 8, эмиттеров. Эти эмиттеры выполняют роль входных диодов (если сравнивать с ДТЛ). Многоэмиттерный транзистор по сравнению с применявшейся в схемах ДТЛ сборкой из отдельных диодов занимает меньше места на кристалле и обеспечивает более высокое быстродействие. Следует отметить, что в микросхемах ТТЛШ, начиная с серии 74LS, вместо многэмиттерного транзистора используется сборка диодов Шоттки (серия 74LS) или PNP транзисторы в сочетании с диодами Шоттки (серии 74AS, 74ALS), так что фактически произошёл возврат к ДТЛ. Название ТТЛ заслуженно носят лишь серии 74, 74H, 74L, 74S, содержащие многоэмиттерный транзистор. Все более поздние серии многоэмиттерного транзистора не содержат, фактически являются ДТЛ и носят название ТТЛШ (ТТЛ Шоттки) лишь «по традиции», будучи развитием именно ДТЛ. 21,22. Для повышения нагрузочной способности логического элемента вместо простого инвертора большинство элементов ТТЛ имеют сложный инвертор (рис. 2.2,а). Он состоит из фазоразделительного каскада, выполненного на транзисторе VT2, и двухтактного выходного каскада, состоящего из выходных транзисторов: насыщаемого VT5 и составного эмиттерного повторителя VT3 и VT4. Рис. 2.2.а. схема элемента со сложным инвертором Рассмотрим функционирование логического элемента со сложным инвертором. Подадим на вход напряжение низкого уровня, соответствующее логическому нулю (переключатель S1 поставлен в положение Н), тогда многоэмиттерный транзистор VT1 будет находиться в активном режиме (переход база - эмиттер открыт, а переход база - коллектор закрыт), течет большой ток , во входную цепь, а транзисторы VT2, VT5 закрыты (на рис. 2.2.б не показаны VT2, VT5), транзисторы VT3 и VT4 будут открыты, т. к. база VT3 через резистор R2 подключена к шине питания Uи.п.=5 В. Поэтому выходное напряжение, снимаемое с нагрузки, расположенной в эмиттерной цепи VT4, будет иметь высокий уровень, что соответствует логической единице Uвых1. Рис. 2.2.б. распределение токов и напряжений при низком входном уровне Статическое выходное напряжение высокого уровня для логического элемента равно: =Uи.п.-Iвых·R4-Uкэ-2·Uб.э. Так как на транзисторах VT3, VT4 выполнен эмиттерный повторитель, то он не может перейти в состояние насыщения, и напряжение Uкэ VT4 не уменьшается меньше (0.7 .. 1) В, а напряжение Uбэ примерно равно 0,7 В для транзисторов без переходов Шотки. Падением напряжения на резисторе R4, ограничивающем ток в выходном каскаде, когда VT4 и VT5 открыты, можно пренебречь. Тогда получаем >=2,6 В. 23 .