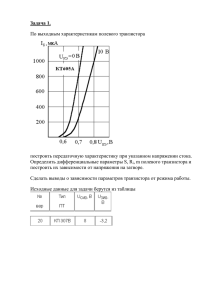

sch_zach

реклама

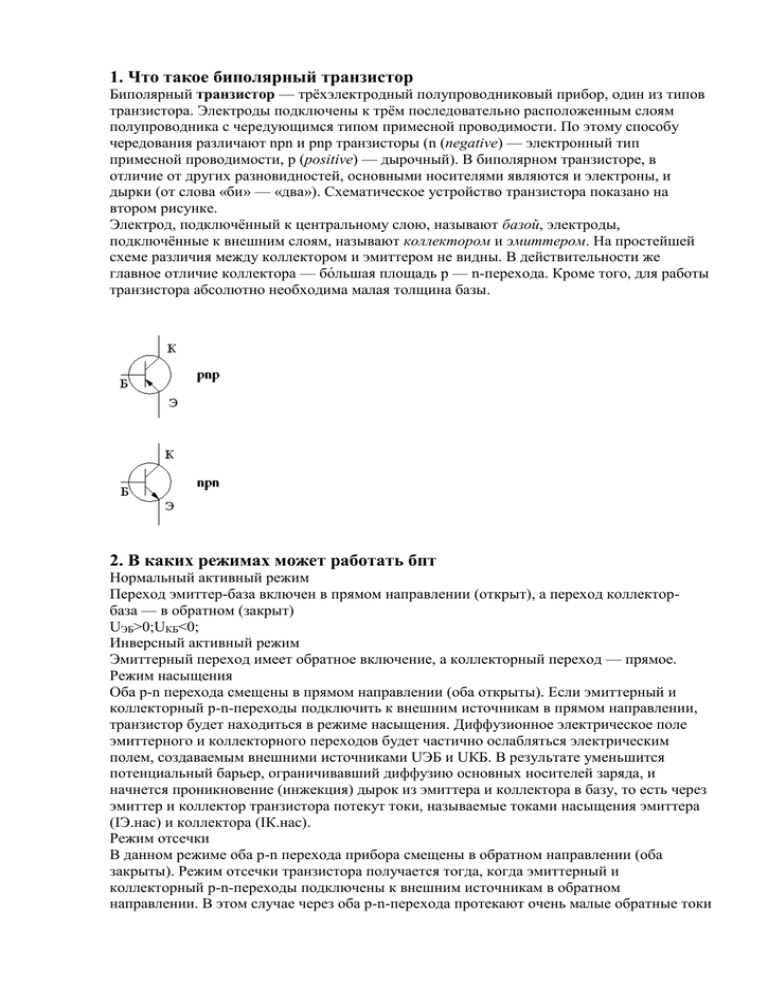

1. Что такое биполярный транзистор Биполярный транзистор — трёхэлектродный полупроводниковый прибор, один из типов транзистора. Электроды подключены к трём последовательно расположенным слоям полупроводника с чередующимся типом примесной проводимости. По этому способу чередования различают npn и pnp транзисторы (n (negative) — электронный тип примесной проводимости, p (positive) — дырочный). В биполярном транзисторе, в отличие от других разновидностей, основными носителями являются и электроны, и дырки (от слова «би» — «два»). Схематическое устройство транзистора показано на втором рисунке. Электрод, подключённый к центральному слою, называют базой, электроды, подключённые к внешним слоям, называют коллектором и эмиттером. На простейшей схеме различия между коллектором и эмиттером не видны. В действительности же главное отличие коллектора — бо́льшая площадь p — n-перехода. Кроме того, для работы транзистора абсолютно необходима малая толщина базы. 2. В каких режимах может работать бпт Нормальный активный режим Переход эмиттер-база включен в прямом направлении (открыт), а переход коллекторбаза — в обратном (закрыт) UЭБ>0;UКБ<0; Инверсный активный режим Эмиттерный переход имеет обратное включение, а коллекторный переход — прямое. Режим насыщения Оба p-n перехода смещены в прямом направлении (оба открыты). Если эмиттерный и коллекторный р-n-переходы подключить к внешним источникам в прямом направлении, транзистор будет находиться в режиме насыщения. Диффузионное электрическое поле эмиттерного и коллекторного переходов будет частично ослабляться электрическим полем, создаваемым внешними источниками UЭБ и UКБ. В результате уменьшится потенциальный барьер, ограничивавший диффузию основных носителей заряда, и начнется проникновение (инжекция) дырок из эмиттера и коллектора в базу, то есть через эмиттер и коллектор транзистора потекут токи, называемые токами насыщения эмиттера (IЭ.нас) и коллектора (IК.нас). Режим отсечки В данном режиме оба p-n перехода прибора смещены в обратном направлении (оба закрыты). Режим отсечки транзистора получается тогда, когда эмиттерный и коллекторный р-n-переходы подключены к внешним источникам в обратном направлении. В этом случае через оба р-n-перехода протекают очень малые обратные токи эмиттера (IЭБО) И коллектора (IКБО). Ток базы равен сумме этих токов и в зависимости от типа транзистора находится в пределах от единиц микроампер — мкА (у кремниевых транзисторов) до единиц миллиампер — мА (у германиевых транзисторов). Барьерный режим В данном режиме база транзистора по постоянному току соединена накоротко или через небольшой резистор с его коллектором, а в коллекторную или в эмиттерную цепь транзистора включается резистор, задающий ток через транзистор. В таком включении транзистор представляет из себя своеобразный диод, включенный последовательно с токозадающим резистором. Подобные схемы каскадов отличаются малым количеством комплектующих, хорошей развязкой по высокой частоте, большим рабочим диапазоном температур, нечувствительностью к параметрам транзисторов. 3. ЛЭ ДТЛ схема и принцип работы с простым инвертором(на одном транзисторе) ДТЛ — диодо-транзисторная логика Логический элемент И - НЕ диодно-транзисторной логики (ДТЛ). Входные сигналы подаются на элемент И, выходной сигнал снимается с элемента НЕ. Таким образом, на выходе элемента И - НЕ сигналом будет логическая 1, если на входе элемента НЕ присутствует сигнал, соответствующий логическому 0. Чтобы это имело место, хотя бы на один вход элемента И должен быть подан сигнал, соответствующий логическому 0. Логический элемент И - НЕ для сигналов положительной полярности показан на рис. 21.4. Он представляет собой соединение через диоды Дс двух элементов: диодного элемента И и транзисторного элемента НЕ. Значения напряжений, соответствующих логическим 0 и 1, необходимо выбрать должным образом, так как при напряжении на базе, несколько меньшем 0,6В, транзистор будет закрыт, а в режиме насыщения напряжение между эмиттером и коллектором равно 0,4 В (и выше). Д1, Д2,Д3 — диоды на входе Дс — диоды связи (для устранения помех на уровне логического нуля) Т — транзистор (биполярный) R1 и Rк — сопротивление для ограничения нагрузки на ЛЭ-ы Если на все входы подано напряжение U1 (логическая 1), все диоды (Д1 Д2, Д3) будут закрыты и ток в цепи «источник E1, резистор R1, открытые диоды Дc» пройдет в базу транзистора. Вследствие падения напряжения на резисторе R1 потенциал φ1 окажется несколько ниже потенциала +E1, диод Д1 будет открыт и потенциал базы φБ транзистора меньше потенциала φ1 на значение падения напряжения на диодах Дc (но выше 0,6В, так что транзистор будет находиться в режиме насыщения). На выходе элемента НЕ установится низкое напряжение U0, соответствующее логическому 0. Если хотя бы на один вход, например Вх1, будет подано напряжение U0, то соответствующий диод Д1 будет открыт и потенциал φ1 будет ≈ U0. Ток от источника E1 будет проходить через резистор R1. Часть тока замкнется через открытый диод Д1; источник U0, источник E1, часть - через смещающие диоды Дc, резистор R2 и источник E1. Потенциал базы φБ = UБЭ будет ниже потенциала φ1 на значение падения напряжения на смещающих диодах Дc. При этом элемент рассчитывают таким образом, чтобы падение напряжения на диодах Дc было таким, чтобы φБ = UБЭ > 0, но значительно меньше 0,6В. В этом случае транзистор будет закрыт и на выходе элемента НЕ напряжение окажется равным EK > U0, т. е. получим логическую 1. 4. ЛЭ ТТЛ схема и принцип работы с простым инвертором(на одном транзисторе) ТТЛ — транзисторно-транзисторная логика Логический элемент И - НЕ транзисторно-транзисторной логики (ТТЛ). Простейший элемент И - НЕ показан на рис. 21.5, а. Он состоит из двух частей: элемента И на многоэмиттерном транзисторе Т1 и элемента НЕ на транзисторе Т2. Связь непосредственная: коллектор Т1 соединен с базой транзистора Т2. Смещение в цепи базы транзистора Т2 выполняет коллекторный переход Т1. Три эмиттерных перехода Т1 подключенных к входу элемента (рис. 21.5,б), выполняют функции входных диодов в схеме И на диодах. По сравнению с ДТЛ-элементами элементы ТТЛ обладают более высоким быстродействием. Элемент выполнен по технологии интегральных микросхем, поэтому он не содержит реактивных элементов. Он работает от сигналов в виде напряжений положительной полярности. Если на все входы подать напряжение U1, то все эмиттерные переходы сместятся в обратном направлении. Потенциал коллектора транзистора Т2 окажется близким нулю, переход база - коллектор смещен в прямом направлении за счет источника +EK. Транзистор T1 будет в инверсном режиме, транзистор Т2 - в режиме насыщения. Коллекторный ток транзистора T1 втекает в базу транзистора Т2, оставляя последний в режиме насыщения. Таким образом, на выходе будет напряжение низкого уровня U0, т. е. логический 0. Если на один из входов подано напряжение U0, то потенциал базы транзистора T1 станет выше потенциалов эмиттера и коллектора, поэтому T1 окажется в режиме насыщения и ток базы замкнется через эмиттерные переходы T1 и не поступит в его коллектор, а следовательно, и в базу T2. Поэтому транзистор T2 будет закрыт, а на его выходе напряжение высокого уровня (логическая 1). Таким образом, элемент выполняет операцию И - НЕ, так как сигнал логического нуля на выходе может быть только тогда, когда на все входы будет подан сигнал логической единицы 5. ЛЭ ТТЛ схема и принцип работы со сложным инвертором Схема ТТЛ со сложным осуществляет логическую операцию И-НЕ. При наличии на входах напряжения лог. «0» многоэмиттерный транзистор VT1 находится в режиме насыщения, а транзистор VT2 закрыт. Следовательно, закрыт и транзистор VT4, поскольку ток через резистор R4 не протекает и напряжение на базе VT4 Uбэ4="0". Транзистор VT3 открыт, так как его база подключена к источнику питания E через резистор R2. Сопротивление резистора R3 невелико, поэтому VT3 работает как эмиттерный повторитель. Через транзистор VT3 и открытый диод VD протекает ток нагрузки логического элемента и выходное напряжение, соответствующее уровню лог. «1», равно напряжению питания за минусом падения напряжения UБЭ.нас, падения напряжения на открытом диоде Uд=UБЭ.нас и небольшого падения напряжения на сопротивлении R2 от тока базы VT2: U¹=E–2UКЭ.нас – R2IБ2 =Un– 2UБЭ.нас. При увеличении напряжения на всех входах потенциал базы VT2 возрастает и при UВХ=U0пор транзистор VT2 открывается, начинает протекать коллекторный ток IK2 через резисторы R2 и R4. В результате базовый ток VT3 уменьшается, падение напряжения на нём увеличивается и выходное напряжение снижается. Пока на резисторе R4 падение напряжения UR4<UБЭ.нас транзистор VT4 закрыт. Когда UВХ=U¹пор=2UБЭ.нас– UКЭ.нас открывается транзистор VT4. Дальнейшее увеличение входного напряжения приводит к насыщению VT2 и VT4 и переходу VT1 в инверсный режим. При этом потенциал точки «а» равен Ua=UБЭ.нас+UКЭ.нас, а точки «б» — Uб=UКЭ.нас, следовательно, Uаб=Uа–Uб=UБЭ.нас. Для отпирания транзистора VT3 и диода VD1 требуется Uаб≥2UБЭ.нас. Так как это условие не выполняется, то VT3 и VD1 оказываются закрытыми и напряжение на входе схемы равно UКЭ.нас=U0 6. Лог уровни ттл и дтл 7. ЛЭ ТТЛш схема и принцип работы логические уровни МС этого вида среди других изделий ТТЛ имеют максимальное быстродействие при умеренном потреблении мощности. В p-n – переходе обычного диода, смещенном в прямом направлении, перенос тока обусловлен инжекцией неосновных носителей из одной области ПП в другую, вследствие чего после переключения приложенного напряжения с прямого на обратное, ток протекает некоторое время, пока избыточная концентрация неосновных носителей не снизится до 0 (время рассасывания). В диодах Шотки накопления неосновных носителей не происходит. Основные носители – электроны, под действием высокого напряжения, переходят в металл. 0,4 В _ Неосновные носители заряда при этом не накапливаются. Благодаря этому + + их время выключения очень мало (до 100 пс = 0,1 нс). Для p-n перехода это время = 1 – 100 нс. 0,4 В + Другое достоинство диодов Шотки в том, что они отпираются при 0,2 – 0,4 _ 0,8 В _ В (против 0,4 – 0,7 для p-n перехода). Диоды подключают параллельно коллекторному переходу, придавая транзистору новые свойства. Такие транзисторы называются транзисторами Шотки. Когда транзистор заперт или находится в насыщенном режиме, потенциал коллектора Схема базового элемента ТТЛШ 0,9к 50 Схема маломощного базового элемента ТТЛШ 75к 8к 200 x1 x1 Выход x2 x4 4к 0,5к 0,25к 1,5к 3к 3,5к выше потенциала базы, диод смещен в обратном направлении и не влияет на работу транзистора. Если в процессе отпирания транзистора потенциал коллектора становится ниже потенциала базы, диод открывается Uд<4 В. При этом коллекторный переход практически заперт, а, следовательно, не возникает режима насыщения и накопления избыточных зарядов. Благодаря этому, при запирании транзистора, исключается задержка, связанная с рассасыванием избыточного заряда. 8. ЛЭ ЭСЛ принцип работы и логические уровни Эмиттерно-связанная логика (ЭСЛ) – один из вариантов логических схем, работающих в ненасыщенном режиме. ЭСЛ-схемы имеют низкий выходной импеданс, небольшой разброс уровней логического напряжения и хорошую помехоустойчивость для обоих уровней логического напряжения. Первым разработчиком ИМС по технологии ЭСЛ была фирма Motorola, которая выпустила серию ИМС МС 10000 (отечественные аналоги – 100 и 500 серии). Интегральные элементы эмиттерно-связанной логики или переключатели тока транзисторной логики (ПТТЛ) относятся к потенциальным элементам: «1» и «0» в потенциальной системе представляются в виде потенциалов, т. е. напряжений того или иного знака. В настоящее время промышленностью выпускается несколько серий элементов ЭСЛ (например, К137, К187, К229, 100, К500, 500 и др.), обладающих функциональной и технической полнотой, т. е. обеспечивающих выполнение любых арифметических и логических операций, а также хранение, вспомогательные и специальные функции. Назначение элементов и принцип работы базовой схемы эмиттерно-связанной логики (ЭСЛ) Логика работы На рис. 3.1(а) показано условное графическое обозначение базового элемента ЭСЛ на функциональных схемах, где х1, х2, …, хn – входы; у1 – инверсный выход; у2 – прямой выход. Минимальное число входов равно двум. Элемент реализует для “положительной логики” одновременно функции ИЛИ–НЕ (стрелка Пирса) по выходу у1 и функцию ИЛИ (дизъюнкция) по выходу у2. Логика работы элемента на три входа представлена таблицей состояний (табл. 3.1). Таблица 3.1 Таблица состояний элемента ЭСЛ для «положительной» логики х1 х1 х1 у1 у1 0 0 0 1 0 1 0 0 0 1 0 1 0 0 1 0 0 1 0 1 1 1 0 0 1 1 0 1 0 1 0 1 1 0 1 1 1 1 0 1 Рис. 3.1. Условное графическое обозначение элемента ЭСЛ Рис. 3.2. Временная диаграмма работы элемента ЭСЛ Логическое уравнение работы элемента, составленное по табл. 3.1, записывается в виде (3.1) В (3.1) знак плюс соответствует дизъюнкции, т. е. логическому сложению. На рис. 3.2(а) приведена временная диаграмма, поясняющая логику работы элемента ЭСЛ на три входа. На рис. 3.3 приведена принципиальная электрическая схема элемента ЭСЛ с напряжением питания . В зависимости от способа кодирования входной информации («1» и «0») эта схема может реализовать либо функции ИЛИ–НЕ, ИЛИ для положительной логики, либо функции И–НЕ, И для отрицательной логики. Рис. 3.3. Схема электрическая принципиальная элемента ЭСЛ Рассмотрим принцип работы элемента ЭСЛ с положительной логикой (при анализе динамического режима работы следует учитывать наличие эквивалентных емкостей на выходах токового переключателя и эмиттерных повторителей). Выбираем средние значения напряжений, соответствующие состояниям «0» и «1», т. е. «1», т.е. , . Напряжение Uоп – среднее значение между уровнями «0» и ; следовательно, . Далее принимаем , . Случай 1. На входах х1–х3 уровень напряжения U0вх, транзисторы Т1–Т3 закрываются, транзистор Т4 открывается и ток проходит через правую ветвь. При этом на коллекторах транзисторов Т1–Т3 будет уровень напряжения Ulвых, а на коллекторе транзистора Т4 – уровень напряжения U0вых. В этом случае эмиттеры транзисторов Т1–Т4 находятся под напряжением Uэ = Uоп – UбэТ4 = – 1,95 В (принимаем UбэТ = 0,7 В). Разность напряжений между базой и эмиттером транзисторов Т1–Т3 равна Uбэ = U0вх – Uэ = 0,325 В, что недостаточно для открывания транзисторов Т1–Т3. Ток IR3 определяется напряжением Uэ, сопротивлением резистора R3 и проходит через открытый транзистор T4. На резисторе R2 создается падение напряжения UR2 = – R2(IкТ4+IбТ7) = – 0,925 В; при этом R2IКТ4 = –0,8 В; R2IБТ7 = – 0,125 В. Уровень напряжения на выходе у2 с учетом падения напряжения на переходе UбэТ4 = 0,7 В равен U0у2 = UR2 – UбэТ7 = – 1,625 В. Уровень напряжения на выходе у1 с учетом падения напряжения на переходе UбэТ6 = 0,7 В равен U1у1 = UR1 – UбэТ6 = – 0,825 В; UR1 = IбТ6R1 = – 0,125 В. Таким образом, уровни напряжений на выходах у1 и у2 определены. 9. чем объяснятся сверхвысокое быстродейтвие эсл 10. схема базового элемента ЭСЛ и его работа, логические уровни 11. ЛЭ И2Л схема базового элемента, принцип работы, логические уровни В основе И2Л схем лежат два принципа:1) совмещение электрически связанных однородных областей полупроводника в кристалле ИС, что приводит к увеличению степени интеграции; 2) отказ от традиционного способа питания цепи базы и коллектора ключевых транзисторов через резисторы. На рисунке показана инжекционная структура с дополнительным р — n-переходом. Если база (область р2) переключающего вертикального транзистора n2 — р2 — n1 -типа расположена вблизи прямосмещенного перехода р1—n1, то часть инжектированных данным переходом дырок попадает в область базы р2. В результате нарушения электронейтральности базы этого транзистора через переход база — эмиттер начинает протекать ток, смещающий этот переход в прямом направлении. Область р1, введенную для инжекции избыточных носителей, называют инжектором Е. Питание инжектора осуществляется от внешнего генератора тока или от источника напряжения через резистор (один внешний резистор). Данную инжекционную структуру можно представить в виде схемы, содержащей два транзистора: токозадающий горизонтальный р1—n1—р2-типа (включен по схеме с общей базой) и переключающий верти-кальный n2 — p2—n1-типа. Упрощенная эквивалентная схема состоит из транзистора n — p — n-типа и генератора тока I в цепи его базы. Обычно транзистор n — p — n-типа выполняется с несколькими коллекторами (область n3).Когда транзисторы VT1 и VT2 закрыты, транзистор VT3 открыт током инжектора I (сплошная линия прохождения тока) и напряжение в узле 2 ЛЭ И2Л что соответствует уровню логической 1 в ПЛ. Если транзистор VT2 откроется, то ток инжектора VT3 переключится в цепь коллектора VT2 (пунктирная линия) и транзистор VT3 закроется. В узле 2 будет напряжение насыщения коллектора VT2: Площадь, приходящаяся на один ЛЭ в схемах в И2Л, приблизительно в 10 раз меньше, чем в схемах ТТЛ. Применение диодов Шотки в схемах И2Л позволяет без увеличения потребляемой мощности получить еще более высокое быстродействие. Реализация логических функций на лэ И2Л Основой принцип инжекционной схемотехники: объединение выходов инжекционных ин векторов реализует логическую функцию монтажное И. Достоинства: Минимальная площадь (для эпитаксиально-планарной технологии). Минимальная мощность (для биполярных схем) (уменьшение рабочего тока) Минимальная pt (среди всех схем) Недостатки: Большая задержка (5-100 нс.) Необходимость подтягивать параметры (n+) Возрастает площадь - чем больше сложность, тем ниже надежность. ИЛИ-НЕ 12. ЛЭ КМОП и КМДП принцип работы, схема ЛЭ «и-не» и логические уровни КМОП (К-МОП; комплементарная логика на транзисторах металл-оксид-полупроводник; англ. CMOS, Complementary-symmetry/metal-oxide semiconductor). Большое распространение получили в последнее время ИМС на основе полевых транзисторов структуры МОП. Принципиальные особенности их позволяют создавать элементы и новые узлы цифровых устройств с малым потреблением P при высокой помехоустойчивости и нагрузочной способности. Сравнительно с биполярными они имеют меньшие размеры, что позволяет разместить на единице площади кристалла большее число элементов при более простой технологии. Действие их основано на управлении рабочим током при помощи электрического поля, создаваемого входным напряжением, поэтому для полевых транзисторов характерно высокое входное сопротивление.Анализируя передаточную характеристику, можно сделать выводы: 1.Логические уровни у схемы равны соответственно: нижний – нулю, верхний - Uи.п. Полезный сигнал на выходе равен напряжению питания (никакая другая схемотехника не обеспечивает этих возможностей). 2.Работоспособность схемы не зависит от напряжения питания, начиная со значений Uи.п> 2Uотп, т.е. схема может работать при весьма больших разбросах по питанию, если начальный его уровень выбран с соответствующим запасом. Элементы КМДП цифровых микросхем используют пары МДП-транзисторов (со структурой металл - диэлектрик-полупроводник) Реализация И-НЕ ИЛИ-НЕ на КМОП элементах Большое распространение получили в последнее время ИМС на основе полевых транзисторов структуры МОП. a Q Принципиальные особенности их E позволяют создавать элементы и новые узлы цифровых устройств с малым потреблением P при высокой помехоустойчивости и нагрузочной способности. Сравнительно с биполярными они имеют меньшие размеры, что позволяет разместить на единице площади кристалла большее число элементов при более простой технологии. Действие их основано на управлении рабочим током при помощи электрического поля, создаваемого входным напряжением, поэтому для полевых транзисторов характерно высокое входное сопротивление. Чтобы открыть оба нижних транзистора надо, чтобы на входе A и входе B была логическая единица, при этом оба верхних транзистора закроются и на выходе Q будет логический ноль. Если хотя бы на одном или на обоих входах будет логический ноль, то хотя бы один из нижних транзисторов закроется, один из верхних откроется, при этом на выходе будет логическая единица. Схема КМОП ЛЭ И–НЕ и его таблица истинности: Схема КМОП ЛЭ ИЛИ–НЕ и его таблица истинности: Если на входах A или B (или на обоих) логическая единица, то откроется один или оба из нижних транзисторов, при этом закроется один или оба верхних транзистора, тогда на выходе логический ноль. Если на обоих входах логический ноль, то закроются оба нижних и откроются оба верхних транзистора, при этом на выходе логическая единица. 13. Что такое Триггер? Для чего он предназначен? Триггер— это запоминающий элемент с двумя (или более) устойчивыми состояниями, изменение которых происходит под действием входных сигналов и предназначен для хранения одного бита информации, то есть лог. 0 или лог. 1. Все разновидности триггеров представляют собой элементарный автомат, включающий собственно элемент памяти (ЭП) и комбинационную схему (КС), которая может называться схемой управления или входной логикой (рис. 7). 14. разновидности триггеров (RS YK D T) RS-триггер— триггер, который сохраняет своё предыдущее состояние при нулевых входах и меняет своё выходное состояние при подаче на один из его входов единицы. При подаче единицы на вход S (от англ. Set — установить) выходное состояние становится равным логической единице. А при подаче единицы на вход R (от англ. Reset — сбросить) выходное состояние становится равным логическому нулю. Состояние, при котором на оба входа R и S одновременно поданы логические единицы, в простейших реализациях является запрещённым (так как вводит схему в режим генерации), в более сложных реализациях RS-триггер переходит в третье состояние QQ=00. Одновременное снятие двух «1» практически невозможно. При снятии одной из «1» RS-триггер переходит в состояние, определяемое оставшейся «1». Таким образом RS-триггер имеет три состояния, из которых два устойчивых (при снятии сигналов управления RS-триггер остаётся в установленном состоянии) и одно неустойчивое (при снятии сигналов управления RS-триггер не остаётся в установленном состоянии, а переходит в одно из двух устойчивых состояний). RS-триггер используется для создания сигнала с положительным и отрицательным фронтами, отдельно управляемыми посредством стробов, разнесённых во времени. Также RS-триггеры часто используются для исключения так называемого явления дребезга контактов. D-триггер (D от англ. delay — задержка либо от data - данные) — запоминает состояние входа и выдаёт его на выход. D-триггеры имеют, как минимум, два входа: информационный D и синхронизации С. После прихода активного фронтаимпульса синхронизации на вход С D-триггер открывается. Сохранение информации в D-триггерах происходит после спада импульса синхронизации С. Так как информация на выходе остаётся неизменной до прихода очередного импульса синхронизации, D-триггер называют также триггером с запоминанием информации или триггером-защёлкой. Рассуждая чисто теоретически, парафазный (двухфазный) D-триггер можно образовать из любых RS- или JK-триггеров, если на их входы одновременно подавать взаимно инверсные сигналы. D-триггер в основном используется для реализации защёлки. Так, например, для снятия 32 бит информации с параллельной шины, берут 32 D-триггера и объединяют их входы синхронизации для управления записью информации в защёлку, а 32 D входа подсоединяют к шине. T-триггеры Т-триггер (от англ. Toggle - переключатель) часто называют счётным триггером, так как он является простейшим счётчиком до 2. Т-триггер асинхронный Асинхронный Т-триггер не имеет входа разрешения счёта - Т и переключается по каждому тактовому импульсу на входе С. T-триггер синхронный Синхронный Т-триггер, при единице на входе Т, по каждому такту на входе С изменяет своё логическое состояние на противоположное, и не изменяет выходное состояние при нуле на входе T. Т-триггер можно построить на JK-триггере, на двухступенчатом (MasterSlave, MS) D-триггере и на двух одноступенчатых D-триггерах и инверторе. Т-триггер часто применяют для понижения частоты в 2 раза, при этом на Т вход подают единицу, а на С — сигнал с частотой, которая будет поделена на 2. JK-триггер работает так же как RS-триггер, с одним лишь исключением: при подаче логической единицы на оба входа J и K состояние выхода триггера изменяется на противоположное. Вход J (от англ. Jump — прыжок) аналогичен входу S у RS-триггера. Вход K (от англ. Kill — убить) аналогичен входу R у RS-триггера. При подаче единицы на вход J и нуля на вход K выходное состояние триггера становится равным логической единице. А при подаче единицы на вход K и нуля на вход J выходное состояние триггера становится равным логическому нулю. JK-триггер в отличие от RS-триггера не имеет запрещённых состояний на основных входах, однако это никак не помогает при нарушении правил разработки логических схем. На практике применяются только синхронные JK-триггеры, то есть состояния основных входов J и Kучитываются только в момент тактирования, например по положительному фронту импульса на входе синхронизации. На базе JK-триггера возможно построить D-триггер или Т-триггер. Как можно видеть в таблице истинности JK-триггера, он переходит в инверсное состояние каждый раз при одновременной подаче на входы J и K логической 1. Это свойство позволяет создать на базе JK-триггера Т-триггер, объединив входы J и К 15. двухтактные(двухступенчатые ) триггеры, для чего они предназначены Триггер — это запоминающий элемент с двумя (или более) устойчивыми состояниями, изменение которых происходит под действием входных сигналов и предназначен для хранения одного бита информации, то есть лог. 0 или лог. 1. Все разновидности триггеров представляют собой элементарный автомат, включающий собственно элемент памяти (ЭП) и комбинационную схему (КС), которая может называться схемой управления или входной логикой (рис. 7). Этот тактовый запоминатель используется в регистровых сдвигах так как при перемещении информации из одного такта в другой, можно записать новую информацию в первый такт. Двухтактный RS-триггер: Двухтактный JK-триггер: 16. регистр, его устройство, назначение и режимы работы Регистр — последовательное или параллельное логическое устройство, используемое для хранения n-разрядных двоичных чисел и выполнения преобразований над ними. Слева – D10 – D17 – это входы Справа – D0 – D07 – это выходы S – синхронизация Е0 – туда надо ноль подавать Регистры относятся к последовательностным схемам, то есть к схемам с памятью. Функции регистров: 1) Хранение информации. 2) Прием информации. 3) Выдача информации. 4) Сдвиг информации. 5) Преобразование кодов. 6) Установление в ноль или в единицу нужного числа. 7) Поразрядные логические операции: дизъюнкция, конъюнкция, Сложение по модулю 2. Общая классификация регистров: 1. Регистры с параллельным приемом и выдачей информации: Слово равно m разрядов. 2. Регистр с параллельным приемом и последовательной выдачей информации: Сдвиг на 1 разряд n+1 тактов на последовательную выдачу. 3. Регистр с последовательным приемом и параллельной выдачей информации: За m тактов принимается m-разрядное слово: 4. Регистр с последовательным приемом и последовательной выдачью информации: 5. Универсальный регистр: M1 M2 Вид приема инф. Вид выдачи инф. 0 0 Параллельный Параллельный 0 1 Параллельный Последовательный 1 0 Последовательный Параллельный 1 1 Последовательный Последовательный Регистр с параллельным приемом и выдачей информации называется регистром хранения (Первый тип регистров). Регистр с последовательным приемом или выдачей информации называется регистром сдвига (второй, третий и четвертый типы регистров). 17.Разновидности регистров. Назначение регистров –хранение и преобразование много разрядных двоичных чисел. Регистры наряду со счетчиками и запоминающими устройствами являются наиболее распространенными последовательностными устройствами цифровой техники. Регистры обладают большими функциональными возможностями. Они используются в качестве управляющих и запоминающих устройств, генераторов и преобразователей кодов, счетчиков, делителей частоты, узлов временной задержки. Элементами структуры регистров являются синхронные триггеры Д-типа, либо RS(JK)-типа с динамическим или статическим управлением. Единичный триггер–простейший регистр (RG) используют в RG цепочке триггеров. Понятие "весовой коэффициент" к разрядам регистра неприменимо в отличие от счетчика, поэтому на условных изображениях нумерация входов и выходов идет подряд (Д1, Д2,Д3 и т.д., а не Д1, Д2, Д4, Д8). RG в зависимости от функциональных свойств делятся на накопительные и сдвигающие. По способу ввода, вывода информации – параллельные, последовательные и комбинированные. По направлению передачи (сдвига) информации – однонаправленные и реверсные. Регистры памяти – простейший вид регистров – хранят двоичную информацию. Это набор синхронных триггеров, каждый из которых хранит один разряд двоичного числа. Ввод (запись) и вывод (считывание) производится одновременно во всех разрядах. С приходом очередного тактового импульса происходит обновление информации. Считывание информации в прямом или обратном (с Q) коде. В качестве подобных регистров может быть использованы без дополнений элементов многих синхронных триггеров: К155ТМ8, ТМ5, ТМ7, 564ТМ3, 555ТМ8 и др. Наращивание разрядности регистра достигается добавлением нужного числа триггеров, тактовые выходы которых присоединяют к шине синхронизации. К1555ИР15 – регистр с тремя состояниями Д1-Д4 – информационные входы, С – синхронизированный вход, Q1-Q4 – прямые выходы, Е1, Е2 – разрешающие: запись при Е1=Е2=0(если на одном из Е "1" то это режим хранения информации), ЕZ1.EZ2 – перевод в 3-е состояние, R – установка в "0" ("1"), с приходом "1" на R вес триггера устанавливается в "0", при вводе информации на Е1, У2 и R должен быть "0". Если на EZ (любом) "1" – выходы отключаются. 19. двоичные счётчики. назначении, принцип работы, коэффициент пересчета Счетчиком называют цифровое устройство, обеспечивающее подсчет числа электрических импульсов. Коэффициент пересчета счетчика равен минимальному числу импульсов, поступивших на вход счетчика, после которых состояния на выходе счетчика начинают повторяться. Счетчик называют суммирующим, если после каждого очередного импульса цифровой код на выходе счетчика увеличивается на единицу. В вычитающем счетчике после каждого импульса на входе счетчика цифровой код на выходе уменьшается на единицу. Счетчики, в которых возможно переключение с режима суммирования на режим вычитания, называются реверсивными. Суммирующий счетчик работает по принципу суммирования сигналов, поступающих на его вход. В начальный момент времени все триггеры устанавливаются сигналом Уст 0 в состояние “0”. После прихода первого счетного импульса триггер Тг1 перейдет в состояние “1” и в счетчике зафиксируется код 001.Второй импульс, пришедший на вход, переведет Тг1 снова в состояние “0”. При этом возникает импульс переноса, который устанавливает следующий триггер Тг2 в состояние “1” и в счетчике зафиксируется код 010. После третьего входного сигнала Тг1 вновь прейдет в состояние “1”, а остальные триггеры останутся в прежнем состоянии. Так будет продолжаться до тех пор, пока счетчик не просуммирует максимальное для трех разрядов число 710=1112. Восьмой импульс переведет Тг1 в состояние “0”, возникший перенос поступит на Тг2 и также переведет его в состояние “0”. В свою очередь, импульс переноса со второго разряда переведет в состояние “0” и Тг3. В результате этого счетчик установится в исходное нулевое состояние (000) 20. как коэффициент пересчета двоичного счетчика(напрмер к=10) 21. Мультиплексоры. определение, принцип построения и разновидности (например кп5 и кп7) Мультиплексор – это функциональный узел, осуществляющий подключение ( коммутацию ) одного из нескольких входов данных к выходу. С помощью мультиплексора выполняется временное разделение информации, поступающей по разным каналам. Мультиплексоры обладают двумя группами входов и одним, реже двумя – взаимодополняющими выходами. Одни входы информационные, а другие служат для управления. К ним относятся адресные и разрешающие (стробирующие) входы. Если мультиплексор имеет n адресных входов, то число информационных входов будет 2 n. Набор сигналов на адресных входах определяет конкретный информационный вход, который будет соединен в выходным выводом. Разрешающий (стробирующий ) вход управляет одновременно всеми информационными входами независимо от состояния адресных входов. Наличие разрешающего входа расширяет возможности мультиплексора, позволяя синхронизировать его работу с работой других узлов. Этот вход используется также для наращивания разрядности. Запрещающий сигнал на этом входе блокирует действие всего устройства. Наличие разрешающего входа расширяет функциональные возможности мультиплексора, позволяя синхронизировать его работу с работой других узлов. Этот вход используется также для наращивания разрядности мультиплексора. На рисунке показаны схема и условное обозначение мультиплексора К555КП7. X0 & X1 & X2 & X3 x0 MS x1 x2 x3 x4 x5 y x6 x7 y 1 1 y & X4 y & X5 X6 X7 & a0 a1 a2 & E & E A2 1 1 A1 1 1 A0 1 1 Схема а) и условное обозначение б) мультиплексора К555КП7. Структура этой микросхемы описывается следующими уравнением: Y E (A0 * A1 * A0 * X0 A2 * A1 * A0 * X1 A2 * A1 * A0 * X2 A2 * A1 * A0 * X3 A2 * A1 * A0 * X4 A2 * A1 * A0 * X5 A2 * A1 * A0 * X6 A2 * A1 * A0 * X7) ( 3.1 ) По функциональным возможностям мультиплексоры являются очень гибкими устройствами и помимо прямого назначения могут выполнять и другие функции. Из (3.1) при Е=0 следует, что это СДНФ функции У1 переменных А2, А1 и А0, если х i как конкретное значение у i на соотвествующем наборе перемене А2, А1 и А0. В таблице 3.1 приведены функции: У1=f1 (А, В, С) и У2=f2(А, В, С, D). A 0 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1 A B 0 0 0 0 1 1 1 1 0 0 0 0 1 1 1 1 B C 0 0 1 1 0 0 1 1 0 0 1 1 0 0 1 1 C D 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 Y1 0 0 0 1 0 1 1 1 Y2 0 0 0 1 1 1 1 0 0 1 1 0 0 0 1 0 На рис. 3.9,а показана реализация на мультиплексоре функции У1. В этом случае х i равно “0” и “1” для соответствующего набора в табл. 3.1. На рис. 3.9,б показана реализация функции У2, где х i равно 0, 1, D или не D. "1" "0" x0 MS x1 x2 x3 x4 x5 y x6 x7 y A B C "0" x0 MS x1 x2 x3 x4 x5 y x6 x7 y "0" D "1" 1 Y1 "0" a0 a1 a2 a0 a1 a2 A B C E Y1 E "0" Рис.3.9. Схемы реализации произвольных логических функций на мультиплексорах. У мультиплексоров, выпускаемых в виде ИС, число информационных входов не превышает шестнадцати. Большее число входов обеспечивается путем наращивания. На рис. 3.10, а показано условное обозначение мультиплексора К155КП1 на 16 входов. На рис. 3.10, б показана схема мультиплексора на 32 входа, построенная на двух микросхемах К155КП1. x0 x0 MS x1 x2 x3 x4 x5 x6 x7 x8 y x9 x10 x11 x12 x13 x14 x15 a0 a1 a2 a3 E x15 a0 a1 a2 a3 a4 x0 MS x15 a0 a1 a2 a3 E y & Y & x0 MS a16 a31 E & x15 a0 a1 a2 a3 E y Рис.3.10. а) Мультиплексор К155КП1 б)32-входовой мультиплексор Демультиплексоры. Демультиплексор – это функциональный узел, осуществляющий коммутацию информации с одного входа на один из нескольких выходов. Демультиплексоры в виде самостоятельных ИС не изготавливаются, т.к. их функции могут выполняться дешифратором, имеющим хотя бы один вход разрешения, который используется как информационный вход. Если информационные входы и выходы обоих коммутаторов представляют линии, то такие коммутаторы называют линейными. Если же входы и выходы – шины, то получим шинные мультиплексоры и демультиплексоры. 22. двоичные сумматоры(полусумматор и полный сумматор) Сумматоры. Простейшим суммирующим элементом является полусумматор. Он имеет два входа А и В и два выхода: S (cумма ) и P (перенос) (рисунок а). A HS B S A P B SM S1 P1 P0 а) б) Рисунок. Суммирующие элементы Обозначением полусумматора служат буквы НS (Нalf Sum). Его работа описывается уравнениями S A B, P AB Процедуру сложения двух n – разрядных двоичных чисел можно представить следующим образом. Сложение цифр А0 и В0 младшего разряда дает бит суммы S0 и бит переноса P1. В следующем разряде производится сложение цифр А1, В1, и Р1, которое формирует бит суммы S1 и перенос Р2. Полный одноразрядный сумматор имеет три входа (рисунок б): два для слагаемых А и В и один для сигнала переноса с предыдущего разряда. На рисунке 2 показана схема, поясняющая принцип действия n- разрядного сумматора с последовательным переносом. Число сумматоров здесь равно числу разрядов. Выход переноса Р каждого сумматора соединен со входом переноса следующего, более старшего разряда. На входе переноса сумматора младших разрядов установлен “0”, так как сигнал переноса сюда не поступает. S0 b0 a0 a SM "0" S1 b1 a1 Sn-1 Sn bn-1 an-1 a SM a SM b S b S b S P0 P P0 P P0 P Рис. 2 Сумматор с последовательным переносом. Слагаемые А i и Bi складываются во всех разрядах одновременно, а перенос Р поступает с окончанием операции сложения в предыдущем разряде. Быстродействие многоразрядных сумматоров подобного вида ограничено задержкой переноса, так как формирование сигнала переноса на выходе старшего разряда не может произойти до тех пор, пока сигнал переноса младшего разряда не распространится последовательно по всей схеме. Время переноса можно уменьшить, вводя параллельный перенос, для чего применяют специальные узлы – блоки ускоренного переноса. Они имеют достаточно сложную схему даже для n = 4 и с увеличением числа разрядов сложность настолько возрастает, что изготовление их становится нецелесообразно. В виде отдельных микросхем выпускаются одноразрядные, двухразрядные и четырехразрядные сумматоры. В семействе ТТЛ это микросхемы соответственно К155ИМ1, ИМ2 и ИМ3. 23. как из 2х полусумматоров построить полный сумматор Одноразрядные двоичные сумматоры строятся по самым различным схемам. Рассмотрим функционирование одноразрядного сумматора, составленного из двух полусумматоров. Полусумматор - это устройство, производящее сложение двух одноразрядных двоичных чисел без учета переноса предыдущего разряда. Составим таблицу истинности полусумматора и полного одноразрядного двоичного сумматора (таблица 1.2). Ai, Bi – двоичные цифры i разряда, Pi-1 – перенос из (i-1) разряда, Si – сумма, получившаяся в i разряде, Pi - перенос из i разряда в (i+1) разряд. Первые четыре строчки таблицы 1.2 представляют собой таблицу истинности полусумматора. Сконструируем двоичный полусумматор. Из таблицы истинности следует, что полусумматор должен иметь два входа и два выхода. Следовательно, нам потребуются, по крайней мере, два двухвходовых логических элемента (каждый логический элемент имеет только один выход). Из таблиц истинности логических элементов и полусумматора видно, что для получения суммы двух одноразрядных двоичных чисел необходимо использовать логический элемент исключающее ИЛИ, а для получения переноса – логический элемент 2И. Схема полусумматора, построенного на указанных логических элементах, приведена на рисунке 1.31. Схема полного одноразрядного сумматора построенного на двух полусумматорах приведена на рисунке 1.32. Один полусумматор используется для сложения i-го разряда двоичных чисел, а второй полусумматор складывает результат первого полусумматора с переносом из (i-1) разряда. Показать самостоятельно, что для получения переноса в полном одноразрядном двоичном сумматоре необходимо сигналы переносов от полусумматоров подать на входы логического элемента 2ИЛИ, на выходе которого получится перенос из полного одноразрядного двоичного сумматора. 24. что такое диод шотки и для чего он предназначен. в чем его отличие от обычного диода. Диод Шоттки (также правильно Шотки, сокращённо ДШ) — полупроводниковый диод с малым падением напряжения при прямом включении. Назван в честь немецкого физика Вальтера Шоттки. Диоды Шоттки используют переход металл-полупроводник в качестве барьера Шоттки (вместо p-n перехода, как у обычных диодов). Допустимое обратное напряжение промышленно выпускаемых диодов Шоттки ограничено 250 В (MBR40250 и аналоги), на практике большинство диодов Шоттки применяется в низковольтных цепях при обратном напряжении порядка единиц и нескольких десятков вольт. Свойства диодов Шоттки Достоинства В то время, как обычные кремниевые диоды имеют прямое падение напряжения около 0,6—0,7 вольт, применение диодов Шоттки позволяет снизить это значение до 0,2—0,4 вольт. Столь малое прямое падение напряжения присуще только диодам Шоттки с максимальным обратным напряжением порядка десятков вольт, выше же падение напряжения становится сравнимым с аналогичным параметром кремниевых диодов, что ограничивает применение диодов Шоттки. Барьер Шоттки (открыл нем. физик Вальтер Шоттки — Walter Schottky) также имеет меньшую электрическую ёмкость перехода, что позволяет заметно повысить рабочую частоту. Это свойство используется в интегральных микросхемах, где диодами Шоттки шунтируются переходы транзисторов логических элементов. В силовой электронике малое время восстановления позволяет строить выпрямители на частоты в сотни кГц и выше. Например, диод MBR4015 (15 В, 40 А), оптимизированный под высокочастотное выпрямление, нормирован для работы при dV/dt до 10 кВ/мкс. Благодаря лучшим временны́м характеристикам и малым ёмкостям перехода выпрямители на диодах Шоттки отличаются от традиционных диодных выпрямителей пониженным уровнем помех, поэтому они предпочтительны в традиционных трансформаторных блоках питания аналоговой аппаратуры. Недостатки при кратковременном превышении максимального обратного напряжения диод Шоттки необратимо выходит из строя (КЗ — короткое замыкание), в отличие от обычных кремниевых p-n диодов, которые переходят в режим обратимого[1] пробоя, и, при условии непревышения рассеиваемой на диоде максимальной мощности после падения напряжения, диод полностью восстанавливает свои свойства. диоды Шоттки характеризуются повышенными (относительно обычных кремниевых p-n диодов) обратными токами, возрастающими с ростом температуры кристалла. Для вышеупомянутого 30CPQ150 обратный ток при максимальном обратном напряжении изменяется от 0,12 мА при +25 °C до 6,0 мА при +125 °C. У низковольтных диодов в корпусах ТО220 обратный ток может превышать сотни миллиампер (MBR4015 — до 600 мА при +125 °C). При неудовлетворительных условиях теплоотвода положительная обратная связь по теплу в диоде Шоттки приводит к его катастрофическому перегреву. Применяются в ТТЛШ Номенклатура диодов Шоттки Диоды Шоттки — составные части современных дискретных полупроводниковых приборов: МОП-транзисторы со встроенным обратным диодом Шоттки (впервые выпущены компанией International Rectifier под торговой маркой FETKY в 1996) — основной компонент синхронных выпрямителей. В отличие от обычного МОП-транзистора, обратный диод которого отличается высоким прямым падением напряжения и посредственными временны́ми характеристиками, использование обратного диода Шоттки позволяет строить силовые синхронные выпрямители с частотой преобразования в сотни кГц и выше. Существуют приборы этого класса со встроенными драйверами затворов и устройствами управления синхронным выпрямлением. Так называемые ORing-диоды и ORing-сборки — силовые диоды и диодные сборки, применяемые для объединения параллельных источников питания общей нагрузки в устройствах повышенной надёжности (логическое ИЛИ по питанию). Отличаются особо низким, нормируемым прямым падением напряжения. Например, специализированный миниатюрный диод MBR140 (30 В, 1 А) при токе 100 мА имеет прямое падение напряжения не более 360 мВ при +25 °C и 300 мВ при +85 °C. ORing-диоды характеризуются относительно большой плошадью P-N перехода и низкими удельными плотностями тока. 25. что такое триггер шмитта. для чего он предназначен Триггер Шмидта - это специфический вид триггера, имеющего один вход и один выход. Такой триггер Еще называют нессиметричным. В триггере Шмидта переход из одного устойчивого состояния в другое осуществляется при определенных уровнях входного напряжения, называемых пороговыми уровнями. Триггер Шмидта изображен ниже. Рис. 6 Триггер Шмидта и графики, поясняющие принцип его работы Если на вход триггера Шмидта подавать нарастающее напряжение (нижний график), то при некотором уровне Uп1 в момент t1 напряжение на выходе скачком переходит из состояния 0 в состояние 1. Если уменьшать напряжение на входе до некоторого напряжения Uп2 в момент t2 напряжение на выходе скачком переходит из состояния 1 в состояние 0. Явление несовпадения уровней Uп1 и Uп2 называется гистерезисом. Соответственно, передаточная характеристика триггера Шмидта обладает гистерезисным характером. Триггер Шмидта, в отличие от других триггеров, не обладает памятью и используется для формирования прямоугольных импульсов из напряжения произвольной формы. ТШ- логические элементы, специально рассчитанные на работу с входными аналоговыми сигналами. Они предназначены для преобразования входных аналоговых сигналов в выходные цифровые сигналы. 26. ЛЭ ТТЛ с 3мя устойчивыми состояниями Если произвести соединение выходов нескольких схем, то в состоянии, когда один из элементов имеет на выходе низкий потенциал, а другой – высокий потенциал; через последовательно соединенные транзисторы потечет значительный сквозной ток. При этом резко возрастает потребляемая мощность и возможен выход схем из строя В этом случае используются элементы ТТЛ, которые кроме двух обычных состояний выхода имеют третье, «отключенное» состояние. При низком потенциале на входе Х все транзисторы в инверторе оказываются закрытыми, и схема полностью отключается от нагрузки. При высоком потенциале элемент с тремя состояниями работает как обычный, выполняя операцию И-НЕ. Выходы таких элементов можно объединять, если в процессе работы устройства разрешать подключение к нагрузке не более одного элемента одновременно. Данную схему можно использовать в качестве схемы блокировки… Принципиальная схема ТТЛ с тремя состояниями. 27. ЛЭ ТТЛ, ДТЛ с открытытм коллектором. схема, принцип работы, назначение Несмотря на то, что базовые элементы ТТЛ имеют сравнительно высокое быстродействие, малые входные и большие выходные токи, хорошо работают на емкостную нагрузку, но имеют недостатки. У них происходит кратковременное увеличение потребляемой мощности в переходные процессы (т.е. переключения), при одновременном переключении большого количества ЛЭ. Броски тока в цепи питания достигают несколько единиц или десятков ампер. Хотя это частично устраняется путем установки в цепи питания отдельных конденсаторов большой емкости, компенсирующие эти кратковременные броски тока, чем обеспечивается уменьшение взаимосвязей (взаимовлияния) ЛЭ по цепям питания. Кроме больших токов при одновременном переключении такие ТТЛ имеют небольшие значения выходного сопротивления, что затрудняет объединение между собой выходы нескольких ЛЭ т.к. в случае разных выходных сигналов через выходные VT будут протекать большие токи. Поэтому у них на выходе устанавливают VTЗ коллекторная цепь которого оставлена свободной (рисунок 1.10). Рисунок 1.10 – Схема элемента ТТЛ с открытым коллектором (а), управление нестандартной нагрузкой (б), параллельное соединение выводов (в) ЛЭ с открытым коллектором (рисунок 1.10, а) могут работать на нетиповую нагрузку (реле, дроссель, обмотка трансформатора, индикаторной лампе, питаемой от UИП и др.) (рисунок 1.10, б), и включаться параллельно по выходам (рисунок 1.10, в). Параллельное включение выходов с открытым коллектором показано на рисунке 1.10, в. Стандартные элементы ТТЛ со сложными выходными инверторами нельзя соединять параллельно по выходам, так как при различных логических состояниях из-за малых выходных сопротивлений элементов в выходных цепях развились бы недопустимо большие токи, а логическое состояние общего выхода было бы неопределенным. Элементы с открытым коллектором допускают параллельное соединение выходов с общим нагрузочным резистором св. В данном случае относительно сигналов на базах выходных транзисторов выполняется операция , а элементы с открытым коллектором могут использоваться и для поочередной работы на общую линию в режиме разделения времени; для этой цели разработаны специальные элементы с тремя состояниями выхода: «1», «0» и «отключено» (отключающиеся от нагрузки), обеспечивающие более высокое быстродействие. В состоянии «отключено» выход элемента не потребляет и не отдает тока в нагрузку. Если в каждый момент времени лишь один из подключенных к магистральной шине элементов активен, а все остальные отключены, то обеспечивается нормальный режим разделения времени. При использовании такой ИМС (ЛЭ) открытый коллектор (рисунок 1.11, а) соединяется с источником напряжения через нагрузочное сопротивление Rсв (рисунок 1.11, б) или через обмотку реле (рис. 1.11, в), светодиод, лампу накаливания (рис. 1.10, б) и т.д. Открытый коллектор позволяет непосредственно подключать несколько ЛЭ (ИМС) и образовывать дополнительную логическую функцию – монтаменое И. Наличие открытого вывода для положительной логики: открытого коллектора для n-р-n VT; открытого эмиттера для р-n-р VT; у МОП- транзисторов у стока для n-канала; у истока для р-канала и для отрицательной логики все наоборот.