А.В. КОБЫЛЯЦКИЙ Научный руководитель – Н.Г. ГРИГОРЬЕВ, к.т.н., с.н.с.

advertisement

А.В. КОБЫЛЯЦКИЙ

Научный руководитель – Н.Г. ГРИГОРЬЕВ, к.т.н., с.н.с.

Национальный исследовательский ядерный университет «МИФИ»

ОСОБЕННОСТИ ПРИМЕНЕНИЯ КОДА ХЭММИНГА В

СТАТИЧЕСКОМ ОЗУ 16 МБИТ

Разработана схемотехника и топология кодера/декодера с учетом правил радиационно-стойкого проектирования (РСП). Проведено моделирование работы кодера/декодера с учетом паразитных параметров топологии и определено его быстродействие в режимах записи и чтения ОЗУ при нормальных и наихудших условиях функционирования.

Одним из наиболее эффективных способов снижения влияния одиночных сбоев и повышения устойчивости к отдельным ядерным частицам

(ОЯЧ) является использование корректирующего кода Хэмминга [1].

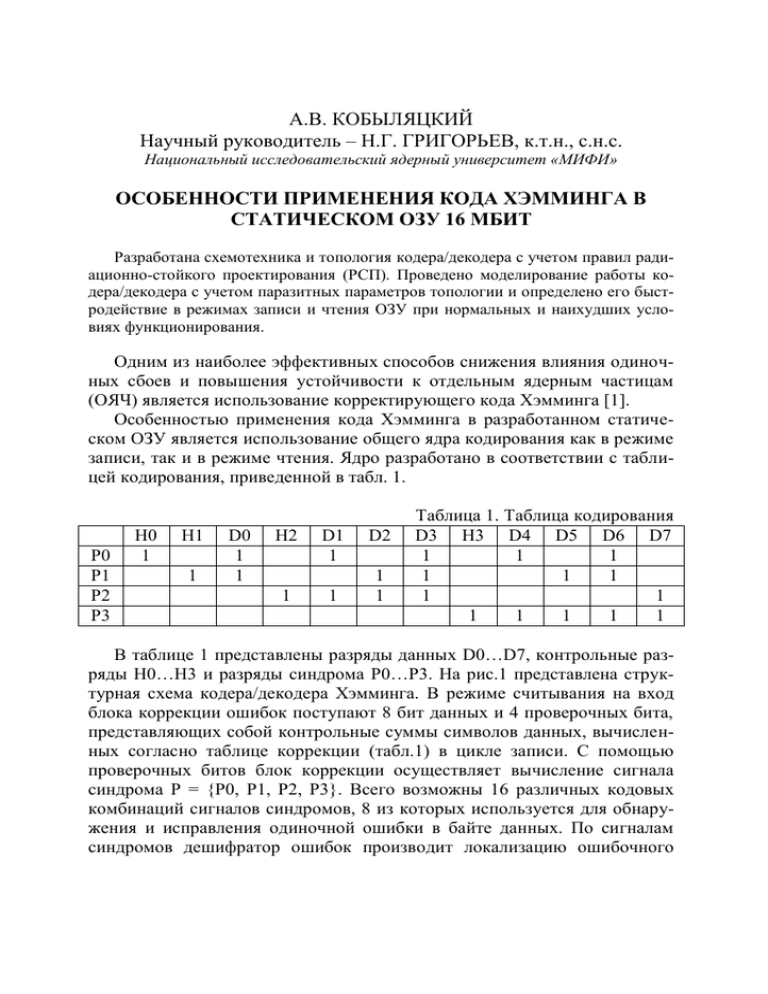

Особенностью применения кода Хэмминга в разработанном статическом ОЗУ является использование общего ядра кодирования как в режиме

записи, так и в режиме чтения. Ядро разработано в соответствии с таблицей кодирования, приведенной в табл. 1.

P0

P1

P2

P3

H0

1

H1

1

D0

1

1

H2

D1

1

1

1

D2

1

1

Таблица 1. Таблица кодирования

D3 H3 D4 D5 D6 D7

1

1

1

1

1

1

1

1

1

1

1

1

1

В таблице 1 представлены разряды данных D0…D7, контрольные разряды H0…H3 и разряды синдрома P0…P3. На рис.1 представлена структурная схема кодера/декодера Хэмминга. В режиме считывания на вход

блока коррекции ошибок поступают 8 бит данных и 4 проверочных бита,

представляющих собой контрольные суммы символов данных, вычисленных согласно таблице коррекции (табл.1) в цикле записи. С помощью

проверочных битов блок коррекции осуществляет вычисление сигнала

синдрома P = {P0, P1, P2, P3}. Всего возможны 16 различных кодовых

комбинаций сигналов синдромов, 8 из которых используется для обнаружения и исправления одиночной ошибки в байте данных. По сигналам

синдромов дешифратор ошибок производит локализацию ошибочного

бита и при установленном сигнале разрешения инверсии nIE = 0 вырабатывает сигнал на исправление соответствующего бита, который обрабатывается блоком инверсии, осуществляющем инвертирование ошибочного бита. Мультиплексоры осуществляют переключения сигналов в зависимости от цикла обращения к памяти при установленном в соответствующее состояние сигнале WR. В цикле записи контрольные разряды коммутируются на нулевой потенциал для последующего вычисления контрольных сумм данных и записи в отдельный накопитель.

Рис.1.Структурная схема кодера/декодера Хэмминга с исправлением ошибок

Схемотехника и топология кодера/декодера Хэмминга разработана по

КМОП технологии с проектными нормами 0,13 мкм для применения его в

составе сбоеустойчивой памяти СОЗУ с информационной емкостью 16

Мбит. Топологически блок кодера/декодера размещен в периферии кристалла. Разработка топологии осуществлялась в соответствии с основными правилами РСП по уменьшению токов утечки при облучении ИИ и

снижению вероятности возникновения тиристорного эффекта.

При разработке кодера были приняты дополнительные меры по увеличению устойчивости к эффектам одиночных и множественных сбоев при

воздействии ОЯЧ. Время задержки блока в режиме чтения с учетом паразитных параметров топологии составляет 1,3 нс при нормальных условиях.

Таким образом, разработанный блок кодирования не вносит дополнительных затрат по площади от СБИС ОЗУ и приводит к незначительному

увеличению времени выборки ОЗУ на 5-7 %.

1.

Список литературы

Телец В., Цыбин С., Быстрицкий А., Подъяпольский С. ПЛИС для космических

применений// ЭЛЕКТРОНИКА: Наука. Технология. Бизнес. – 2005. - №6.