Lec_8_10

реклама

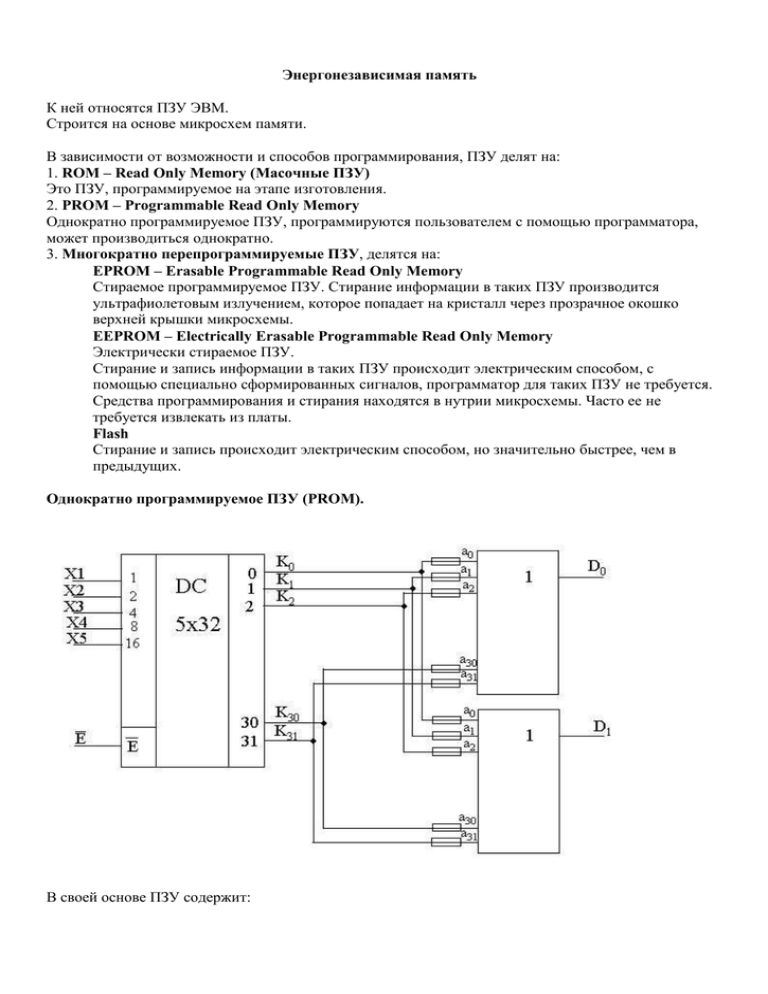

Энергонезависимая память К ней относятся ПЗУ ЭВМ. Строится на основе микросхем памяти. В зависимости от возможности и способов программирования, ПЗУ делят на: 1. ROM – Read Only Memory (Масочные ПЗУ) Это ПЗУ, программируемое на этапе изготовления. 2. PROM – Programmable Read Only Memory Однократно программируемое ПЗУ, программируются пользователем с помощью программатора, может производиться однократно. 3. Многократно перепрограммируемые ПЗУ, делятся на: EPROM – Erasable Programmable Read Only Memory Стираемое программируемое ПЗУ. Стирание информации в таких ПЗУ производится ультрафиолетовым излучением, которое попадает на кристалл через прозрачное окошко верхней крышки микросхемы. EEPROM – Electrically Erasable Programmable Read Only Memory Электрически стираемое ПЗУ. Стирание и запись информации в таких ПЗУ происходит электрическим способом, с помощью специально сформированных сигналов, программатор для таких ПЗУ не требуется. Средства программирования и стирания находятся в нутрии микросхемы. Часто ее не требуется извлекать из платы. Flash Стирание и запись происходит электрическим способом, но значительно быстрее, чем в предыдущих. Однократно программируемое ПЗУ (PROM). В своей основе ПЗУ содержит: Дешифратор DC на n входов и 2^n выходов и схемы ИЛИ, причем каждый выход дешифратора через плавкие перемычки подключен к входам схем ИЛИ. Число разрядов сигнала адреса Х5,Х4,Х3,Х2,Х1 определяет число двоичных комбинаций которое может быть записано в ПЗУ, т.е. число сигналов адреса определяет число ячеек ПЗУ. Количество схем ИЛИ определяет разрядность каждой ячейки памяти. В современных ПЗУ разрядность, как правило, равна 8. Каждая ячейка может хранить один байт информации. Для каждого выхода ПЗУ Dj будет реализовываться функция: D j E(K 0 a 0 K1a 1 K 3 a 3 ) E – сигнал разрешения работы, Е=1, то микросхема отключена. Ki – минтермы образованные адресными сигналами Х5,Х4,Х3,Х2,Х1 ai – состояние перемычки, если перемычка цела ai = 1, а если перемычка пережжена ai = 0. Программирование ПЗУ сводится к написанию для каждого выхода подобных логических выражений, из которых становится понятно, какие перемычки следует пережечь. Процесс программирования происходит с помощью программатора. При этом выходы ПЗУ являются входами, на которые подаются повышенные напряжения для пережигания плавких перемычек. Нужная перемычка выбирается с помощью сигналов адреса. Обозначение микросхемы К155РЕ3: Из рисунка видно, что число ячеек этой ПЗУ составляет 32 (2^5) ячейки, разрядность каждой ячейки равна 8, т.е. один байт. Таким образом, емкость этого ПЗУ составляет 256 бит или 32 байта. Обобщенная структура и алгоритм работы микропроцессорной системы. Основным элементом является ЦПУ (микропроцессор). Работа микропроцессора и все системы синхронизируется генератором тактовых импульсов (ГТИ) который формирует тактовые импульсы с частотой fclk. Кроме микропроцессора в систему входят: память (ПЗУ и ОЗУ) и устройства ввода-вывода (УВВ) которые позволяют микропроцессорной системе общаться с внешним миром. Все устройства объединяются в систему с помощью трех магистралей (Шин). Обычно шины являются общими для всех устройств. Принцип «общей шины» - предполагает подключение одноименных входов и выходов всех устройств к одному и тому же проводнику. При работе по общим шинам обмен информацией должен происходить только между 2мя устройствами, входящими в систему. Остальные устройства в это время должны быть отключены и не мешать работе. Каждое из устройств имеет свой адрес, и с помощью сигналов адреса его можно активизировать. Если на шине адреса установить комбинацию соответствующую номеру устройства, то это устройство перейдет в активное состояние и с ним можно будет производить обмен информации. Остальные устройства в это время будут находиться в пассивном состоянии, и не будут мешать этому обмену. Адреса формируются микропроцессором и поступают по шине адреса на все устройства системы. Шина адреса одно направлена. Число разрядов в этой шине определяет адресное пространство микропроцессор. Шина данных предназначена для обмена данными между устройствами (двунаправлена). Разрядность шины данных определяется разрядностью микропроцессора. Шина управления (комбинированная) часть сигналов формируется в ЦПУ и подается на устройство, а часть наоборот. Обобщенный алгоритм работы МП системы. Работа микропроцессорной системы представляет собой циклическую последовательность следующих действий: 1. Считывание команды из памяти и формирование адреса следующей команды (выборка кода операции); 2. Считывание операндов из памяти, если это требуется по смыслу расшифрованной команды; 3. Выполнение команды; 4. Запись результатов выполнения команды в память, если это требуется по смыслу расшифрованной команды. Такая последовательность шагов называется машинным циклом (циклом команды, циклом шины). В свою очередь машинный цикл разбивается на машинные такты, длительность которых определяется тактовой частотой. 1978 г. – Intel i8086 – однокристальный 16-ти разрядный процессор. Он имеет 20-ти разрядную шину адреса. Этот процессор был разработан для однозадачного режима (MS-DOS). Режим его работы – реальный режим. Базовый процессор состоит из 3-х частей. Структурная схема базового микропроцессора i8086 Операционное устройство – устройство, в котором выполняются операции заданной команды. Устройство шинного интерфейса предназначено для организации обмена информацией между МП и другими устройствами по шинам. Устройство управления предназначено для формирования внешних и внутренних управляющих сигналов, которые обеспечивают правильность работы системы. Операционное устройство – блок регистров, состоящий из 16-ти разрядных регистров. AX, BX, CX, DX – Регистры общего назначения. При работе с байтами эти регистры могут делится на верхнюю и младшую половины. *H – high – верхняя, *L – low – нижняя. AX (AL) – аккумулятор. SP, BP – неделимые регистры; SP – Указатель стека, в нем всегда находится адрес входа в стек, BP – базовый, в нем могут хранится данные и адреса. SI, DI – индексные, используются для хранения адресов при индексной адресации. АЛУ – 16-ти разрядная комбинационная схема, которая может выполнять 4 действия арифметики над числами со знаком и без знака, а так же логические операции, включая сдвиги. С АЛУ связан регистр флагов: 16-ти разрядный регистр, 9 разрядов которого задействованы под флаги. Из этих 9-ти флагов, 6 является арифметическими, и 3 являются флагами управления. CF (Carry Flag) - Флаг переноса - он устанавливается, если в результате операции формируется перенос или заем из старшего разряда результата. PF (Parity Flag) - Флаг четности - он устанавливается, если в младшем байте результата сформировано четное количество двоичных единиц. AF (Auxiliary Flag) – Флаг вспомогательного переноса –устанавливается если при формировании результата произошел перенос из младшего полубайта в старший или заем из старшего полубайта в младший. Он используется в операциях над двоично-десятичными числами. ZF (Zero Flag) – Флаг нулевого результата – устанавливается, если результат операции равен нулю. SF (Signum Flag) – Флаг знака – принимает значение старшего разряда результата и в случае операций со знаком, характеризует его знак. OF (Overflow Flag) – Флаг переполнения – устанавливается, если в результате операции происходит перенос в знаковый бит или заем из знакового бита результата. Является индикатором переполнения – ситуации, когда результат выходит за пределы допустимого диапазона значений для чисел TF (Trap Flag) – Флаг трассировки (флаг пошагового режима). При установке TF в «1» процессор переходит в режим пошагового выполнения команд. Используется в программах отладчиков. IF (Interrupt-enable Flag) – Флаг разрешения прерываний. Если IF = 1, то процессор реагирует на прерывания, поступающие от внешних устройств. Если IF = 0, прерывания от внешних устройств запрещены. DF – (Direction Flag) – Флаг направления, который определяет порядок обработки цепочек данных (строк). Если DF = 0, обработка начинается в прямом направлении, от меньших адресов к большим. Если DF = 1, то обработка происходит в обратном направлении. Устройство шинного интерфейса. Включает в себя блок сегментных регистров, в который входят четыре 16-ти разрядных сегментных регистра CS, SS, DS, ES, предназначенные для хранения сегментных адресов памяти. Указатель команд IP – 16-ти разрядный регистр в котором хранится эффективный адрес следующей выполняемой команды. Сумматор адресов – устройство, которое формирует физический адрес ячеек памяти (полный адрес), который является 20-ти битовым. Его формирование происходит из логического адреса. Seg : EA 16p 16p PA 20p Буферные устройства предназначены для согласования выходов МП с внешними шинами системы. Регистры очереди команд – регистры, в которые помещаются извлекаемые из памяти команды. Число регистров – определяется самой длинной командой. Регистры в очереди команд позволяют организовать простейший конвейер, пока очередная команда выполняется в операционном устройстве (если в очереди есть свободное место) из памяти извлекается следующая команда и помещается в регистры очереди команд. Устройство хранения: включает дешифратор команд и микропрограммную память. Операции состоят из микроопераций. Управление операционным устройством происходит при помощи микрокоманд, заставляя МП на каждом числе выполнять микрооперации. Выполнение любой операции производится под управлением микропрограммы, которая представляет собой законченный набор микрокоманд. Эти микропрограммы на этапе изготовления МП заносятся в ПЗУ, которое называется микропрограммной памятью. Извлеченная из памяти команда из регистра очереди команд поступает на дешифратор. Команд на выходе дешифратора формируются сигналы, которые позволяют извлечь из микропрограммной памяти микропрограмму соответствующую расшифрованной команде. Работа МП с памятью. Адресное пространство - число адресов, которое может сформировать МП на шине адреса. Физический (полный) адрес PA ячеек памяти представляет собой 20 разрядный двоичный код на шине адреса МП. A19A18A17 A1A 0 000000 00000h 1111...11 2 20 1 FFFFFh Число адресов составляет 2 20 1024 1024 1.048.576 Максимальная емкость памяти составляет 2 20 8 2 20 байт 1Мб Процессор работает с памятью на основе принципа сегментации: 1. Вся память разбивается на сегменты длинной 216 64 Кб . Сегменты могут начинаться с адресов кратных 16: Только с таких адресов могут начинаться сегменты. Обратиться к сегменту памяти можно, указав его базовый (сегментный) адрес : SEG XXXX0h Сегментный адрес получается путем отбрасывания 4-х двоичных младших разрядов, равных 0, либо одного 16-тиричного младшего, равного 0. 2. Обратиться к ячейке внутри сегмента можно указав на сколько адресов она отстоит от начала сегмента (смещение - OFFSET) 3. К любую ячейке можно обратиться указав пару 16 разрядных адресов SEG : OFFSET Это логический адрес ячеек памяти. Физические 20-ти битовые адреса памяти, которые должны быть на шине адреса формируются в сумматоре адресов МП из логического адреса в соответствии с выражением: PA = SEG*16 + OFFSET, где РА – физический или полный адрес, SEG*16 – адрес начала сегмента, получающийся из базового адреса, OFFSET - смещение. Умножение на 16 делается для восстановления отброшенных нулей. Форматы данных Процессор может работать с разными форматами, но наиболее распространенные: - Byte Данные этого формата занимают отдельную ячейку памяти, следовательно, для обращения к таким данным, необходимо указать адрес этой ячейки. - Word Данные этого формата состоят из 2х байтов. Занимает в памяти 2 соседние ячейки, причем младший байт располагается по меньшему адресу. Адресом слова является адрес его младшего байта. - Double word Состоят из 4х байтов. Занимает 4 соседние ячейки, причем младший байт меньшего слова занимает меньший адрес. Адресом двойного слова является адрес младшего байта младшего слова. Программная модель МП системы Программная модель это доступные программисту на уровне команд ассемблера элементы МП системы. В модель входят элементы МП, память и устройства в\в. Организация прерываний в МП системе. Прерывание – некоторый сигнал, который заставляет МП прервать выполнение текущей программы и перейти на выполнение другой, более важной программы (обладающей большим приоритетом). Эта более важная программа называется процедурой или подпрограммой обслуживания прерываний, по окончании процедуры прерываний процессор должен автоматически возобновить выполнение прерванной программы. Для возврата основную программу должен запомнить адрес возврата (адрес возврата хранится в паре регистров CS:IP) и содержимое регистра флагов. Эти 3 регистра сохраняются в стеках автоматически. Если нужно сохранить содержимое других регистров, то необходимо использовать команду PUSH, по окончании процедуры прерывания содержимое 3х регистров автоматически восстанавливается по команде IRET (возврат из прерывания). Командой IRET заканчивается любая процедура обслуживания прерываний. Содержимое других регистров извлекается командой POP. В 32-разрядных МП есть команды PUSHA и POPA отправляют в стек \ восстанавливают все регистры. Прерывания делятся на 3 категории: - внешние; - внутренние (генерируемые МП); - программные. Структурная схема организации прерываний Внешние прерывания поступают от внешних устройств и делятся на: - немаскируемые прерывания NMI Запросы на немаскируемые прерывания поступают в случаях требующих немедленной реакции процессора. Эти прерывания не могут быть запрещены. В этом случае сигнал INTA не формируется (для ускорения обработки прерывания). - маскируемые прерывания INTR Поступают от внешних устройств через контроллер прерываний. Можно программно запретить (замаскировать). Для этого следует установить флаг IF в состояние 0. Если IF = 1, то МП принимает сигнал от внешнего устройства и обрабатывает его. В ответ МП формирует ответ подтверждение прерываний INTA. Контроллер прерывания, в случае если на его входы одновременно поступает несколько сигналов прерываний, выбирает сигнал, обладающий высшим приоритетом. Структурная схема контроллера прерываний: Внутренние прерывания формируются при возникновении особых ситуаций в работе МП. Прерывание тип 0: Возникает при выполнении деления, когда происходит деление на ноль или выбран не верный формат прерываний. Прерывание тип 1: Формируется когда установлен пошаговый режим работы МП. Прерывание тип 4: Прерывание по переполнению, возникает в случае если OF = 1. Прерывание тип 6: Возникает при выполнение неправильной команды. Программные прерывания, определяются пользователем с помощью команд INT n, где n-номер или тип прерывания. Прерывания вызывающие DOS-команды. Формируется сигнал прерывания и МП переходит на обслуживание этого прерывания. За каждым типом прерывания закреплена определенная подпрограмма его обслуживания, которая может находиться либо в ПЗУ, либо в ОЗУ. Каждая такая подпрограмма характеризуется логическим адресом соответствующим его началу. Пользователю не надо задавать адрес нужной подпрограммы, он использует только номер прерывания. Этот тип прерывания указывает на специальную таблицу указателей векторов прерываний, которая располагается в начальной области ОЗУ.