Переход полупроводниковых технологий в

реклама

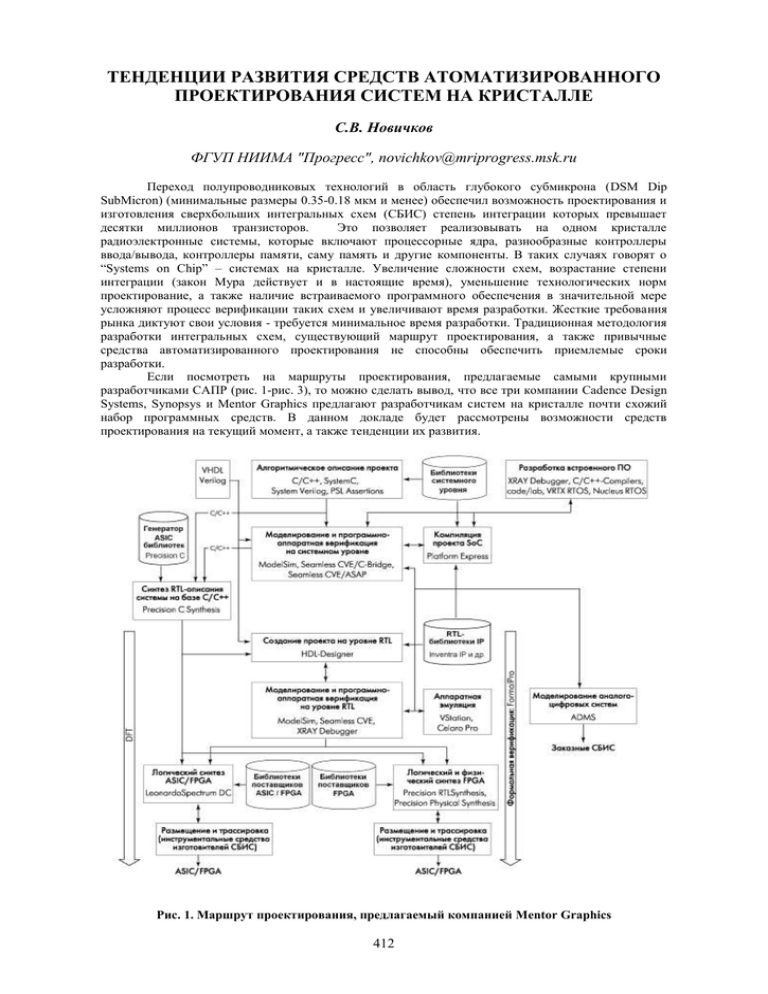

ТЕНДЕНЦИИ РАЗВИТИЯ СРЕДСТВ АТОМАТИЗИРОВАННОГО ПРОЕКТИРОВАНИЯ СИСТЕМ НА КРИСТАЛЛЕ С.В. Новичков ФГУП НИИМА "Прогресс", [email protected] Переход полупроводниковых технологий в область глубокого субмикрона (DSM Dip SubMicron) (минимальные размеры 0.35-0.18 мкм и менее) обеспечил возможность проектирования и изготовления сверхбольших интегральных схем (СБИС) степень интеграции которых превышает десятки миллионов транзисторов. Это позволяет реализовывать на одном кристалле радиоэлектронные системы, которые включают процессорные ядра, разнообразные контроллеры ввода/вывода, контроллеры памяти, саму память и другие компоненты. В таких случаях говорят о “Systems on Chip” – системах на кристалле. Увеличение сложности схем, возрастание степени интеграции (закон Мура действует и в настоящие время), уменьшение технологических норм проектирование, а также наличие встраиваемого программного обеспечения в значительной мере усложняют процесс верификации таких схем и увеличивают время разработки. Жесткие требования рынка диктуют свои условия - требуется минимальное время разработки. Традиционная методология разработки интегральных схем, существующий маршрут проектирования, а также привычные средства автоматизированного проектирования не способны обеспечить приемлемые сроки разработки. Если посмотреть на маршруты проектирования, предлагаемые самыми крупными разработчиками САПР (рис. 1-рис. 3), то можно сделать вывод, что все три компании Cadence Design Systems, Synopsys и Mentor Graphics предлагают разработчикам систем на кристалле почти схожий набор программных средств. В данном докладе будет рассмотрены возможности средств проектирования на текущий момент, а также тенденции их развития. Рис. 1. Маршрут проектирования, предлагаемый компанией Mentor Graphics 412 Рис. 2. Маршрут проектирования, предлагаемый компанией Synopsys Рис. 3. Маршрут проектирования, предлагаемый компанией Cadence Design Systems 413 Системный уровень. В настоящее время на системном уровне проектирования решаются следующие задачи: Анализ задач, целей создания “систем на кристалле”; определение их эксплуатационнотехнических и экономических характеристик таких как: быстродействие, максимальная потребляемая мощность, время разработки, стоимость. Создание и анализ высокоуровневых поведенческих моделей систем (включая каналы связи, приемо-передающие тракты и др.). Создание тестов для верификации “системы на кристалле”. Определятся разрядность данных, выбираются и анализируются алгоритмы создаваемых систем. Выбор архитектуры системы на основе накопленного опыта, проведенных ранее разработок, а также, анализа аналогичных проектов. При этом определяются требуемые IP-блоки: процессорные ядра, контроллеры, память, а также проводиться анализ экономических затрат на использование заимствованных IP-блоков. Декомпозиция проекта на программную и аппаратную части. Создание спецификации и тестов для программной и аппаратной частей проекта. Разработка отдельных специализированных тестов и спецификаций для IP-блоков, разрабатываемых в рамках проекта. До появления систем на кристалле и специализированного программного обеспечения, на данном этапе решался только ряд из представленных задач, а именно: анализ целей создания схемы, определение эксплуатационно-технических и экономических характеристик, создание тестов, разработка алгоритмов и создание поведенческой модели. Основными средствами для этого являлись языки программирования (С, С++) и пакет MathWorks Mathlab/Simulink. Недостатки такого подхода очевидны: Необходимость преобразования тестовых векторов для возможности их использования совместно с моделями на языке HDL HDL (Verilog, VHDL). Затруднен переход от блоков с плавающей десятичной точкой к блокам с фиксированной точкой. Невозможность моделирования алгоритма совместно с моделью на языке HDL. Отсутствие средств для разработки и анализа архитектуры систем. На сегодняшний день возможности пакета Matlab значительно увеличились за счет toolbox, разработанных MathWorks и сторонними разработчиками. Matlab позволяет выполнять моделирование Verilog/VHDL описаний (при наличии Modelsim компании Mentor), имеет широкие возможности по обработки сигналов (Signal Processing Toolbox), фильтрации сигналов (Filter Design Toolbox), моделированию телекоммуникационных систем (Communications Toolbox), а также позволяет работать с числами с фиксированной десятичной точкой (Fixed-Point Toolbox). Значительно упростить переход к моделям с фиксированной точкой можно посредством DSP Synthesis компании AccelChip. Данный продукт ориентирован на разработку DSP с использованием FPGA, но может быть использован для разработки и анализа алгоритмов с фиксированной точкой для систем на кристалле. Более широким набором возможностей обладают продукты SPW (Signal Processing WorkSystem) и HDS (Hardware Design System) компании CoWare. В отличие от Matlab, эти пакеты требует наличия Cadence NC-SIM для моделирования HDL модулей, а также позволяют моделировать высокочастотные блоки (требуется Cadence SpectreRF) и обеспечивают быстрый переход от моделей с плавающей точкой к моделям с фиксированной точкой и синтезабельным RTL описаниям этих блоков за счет дополнительных параметризованных библиотек. Выше описанные программные продукты не имеют возможностей разработки, анализа и верификации реализаций алгоритма на уровне архитектуры. Фактически, на данный момент также нужно иметь средства, позволяющие исследовать различные варианты архитектуры с учетом возможностей аппаратной и программной реализацией различных функций, использовать IP блоки, независимо от языка или уровня абстракции описания и разрабатывать новые IP блоки, анализировать эффективность использования памяти и загрузку шин, влияние времени считывания и записи, а также требуется проанализировать эффективность использования того или иного IP блока. Для этого требуется более специализированный чем С++, Verilog и VHDL язык, такой как SystemC. SystemC представляет собой набор классов расширяющий возможности стандартного языка С++ и обеспечивает описание статических, динамических событий, параллелизм, дополнительные типы данных, а также описание моделей на уровне RTL. Основные отличия SystemC от С++ следующие: SystemC поддерживает модули (иерархический элемент, содержащий модули или процессы). SystemС поддерживает три различных вида процессов, используемых для функционального описания. SystemC поддерживает однонаправленные и двунаправленные порты для взаимосвязи модулей. 414 SystemC поддерживает дополнительные типы данных для реализации различных уровней абстракции (логический тип (двух- и четырехзначная логика), тип с фиксированной десятичной точкой, знаковые/безнаковые типы, тип с произвольной и фиксированной разрядностью, векторные типы). SystemC поддерживает тактирование и понятие времени. SystemC имеет высокую скорость моделирования с точность до такта (cycle-base simulation). SystemC позволяет описывать проект на различных уровнях абстракций от высокоуровневой модели до RTL модели, функционирующей с точностью до цикла. SystemC поддерживает различные уровни описаний протоколов связи. SystemC позволяет сохранять результаты в виде диаграмм в форматы VCD, WIF, ISDB. Так как в основе SystemC лежит С++, то для работы с SystemC можно использовать привычные средства разработки ПО (gcc, gdb, Borland C++ Builder, Microsoft Visual C++). Однако на данный момент на рынке существуют специализированные средства для анализа архитектуры: System Studio компании Synopsys. ConvergenSC компании Coware. Seamless CVE компании Mentor Graphics. Visual Elite компании Summit design. Easi Studio компании Beach Solution. Winter Гомельского государственного университета им. Ф. Скорины. Выше указанные программные средства позволяют также решать задачи программноаппаратной верификации и позволяют начать разработку ПО значительно раньше. В привычном маршруте проектирования разработка ПО начинается после разработки модели аппаратной части на уровне RTL. При этом следует учитывать, что скорость моделирования RTL модели недостаточна для эффективной верификации и отладки программной части проекта, а разработка и верификация RTL модели занимает очень много времени. Для проведения более ранней программно-аппаратной верификации можно использовать виртуальный прототип (модель, описывающая поведение системы на уровне транзакций) созданный в этих программных средствах. По мере разработки можно заменять поведенческие блоки их реальными моделями. При этом возникает несколько очевидных проблем. Первая - среда, в которой происходит верификация проекта, должна поддерживать максимальное количество языков описания (С, С++, SystemC, Verilog, Verilog-AMS, VHDL-A, Matlab) и должна обеспечивать моделирование программной, цифровой и аналоговой частей. Вторая – увеличение времени моделирования при уменьшении уровня абстракции и использовании RTL моделей вместо моделей уровня транзакций. Решением этой проблемы может быть: использование готовых IP-блоков в виде изготовленных микросхем, расположенных на макетной плате; использование прототипов на основе FPGA; использование аппаратных ускорителей, таких как Palladium. Функциональный уровень. На функциональном уровне решается две основные задачи, а именно: разработка синтезабельной RTL модели устройства и верификация этой модели. Основой тенденцией в области разработки RTL моделей является повышение уровня абстракции. Так современные средства позволяют осуществлять синтез RTL моделей непосредственно из С/С++ описаний. Больших успехов в данной области достигли Mentor Graphics (Presision C Syntesys), Forte Design Systems, Tensilica, Celoxica. Также следует отметить значительное увеличение популярности среди разработчиков аппаратуры достаточного нового языка SystemVerilog. Некоторые отличия SystemVerilog 3.1a от Verilog2001: SystemVerilog поддерживает дополнительные типы данных: типы аналогичные С (int, typedef, struct, enum, union), ограниченная очередь, логический четырехзначный тип, тип bit, динамические типы данных (строки, классы, динамическая очередь, динамические массивы). SystemVerilog поддерживает приведение (преобразование типов); в SystemVerilog добавлены дополнительные операторы (оператор группового равенства/неравенства), потоковые операторы, оператор принадлежности множеству; в SystemVerilog расширенны возможности функций и процедур (добавлен оператор foreach, расширенны операторы циклов, добавлены операторы перехода: return, break, continue), расширены возможности оператора fork-join для организации конвейеров; в SystemVerilog добавлены “финальные блоки” (блоки, которые выполняются один раз в конце моделирования, т.е. антипод initial); в SystemVerilog расширено управление событиями и последовательностями событий; добавлен импорт/экспорт функций посредством DPI (Direct Programming Interface); добавлен объектно-ориентированный механизм, классы, указатели; 415 добавлено автоматическое создание тестовых сигналов, с использованием случайных констрейнов; добавлен механизм утверждений. Следует заметить, что верификация проекта является наиболее трудоемкой задачей при разработки систем на кристалле и занимает более 50 процентов времени всей разработки. Процесс верификации усложняется наличием в современных СБИС различных типов блоков: процессоров, высокоскоростных интерфейсов ввода-вывода, встроенной памяти, аналоговых, смешанных и СВЧ блоков, DSP, программного обеспечения, взаимодействующего с операционной системой реального времени. Еще более усложняет процесс верификации наличие IP блоков сторонних производителей. В связи с этим средства верификации функционального уровня последние несколько лет претерпевают значительные изменения и позволяют решать следующие задачи: Формальная верификация. Вместо многократного моделирования схемы при различных тестовых воздействиях выполняется сопоставление проектного решения с некоторым эталонным решением. Формальная верификация может эффективно использоваться для проверки синтезированной модели, когда в качестве эталонной модели вступает исходное RTL описание. Часть программ формальной верификации позволяют также сравнивать RTL и SPICE модели. Наиболее известными средствами формальной верификации являются Synopsys Formality/ESP, Cadence Conformal, FormalPro компании Mentor Graphics, 0-in Confirm, 0-in Search. Верификация на уровне утверждений. Данная методология верификации подразумевает расстановку внутри моделируемого кода "закладок", проверяющих работу тех или иных функций по мере их срабатывания, не дожидаясь распространения следствия данного срабатывания на выход схемы. В результате ошибка идентифицируется значительно быстрее и проще. Причем можно практически мгновенно определить ее истинную причину и в то же время существенно снизить сложность и объем тестовых моделей. Основными языками описания утверждений являются OpenVera Assertions (OVA) , Property Specification Language (PSL) и SystemVerilog. На первых этапах становления утверждений для работы с ними приходилось использовать специализированное ПО. На текущий момент поддержка утверждений заложена в большинстве программ моделирования. Проверка написания кода на соответствие заданному стандарту кодирования для Verilog/VHDL/SystemVerilog, то есть на основе предопределенных или созданных пользователем правил, средства позволяют разработчику значительно расширить возможности при проверке HDL описаний на наличие потенциальных ошибок, которые могут возникнуть на этапах моделирования, синтеза, тестирования, при многократном использовании и при переходе с RTL уроня на вентильный уровень: нахождение ошибок, связанных, с использованием нескольких схем синхронизации (clock domains), проверка на пригодность для моделирования, синтеза, временного анализа. Наиболее известные программные средства: Synopsys Leda, Cadence HAL и Mentor DesignAnalyst. Логический уровень. На данном этапе на основе RTL кода синтезируется список цепей в базисе выбранной технологической библиотеки с использованием средств автоматизированного синтеза. Основной тенденцией в сфере разработки средств логического синтеза является учет эффектов субмикрона на этапе синтеза и улучшение работы при синтезе больших проектов. Современные средства позволяют не внося никаких изменений в требования по функциональности, быстродействию, энергопотреблению и физическим параметрам проекта встраивать структуры для самотестирования, структуры повышающие тестируемость, а также позволяют автоматически генерировать тесты с высоким процентом сканирования (Cadence Encounter Test, Mentor FastScan/ FlexTest / LBISTArchitect, Synopsys DFT Compiler/ TetraMAX ATPG). Также стоит отметить поддержку новых языков (хоть и с некоторыми ограничениями) Verilog 2001, SystemVerilog, SystemC средствами автоматического синтеза. После логического синтеза выполняется временной статистический анализ с целью определения задержек, временных характеристик, падения напряжения, целостности сигнала, а также проводится анализ потребляемой мощности. Статистический временной анализ может выполняться как средствами программы логического синтеза, так и специализированным ПО. Наибольшую популярность для выполнения статического временного анализа приобрел продукт Synopsys Prime Time, став де-факто стандартом. Физический уровень (разработка топологии). Разработка топологии цифровых схем с технологическими нормами менее 0,18 мкм должна начинаться с разработки физического прототипа. Физический прототип-представление SoC, ASIC или отдельного блока, которое доступно до получения финальной топологии и содержит достаточную физическую информацию, чтобы достаточно точно оценить основные параметры системы, такие как временные характеристики, паразитные параметры, занимаемую площадь, потребляемую мощность. При этом физический прототип должен быть достаточно точным, чтобы проектирование топологии на его основе обеспечивало реализацию в соответствие с проектными нормами. Таким образом, задача построения 416 физического прототипа является комбинацией задач, решение которых необходимо для последующей передачи данных на физическую реализацию, где выполняются наиболее длительные по времени выполнения процедуры разработки топологии и ее верификация. Как правило, при создании виртуального прототипа решаются следующие задачи: размещение на кристалле; предварительная трассировка; анализ задержек и временной анализ; анализ качества сигналов; физический синтез; физическая оптимизация; синтез синхроцепей; планирование и синтез цепей питания и земли; анализ падения напряжения (IR drop); проверка целостности сигнала (Signal Integrity); анализ перекрестных помех (Crosstalk). После разработки и проверки физического прототипа выполняется разработка топологии. Средства используемы для финального размещения и трассировки являются самыми дорогостоящими во всем маршруте проектирования. По окончании разработки топологи проводиться ряд проверок: соответствие топологии нормам проектирования (DRC-Design Rule Check); соответствие топологии списку цепей или принципиальной схеме (LVS-Layout vs Schematic); экстракция паразитных элементов (RCX-Resistor Capasitor eXtract); временной анализ с учетом реальных данных топологии; Разработка аналоговых блоков. За последние несколько лет существенных изменений в возможностях программных средств для разработки аналоговых блоков не произошло. Стоит отметить широкое распространение средств моделирования на основе табличных методов. Как правило, моделировщики на базе табличных методов позволяют увеличить скорость моделирования до 10 раз, сохраняя при этом приемлемую точность по сравнению со SPICE-подобными моделировщиками. Средства разработки топологии аналоговых схем, а именно средства автоматического размещения и трассировки позволяют упростить разработку топологии, но не позволяют полностью автоматизировать данный процесс. В завершении доклада хотелось бы выделить компании - разработчиков САПР, представленные на отечественном рынке. Во-первых, следует отметить три компании предлагающие программные продукты охватывающие весь маршрут проектирования систем на кристалле: Cadence Design Systems, Synopsys (дистрибьютор в Росси компания Alt-s), Mentor Graphics Technologies (официальный представитель в России компания Megrateс). Кроме этих трех компаний, являющихся мировыми лидерами в области разработки средств проектирования, существуют компании, предлагающие программные продукты для ограниченного круга задач и имеющие своих дистрибьюторов или представительства в России: Simplicity (логический синтез), Summit Design (программно-аппаратная верификация, архитектурный анализ системы), Aldec (моделирование Verilog/VHDL/SystemVerilog/SystemC, аппаратные средства для ускорения моделирования). Из отечественных разработчиков программных продуктов можно выделить: DeverSYS (Reuse Checker Программный комплекс проверки IP ядер), Гомельский государственный университет им. Ф. Скорины (Winter - интегрированная среда сквозной совместной разработки аппаратного и программного обеспечения) и Московский институт электронной техники (AvoCAD-система для схемотехнического проектирования и моделирования ИС). ЛИТЕРАТУРА 1. 2. 3. 4. 5. 6. Лохов А. Функциональная верификация СБИС // Электроника: Наука, Технология, Бизнес. - 2004. - № 1. - С. 58-62. Кравченко В., Радченко Д. Виртуальное прототипирование // Электроника: Наука, Технология, Бизнес. - 2003. - № 7. - С. 34-37. Кравченко В., Радченко Д. САПР компании Synopsys // Электроника: Наука, Технология, Бизнес. - 2003. - № 5. - С. 31-33. Лохов А. Средства проектирования СБИС компании Mentor Graphics // Электроника: Наука, Технология, Бизнес. - 2003. - № 7. - С. 30-33. Сайт компании Alternative Solution http://www.alt-s.ru/. Сайт компании Cadence Design System http://www.cadence.com. 417