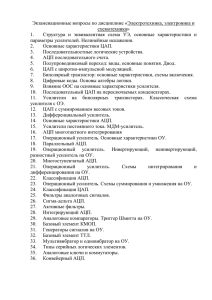

Функциональные устройства комбинационного типа.

реклама

Министерство образования Российской Федерации

Алтайский государственный технический университет

им. И.И.Ползунова

Схемотехника

Барнаул

2008г.

Содержание

Модуль 1. Аналоговая электроника.

ТЕМА 1. Источники питания электронной аппаратуры.

ТЕМА 2. Стабилизаторы напряжения и тока.

ТЕМА 3. Методы линейной обработки аналоговых сигналов .

ТЕМА 4. Генераторы электрических сигналов

ТЕМА 5. Линейно-импульсные схемы.

Модуль 2. Введение в цифровую схемотехнику. Функциональные

устройства комбинационного типа.

ТЕМА 6. Логические функции, аксиомы алгебры логики, минимизация

логических функций. Цифровые коды и операции над ними.

ТЕМА 7. Базовые элементы цифровых ИС: ТТЛ, ЭСЛ, КМОП.

ТЕМА 8. Мультиплексоры и демультиплексоры. Универсальные

логические модули на основе мультиплексоров. Компараторы

ТЕМА 9. Шифраторы и дешифраторы. Сумматоры и полусумматоры.

ТЕМА

10.

Арифметико-логические

устройства

(АЛУ).

Программируемые логические матрицы (ПЛМ). Матричные умножители

Модуль 3. Функциональные узлы последовательного типа.

ТЕМА 11. Триггерные схемы.

ТЕМА 12. Регистры.

ТЕМА 13. Счетчики импульсов. Синтез счетчиков.

Модуль 4. Цифровые запоминающие устройства. Устройства сопряжения

аналоговых и цифровых схем.

ТЕМА 14. Основные сведения. Основные структуры ЗУ

ТЕМА 15. Постоянные запоминающие устройства (ПЗУ). Оперативные

запоминающие устройства (ОЗУ).

ТЕМА 16. Флэш-память. Перспективные запоминающие устройства.

ТЕМА

17.

Цифроаналоговые

Аналогоцифровые преобразователи (АЦП).

преобразователи

(ЦАП).

Модуль 2.

Введение в цифровую схемотехнику.

Функциональные устройства комбинационного типа.

Тема 6. Логические функции, аксиомы алгебры логики, минимизация

логических функций, построение карт Карно. Инвертор, дизъюнктор,

конъюнктор, условное обозначение, таблица истинности. Представление

логических элементов в электронной аппаратуре, логические операции,

реализуемые данными элементами, базовые логические элементы. Цифровые

коды и операции над ними.

6.1 Элементарные логические функции

1) Конъюнкция (операция “и”, логическое умножение.) Конъюнкция

нескольких переменных равна 1 лишь тогда, когда все переменные равны 1.

Конъюнкция обозначается в виде произведения у = х1·х2, или у = х1х2, или у =

х1Λ х2.

Обозначение элемента в схеме приведено на рисунке 2.1

Рисунок 2.1 – Конъюнктор

Таблица соответствия для конъюнкции:

х1

х2

у=х1·х2

0

0

0

0

1

0

1

0

0

1

1

1

Таблица 2 – Конъюнкция

2) Дизъюнкция (операция “или”, логическое сложение.)

Дизъюнкция нескольких переменных равна

1, если хотя бы одна из

переменных равна 1.Дизъюнкция обозначается в виде суммы:

или у = х1Vх2..

у = х 1+х2,

Обозначение элемента в схеме приведено на рисунке 2.2.

Рисунок 2.2 – Дизъюнктор

Таблица соответствия для дизъюнкции:

х1

х2

у=х1+х2

0

0

0

0

1

1

1

0

1

1

1

1

Таблица 3 – Дизъюнкция

3)Инверсия (операция “не”, логическое отрицание). Обозначение

элемента в схеме приведено на рисунке 2.3:

Рисунок 2.3 – Инвертор

Таблица соответствия для инверсии:

х

у= x

0

1

1

0

Таблица 4 – Инверсия

Возможны

комбинированные

операции.

Примеры

элементов,

выполняющих такие действия приведены на рисунке 2.4

Рисунок 2.4 – Комбинированные логические элементы

4) Исключающее “или” – функция равна 1,когда только одна переменная

равна 1. Обозначается значком

5) Сумма по модулю 2 - функция равна 1,когда нечетное число

переменных равно 1,

функция равна 0 ,когда четное число переменных равно 1.

Функция обозначается: в виде у = Σmod2 = х1 х2 ... хn

Для двух переменных

Σmod2 совпадает с функцией

исключающее

“или”.

Для трех переменных в таблице 4 приведены данные для функций

“исключающее или” и ”сумма по модулю 2”.Они уже неполностью

совпадают.

х1

х2

х3

у1=х1

х2

х3

у2=х1 х2

х3

0

0

0

0

0

0

0

1

1

1

0

1

0

1

1

0

1

1

0

0

1

0

0

1

1

1

0

1

0

0

1

1

0

0

0

1

1

1

0

1 !!!

Таблица 5 – Сравнение функций

Система логических функций называется функционально полной, если

используя

только эти

функции можно реализовать любые другие.

Функционально полными являются системы:

1) “и”, ”или”, ”не”,

2) “и”, ”не”,

3) “или”, ”не”.

Порядок выполнения логических операций: “не”, ”и”, ”или” (если нет

скобок).

6. 2. Алгебра логики (алгебра Буля)

Алгебра

логики

изучает

связь

между

переменными

принимающими только два значения:

"1" - логическая единица или "0" - логический нуль.

параметрами,

6.2.1. Основные понятия алгебры логики

Закон исключенного третьего

Если х 1, то х = 0, если х 0, то х = 1.

Логическая функция

у=f(х1,х2,...,хn) задана, когда каждому набору х

однозначно сопоставляется

переменными равно N 2

2

у.

Количество функций, образуемых n

n

.

Если n = 1, то N = 4:

у1 = 0,

у2 = 1,

у3 = х,

у4 = /х.

Для двух переменных

n = 2 и N = 16.

В таблице 6 приведены некоторые из возможных функций при n=2

х1

х2

у1

у2

у3

у4

0

0

0

0

1

0

0

1

1

0

1

1

1

0

1

0

1

1

1

1

1

1

0

0

Таблица 6 – Логические функции двух переменных

6.1.3. Аксиомы алгебры логики

х+0=х

х0=0

х 0=х

х+1=1

х1=х

х 1=х

х+х=х

хх=х

х х=0

хх=0

х+х=1

х х=1

Таблица 7 – Аксиомы алгебры логики

Их можно проверить подставляя вместо х 0 или 1.

6.2.4. Правила Де-Моргана:

Любые логические функции могут быть построены с использованием только

элементов "И-НЕ" или только элементов "ИЛИ-НЕ". Переход от операции

"И" к операции "ИЛИ", а также обратный переход осуществляется с

помощью законов дуальности (теорема де Моргана):

В предыдущей строке показана типичная ошибка,когда полагают,что

произведение инверсий равно инверсии произведения этих же переменных.

Закон поглощения

х1+х1х2 = х1(1+х2) = х11 = х1 х1 “поглощает” х2

6.2.5. Минимизация путем алгебраических преобразований

Пусть функция задана в виде таблицы:

х1

х2

х3

У

0

0

1

1

0

1

1

1

1

1

1

1

Таблица 8 – Функция, заданная в виде таблицы

Каждая строка таблицы представляет собой конъюнкцию переменных.

Если значение переменной в данной строке равно 0, то переменная берется с

инверсией.

Реализация полученного выражения с помощью элементов ”2и-не”:

Рисунок 2.5 – Реализация функции, заданной таблицей

6.1.6. Минимизация с помощью диаграмм Карно

Правило построения диаграммы Карно

Для n переменных заполняется прямоугольная таблица, содержащая 2n

клеток так, чтобы в соседних клетках конъюнкции отличались не более, чем

одним сомножителем.

Если минимизируемая функция при данном наборе переменных равна 1

, то в соответствующую клетку ставится

1 (нули можно не ставить). В

прямоугольной таблице единицы обводятся контурами и записывается

функция в виде суммы произведений, описывающих контуры. Число клеток

внутри контура 2к (1,2,4,8...).

Следует покрыть все единицы возможно меньшим числом возможно

более крупных блоков. Каждому блоку сопоставляется конъюнкция,

записываемая следующим образом:

1)Если блок целиком лежит в единичной области переменной х i , то она

включается в конъюнкцию без инверсии, если в нулевой области, то с

инверсией.

2) Если блок делится точно пополам между нулевой и единичной

областями хi ,то хi в конъюнкцию не включается (склеивание по хi).

Других расположений правильно выбранного блока быть не может.

Например:

а) для двух переменных ,заданных таблицей

б) для трех переменных:

6.3. Цифровые коды

6.3.1. Двоичный позиционный код

В обыденной жизни применяется

десятичная система счисления, в

которой используется 10 цифр от 0 до 9 и число представлено как сумма

степеней числа 10. Например, число 1407 представляет сокращенную запись

суммы 1*103 +4*102 +0*101 +7*100. В цифровой электронике чаще всего

используется двоичная система счисления.

Двоичная (бинарная) система основана на степенях числа 2, оперирует

только с двумя символами (цифрами): 0 и 1. Двоичная цифра (символ 0 и 1)

является единичной элементарной информацией, которая называется битом.

Биты объединяются в слова определенной длины, слово длиною в 8 бит

называется байтом, В настоящее время наиболее распространены системы с

байтовой организацией данных. Поскольку в двоичной системе используется

два символа, она имеет основание 2 и значения, которые должны быть

приписаны отдельным позициям (веса), являются степенями числа 2.

Целые числа без знака в двоичной системе счисления представляются

следующим образом:

am2m+am-12m-1+....+a4 24+a3 23+a2 22+a1 21+a0 2° ,где ai=0,или 1

Наименьшая значащая цифра (младший разряд числа) здесь расположена

справа, а слева последовательно каждая цифра представляет собой более

высокий разряд, более высокую степень числа 2. Например, код 1011

представляет число

1*23+0*22+1*21+1*20=8+2+1=11

При сдвиге целого числа на одну позицию влево производится

умножение на два, а при сдвиге на одну позицию вправо производится

деление на 2, что обусловлено основанием этой системы счисления.

Перевод чисел из двоичной системы счисления в десятичную

Перевод выполняется путем сложения весов тех разрядов, в которых

имеются единицы. Например:

Веса

27 26 25 24 23 22 21

Переводимое число

1

0

0

1

1 0

1

20

1

= 128 + 0 + 0 + 16 +8 + 0 + 2 + 1 =155

6.3.2. Двоично-десятичный код

Двоично-десятичный код представляет собой десятичный код, каждый

разряд которого представлен четырьмя разрядами двоичного кода.

Например:

4610=0100.01102-10 ;

84210=1000.0100.00102-10

Он используется для выдачи информации на цифровые индикаторы. На

каждый

индикатор

поступает

четырехразрядный

двоичный

код

и

высвечивается одна из цифр десятичного кода.

6.3.3. Восьмеричный код

Двоичный код для представления больших чисел требует очень

большого числа двоичных разрядов ,состоящих из единиц и нулей. С такими

кодами человеку работать затруднительно и легко возникают ошибки. Для

облегчения работы двоичные коды можно представить в восьмеричной

форме: каждые три разряда ,начиная с младшего, записываются в виде

десятичной цифры. Так как самое большое число, которое можно записать

тремя двоичными разрядами равно 7(1112=710),то восьмеричные коды

записываются цифрами от 0 до 7.Например, 101.1102=568 ,11.1002=347.

6.2.4. Шестнадцатеричный код.

Он образуется аналогично восьмеричному, но объединяются четыре

разряда ,начиная с младшего, и записываются в виде одного символа. Самое

большое число, которое можно записать четырьмя двоичными разрядами

11112=1510,что составляет уже 2 десятичных цифры ,а представить нужно в

виде одного символа. Поэтому вводятся новые символы для представления

чисел от 10 до 15.Для этого используются буквы латинского алфавита

А,B,C,D,E,F

Десятичный код

0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15

Шестнадцатеричный код

0 1 2 3 4 5 6 7 8 9 A B C D E F

Например:

1010.01112=A716 (чаще используется обозначение A7H) ,

11.0111.01012=375H , 1111.1011.10012=FB9H .

Шестнадцатеричный код чаще всего используется для общения человека

и ЭВМ на уровне кодов.

6.2.5 Код Грея.

Рассмотренные выше коды называются позиционными так как вес

каждого

разряда

определяется

его

положением

(позицией)

в

рассматриваемом коде. Так в двоичном позиционном коде 1 в крайнем

правом разряде представляет число 20 ,в следующем разряде-21 и т.д. Поэтому

двоичный позиционный код еще называют кодом 8421. В цифровых датчиках

применение этого кода может привести к большим ошибкам. В цифровых

датчиках перемещения или угла поворота единица изображается отверстием

в маске, через которое проходит световой луч, а ноль изображается

непрозрачным участком маски.

“ 10 “

“2 “

Код Грея

0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

0000

0001

0010

0011

0100

0101

0110

0111

1000

1001

1010

1011

1100

1101

1110

1111

0000

0001

0011

0010

0110

0111

0101

0100

1100

1101

1111

1110

1010

1011

1001

1000

Таблица 9 – Сравнение двоичного кода и кода Грея

Если пользоваться двоичным, то при перемещении маски, например, из

положения 0111 в положение 1000 из-за неодновременной смены трех “1” на

три “0” могут кратковременно возникнуть коды 1100, 1010, 1101 и т.д.,

которые

значительно

отличаются

как

от

предыдущего,

так

и

от

последующего значения и погрешность становится непредсказуемой. Все

проблемы снимаются при использовании кода Грея, в котором при

увеличении кода на 1 каждый раз изменяется только один из разрядов. Код

Грея используется только для снятия информации с датчика. Для дальнейшей

обработки информации код Грея переводится в двоичный позиционный по

следующему алгоритму:

Каждый i-й, считая с левого старшего, разряд двоичного позиционного

кода любого числа равен сумме по модулю 2 i-го и всех более левых

разрядов этого числа, представленного кодом Грея.

6.4. Арифметические операции над двоичными кодами

6.4.1. Сложение

Сложение двоичных кодов производится побитно на основе следующих

соотношений: 0+0=0; 0+1=1; 1+0=1; 1+1=0 и 1-в перенос (в результате 10).

Например:

1

+9

перенос

111

+1001

5

0101

14

1110

переносы

+7

+0111

1

0001

8 1000

6.4.2. Вычитание

Это действие можно выполнять так же как и в десятичных кодах,

занимая 1 старшего разряда (производить заем):

1

-

10

заем

-1010

5

0101

5

0101

Но для многоразрядных кодов процедура очень осложняется, когда

приходится занимать не из соседнего старшего разряда а из более старших

разрядов. Поэтому в цифровой технике вводится понятие дополнительного

кода, который позволяет совершенно одинаково выполнять операции

сложения и вычитания. Для указания знака кода используется самый

старший его разряд. В положительном коде старший разряд равен нулю, а в

отрицательном – единице. Дополнительный код положительного числа

совпадает

с

его

прямым

(обычным)

кодом.

Дополнительный

код

отрицательного числа получается путем инверсии прямого кода и добавления

к результату единицы.

Например: прямой и дополнительный код числа +5 равен 0101,

дополнительный код числа –5 равен 0101 +1=1010+1=1011.

Старший разряд “1” указывает, что код представляет отрицательное

число. Код называется дополнительным потому, что он дополняет nразрядный

прямой

код

до

значения

2n.В

приведенном

примере

0101+1011=100002=24.

Имеется

,несколько

другой

быстрее

способ

приводящий

определения

к

цели.

дополнительного

Разряды

прямого

кода

кода

переписываются справа налево, начиная с младшего разряда D0 до первой

встретившейся 1,остальные разряды инвертируются.

Например 10110пр=01010доп.

Вычитание двоичных кодов сводится к сложению положительных и

отрицательных кодов и выполняется как сложение их дополнительных кодов.

При выполнении этой операции очень важно проследить чтобы результат

действия над кодами не исказил знаковый разряд. Поэтому должен быть

определенный запас нулевых разрядов, расположенных после знакового

разряда. В нижеприведённых примерах операнды занимают всего 4 разряда

,но будем использовать восьмиразрядные коды.

Рассмотрим различные ситуации при вычитании.

1) Вычислим в двоичных кодах результат операции 7-5=7+(-5)

Определим

дополнительный

код

–5=-00000101пр=11111011доп.

Тогда 710-510=00000111доп+11111011доп=1.00000010доп=00000010пр=210

Возникший перенос 1 в разряд D8 отбрасывается. Знаковый разряд

D7=0,поэтому результат – положительное число 2 ,у которого прямой код

такой же ,как и дополнительный.

2)

Определим

результат

операции

510-710=

=00000101пр-00000111пр=00000101доп+11111001доп=11111110доп=-00000010пр=210

ЗдесьD7=1,результат

отрицательный,

поэтому

дополнительный

код

переводится в прямой. Это выполняется по тому же правилу ,что и перевод

прямого кода в дополнительный.

3)

Найдём

–510-710=11111011доп+11111001доп=1.11110100доп=-

00001100пр=-1210.

6.3.3. Умножение

Операция выполняется также как и для десятичных кодов :множимое

умножается на каждый разряд множителя и результаты складываются со

сдвигом. Можно умножать, начиная с младших разрядов со сдвигом влево,

или со старших со сдвигом вправо.

610* 710

111

111

* 110

*110

000

111

111

111

* 111

*

1010102=4210

000

101010

Числа со знаком умножаются в прямом коде, а знак определяется как сумма

по

модулю

2

знаковых

разрядов.

6.3.4. Деление

Выполняется как вычитание со сдвигом. Например:

18:6=3

22:4=5,5

10010 : 110

- 110

10110 : 100

11

-100

110

110

-110

-100

101,1

000

10,0

-100

000

Здесь дробная часть представляет отрицательные степени числа 2.

Например: степени 2 2 1 0 -1-2

Код

1 1 0, 1 1=4+2+0,5+0,25=6,75.

ТЕМА 7. Базовые элементы цифровых ИС: ТТЛ, ЭСЛ, КМОП –

основные характеристики и параметры и их сравнительная характеристика.

7. Логические интегральные схемы.

7.1. Представление логических переменных в электронной аппаратуре

Большинство

цифровых

микросхем

относятся

к

потенциальным

микросхемам, в которых сигнал на их входе представляется высоким или

низким уровнем напряжения. Этим уровням соответствуют логические

значения 1 и 0. Существуют два способа представления логических

переменных:

1. Высокий уровень напряжения - 1, низкий - 0 (положительная логика).

2. Высокий уровень напряжения - 0, низкий - 1 (отрицательная логика).

Логические операции, выполняемые микросхемами, обычно указывают

для положительной логики.

7.2. Базовые логические элементы

Разработкой каждой серии цифровых ИС начинается с базового

логического элемента. Так называют элемент, который лежит в основе всех

микросхем серии: комбинационных(логических), триггеров, счетчиков и др.

Как правило, базовые логические элементы выполняют операции "И-НЕ"

либо "ИЛИ-НЕ". Принцип построения базового элемента, способ управления

его

работой,

напряжение

питания

и

другие

параметры

являются

определяющими для всех ИС данной серии. Широко распространены ИС,

построенные на базовых элементах транзисторно-транзисторной логики

(ТТЛ)

7.2.1. Технология ТТЛ

Базовый элемент ТТЛ (рис. а) строится на основе многоэмиттерного

транзистора VT1, обеспечивающего коньюнкцию входных сигналов Xi, и

сложного инвертора на транзисторах VT2-:VT4, выполняющего операцию

"НЕ".

Когда на все входы Xi многоэмиттерного транзистора поданы сигналы 1

(высокий потенциал, сравнимый с +E), все его эмиттерные переходы

закрыты. Ток от источника через резистор R1 и коллекторный переход VT1

поступает на базу VT2. Транзистор VT2 открывается до насыщения и

открывает VT4 также до насыщения. Транзистор VT3 в это время закрыт,

поскольку напряжение на коллекторе открытого транзистора VT2 мало. Диод

VD служит для повышения порога открывания транзистора VT3.

Рисунок 2.6 – Базовый элемент ТТЛ

Таким образом, рассмотренный элемент ТТЛ выполняет логическую

операцию

"И-НЕ" ( 1 i n ).

Для ограничения тока через открытый транзистор VT3 при случайном

коротком замыкании выхода элемента включен резистор R4.

В состав некоторых серий цифровых ИС ТТЛ входят логические

элементы без коллекторной нагрузки выходного транзистора VT4 - элементы

с "открытым" коллектором. Они предназначены для работы с внешней

нагрузкой в виде индикаторных приборов, светодиодов и т.д.

Если какие либо из входов многоэмиттерного транзистора никуда не

подключены, то это воспринимается элементом как подача на эти входы 1,

так как тока в цепи неподключенного эмиттера нет.Поэтому, например,

элементы "И-НЕ" ("ИЛИ-НЕ") можно использовать как простые инверторы,

подавая инвертируемый сигнал соединяя все входы вместе..В схеме

"И-НЕ" сигнал можно подавать только

на один из входов,оставляя

остальные неподключенными(рис.2-7).

Рисунок 2.7 – Использование элементов “и-не’, ’или-не’ как инверторов

Вход

ИС

транзистор-транзисторной

помощью многоэмиттерного транзистора.

логики(ТТЛ)

реализуется

с

Рисунок 2.8 – Многоэмиттерный транзистор

При подаче хотя бы на один из эмиттеров уровня “0”, ток из выходной

цепи Rн переключается во входную цепь и на выходе устанавливается “0”.

Если на все входы подать уровень “1”, тогда во входной цепи тока не будет,

он пойдет через Rн и на выходе будет “1”. Данная схема выполняет операцию

“и”.

Если на входы ничего не подавать, то тока во входной цепи также не

будет и на выходе появится “висячая 1”. При соединении многоэмиттерного

транзистора и сложного инвертора образуется элемент “и-не”.

7.2.2. Пути повышения быстродействия ТТЛ схем

1) Нелинейная обратная связь (НОС)

Рисунок 2.9 – НОС с помощью диода

При подаче на вход напряжения единичного уровня транзистор

открывается и напряжение на выходе начинает падать. В какой-то момент

потенциал φа < φb , следовательно VD открывается и дальнейшего насыщения

не происходит. Поэтому при подаче Uвх=0 транзистор закрывается

значительно быстрее.

2) Применение диодов и транзисторов Шоттки.

ДШ – диод Шоттки (диод на горячих носителях).

Рисунок 2.10 – Условное обозначение и характеристика диода Шоттки

В них выпрямительный контакт расположен на границе между металлом

и полупроводником, а носители зарядов и в полупроводниках, и в металле –

электроны. Неосновных носителей нет.Соединение ДШ + транзистор

образуют транзистор Шоттки (555 серия).

7.2.3. Технология КМОП

В качестве инверторов можно использовать МОП транзисторы ,но р- и

n-канальные цифровые элементы оказались непрактичными как базовые для

массовых микросхем прежде всего из-за низкого быстродействия. Действительно, при Rс=100кОм и емкости нагрузки Сн=30 пФ время отключения

составит t1,0 =2,2RcCн=6,6 мкс,что соответствует максимальной частоте

входных импульсов 150 кГц.

Увеличить быстродействие на порядок позволяет последовательное

(столбиком) соединение р и n-канальных МОП-транзисторов. Тогда резистор

Rc в схеме не нужен, а заряд и разряд паразитных нагрузочных емкостей

будет происходить через относительно небольшие сопротивления р и nканалов .

С помощью металлизации поверхности кристалла элементы структуры

соединяются в схему инвертора DD1(рис.в) . К затворам присоединен

защитный стабилитрон VD1 ,без него вход инвертора будет пробит

статическим электричеством

Цифровые микросхемы должны быть крайне устойчивы к таким явлениям, как пробои от статического или наведенного от силовых сетей

электричества. Прежде всего защита гарантируется их структурой.

На рисунке г показана полная эквивалентная схема инвертора КМОП.

Стоковое напряжение (плюс источника питания) подключается на nподложку.

в

г

Рис.2-11

Упрощенная

и

полная

схемы

инвертора

на

КМОП

транзисторах

Конденсатор С

символизирует входную емкость инвертора. Как

правило, она составляет от 5 до 15 пф. Диоды VD1 – VD3 защищают

изоляцию затвора от пробоя. Диод VD1 имеет пробивное напряжение 25 В,

VD2 и VDЗ-50 В. Последовательный резистор R=200 Ом... 2 кОм не

позволяет скачку тока короткого замыкания передаваться в незаряженную

входную

емкость

С.

Тем

самым

защищается

выход

предыдущего

(управляющего) инвертора от импульсной перегрузки. Диоды VD4-VD5

защищают выход инвертора от пробоя между n+ и p+ областями .Диод VD6

защищает канал от ошибочной перемены полярности питания.

7.2.4. ЭСЛ технология

Цифровые микросхемы эмиттерно-связанной логики (ЭСЛ) имеют

наибольшее

быстродействие,

достигшее

в

настоящее

время

субнаносекундного диапазона. Особенность ЭСЛ в том, что схема логического элемента строится на основе интегрального дифференциального

усилителя (ДУ), транзисторы которого могут переключать ток и при этом

никогда не попадают в режим насыщения. Поэтому такие схемы самые

быстродействующие.

Рис.2-12 Схема элемента ЭСЛ

На рис.2-12 а показана основа логического элемента DD1—переключатель тока I0. Если входным сигналом Uвх открыть транзистор VТ1, через

него потечет весь ток I0, вытекающий из общей точки связанных эмиттеров

Э. На коллекторе транзистора VТ1 окажется напряжение низкого уровня. В

этот момент транзистор VТ2 тока не имеет, он вынужденно находится в

состоянии отсечки. На его коллекторе присутствует напряжение высокого

уровня.

Наличие генератора стабильного тока (ГСТ) принципиально, с его

помощью строго фиксируются выходные логические уровни.

В отличие от аналоговых применений дифференциального усилителя,

когда

стремятся

использовать

разность

напряжений

Uвых

между

коллекторами, цифровая микросхема, переключающая ток I0, снабжается

двумя инверсными выходами логических уровней, где

выделяются

напряжения высокого и низкого уровней.

На рис.2-12б показан простейший одновходовый элемент ЭСЛ. Новым в

развитии элемента DD1 (рис. а) здесь является источник опорного

напряжения

Uоп.

Это

напряжение

фиксирует

порог

срабатывания

переключателя тока. Тем самым дифференциальный усилитель превращается

в логический элемент. У него теперь два состояния выходов, которые

переключаются лишь при условиях: Uвх>Uоп или Uвх<Uоп. Однако при

проектировании ЭСЛ ставилась задача: получить сверхскоростную логику. В

схеме (рис.2-12 б) этого достичь нельзя, так как выходное сопротивление

выходов Q и Q велико, оно приближается к величине Rн. Для снижения

выходного

сопротивления

к

коллекторным

выходам

подключаются

эмиттерные повторители, работающие в линейном режиме . Теперь выходное

сопротивление эмиттерного выхода значительно уменьшается:

Rвых=Rk/(B+1),

где (В+1)—коэффициент усиления транзистора—эмиттерного повторителя по току. Эмиттерные выходы чаще делаются “открытыми”, чтобы

можно было их соединять в элементы “монтажное ИЛИ”.. Сопротивление

внешнего нагрузочного резистора Rэн можно выбрать от 300 Ом до 30 кОм.

Принципиальная

особенность

отрицательным напряжением-Uи.п

э

микросхем

ЭСЛ:

они

питаются

(то есть напряжение подается от

эмиттеров), причем коллекторные цепи заземляются. Этим способом

повышается помехоустойчивость ЭСЛ. Ток потребления Iпот вытекает из

микросхемы в источник.

7.2.5. Параметры цифровых интегральных схем

Kоб - коэффициент объединения по входу, определяет число входов

данной микросхемы, по которым реализуется логическая функция; Uп допустимое напряжение статической помехи, определяется как разность

выходного и входного напряжений, соответствующих уровню логической 1,

либо уровню логического 0. В расчет принимается меньшее из значений Uп1

= Uвых'- Uвх' и Uп0 = Uвх0 - Uвых0; Pпот.ср - средняя потребляемая мощность,

определяемая выражением Pпот.ср = (Pпот0 + Pпот1)/2, где Pпот0, Pпот1 потребляемая микросхемой мощность в состоянии соответственно 0 и 1 на

входе.

Средняя потребляемая мощность тесно связана с быстродействием

микросхемы:

чем

больше

переключаться схема.

Pпот.ср,

тем

с

большей

частотой

может

7.2.6. Динамические параметры ИС

Основным динамическим усредненным параметром быстродействия ИС

является среднее время задержки распространения сигнала tзд.ср. (tзд0,1. t1зд,0. ) / 2 ,

где

0 ,1

t зд

.-

время задержки распространения сигнала при выключении

микросхемы, t1зд,0. - время задержки при включении микросхемы.

7.2.7. Статические параметры ИС

Uип - напряжение источника питания;

U0вх,U0вых - входное и выходное напряжение логического 0;

U1вх,U1вых - входное и выходное напряжение логической 1;

I0вх,I0вых - входной и выходной ток логического 0;

I1вх,I1вых - входной и выходной ток логической 1;

Kраз - коэффициент разветвления по выходу, определяет число входов

микросхем - нагрузок, которые можно одновременно подключить к выходу

данной микросхемы;

7.3. Условные обозначения интегральных схем

Интегральные микросхемы объединены в серии. Серия состоит из

совокупности различных типов ИС, имеющих одинаковое конструктивное

оформление

и

изготавливаемых

на

основе

одинаковых

базовых

элементарных схем.

Условное обозначение различных типов ИС состоит из четырех

элементов. Первый элемент - цифра, указывающая на технологическую

разновидность микросхемы: полупроводниковые 1, 5, 7; гибридные - 2, 4,

6, 8; прочие - 3. Второй элемент обозначает порядковый номер серии и

состоит из двух цифр 00-:99. Третий индекс из двух букв определяет

функциональные свойства ИС, ее назначение. Четвертый элемент порядковый номер разработки ИС в данной серии для микросхем одного

назначения. Более подробные данные об ИС приводятся в справочниках.

ТЕМА 8. Мультиплексоры и демультиплексоры. Универсальные логические

модули на основе мультиплексоров. Компараторы

8.1. Мультиплексоры и демультиплексоры

Мультиплексоры осуществляют подключение одного из входных каналов к

выходному под управлением управляющего (адресующего) слова. Разрядности

каналов

могут

быть

различными,

мультиплексоры

для

коммутации

многоразрядных слов составляются из одноразрядных.

Рис. 2.13 – Упрощенное представление мультиплексора многопозиционным

ключом (а) и реализация мультиплексора на элементах И-НЕ (б)

Входы мультиплексора делятся на две группы: информационные и адресующие. Работу мультиплексора можно упрощенно представить с помощью

многопозиционного ключа. Для одноразрядного мультиплексора ого представлено на рис. 2.9, а. Адресующий код А задает переключателю определен-

ное положение, соединяя с выходом F один из информационных входов хi .

При нулевом адресующем коде переключатель занимает верхнее положение

хо, с увеличением кода на единицу переходит в соседнее положение x1 и т. д.

Работа мультиплексора описывается соотношением

которое иногда называется мультиплексной формулой. При любом значении

адресующего кода все слагаемые, кроме одного, равны нулю. Ненулевое

слагаемое равно х$, где I — значение текущего адресного кода.

Схемотехнически мультиплексор реализует электронную версию показанного переключателя, имея, в отличие от него, только одностороннюю передачу данных. На рис. 2.9, 6 показан мультиплексор с четырьмя информационными входами, двумя адресными входами и входом разрешения работы

При отсутствии разрешения работы (Е = 0) выход F становится нулевым

независимо от информационных и адресных сигналов.

В стандартных сериях размерность мультиплексоров не более 16x1.

8.2. Универсальные логические модули на основе мультиплексоров

Универсальные логические модули (УЛМ) на основе мультиплексоров относятся к устройствам, настраиваемым на решение той или иной задачи Универсальность их состоит в том, что для заданного числа аргументов можно

настроить УЛМ на любую функцию. Известно, что общее число функций n

аргументов выражается как 2n С ростом n число функций растет чрезвычайно

быстро. Хотя практический интерес представляют не все существующие

функции, возможность получить любую из огромного числа функций

свидетельствует о больших перспективах применения УЛМ.

8.2.1. Первый способ настройки УЛМ

Первым способом настройки, используемым в УЛМ, является фиксация некоторых входов. Для этого способа справедливо следующее соотношение

между числом аргументов и числом настроечных входов. Пусть число аргументов n и требуется настройка на любую из функций. Тогда число комбинаций для кода настройки, равное числу функций, есть 2n . Для двоичного

кода число комбинаций связано с разрядностью кода выражением 2 m, где

m— разрядность кода. Приравнивая число воспроизводимых функций к

числу комбинаций кода настройки, имеем для числа настроечных входов

соотношение m = 2n.

Рис. 2.12. Схема использования мультиплексора в качестве УЛМ (а),

примеры воспроизведения функций при настройке константами (б) и при

переносе одного аргумента в число сигналов настройки (в)

Полученному выражению отвечает соотношение между числом входов разного типа для мультиплексора. При этом на адресные входы следует

подавать аргументы функции, а на информационные входы — сигналы

настройки (рис. 2.12, а). Таким образом, для использования мультиплексора в

качестве УЛМ следует изменить назначение его входов.

Рис. 2.12, а - иллюстрирует возможность воспроизведения с помощью

мультиплексора любой функции n аргументов. Действительно, каждому набору аргументов соответствует передача на выход одного из сигналов настройки. Если этот сигнал есть значение функции на данном наборе

аргументов, то задача решена. Разным функциям будут соответствовать

разные коды настройки. Алфавитом настройки будет {0,1}

—

настройка

осуществляется константами 0 и 1. На рис. 2.12, б показан пример

воспроизведения

функции

неравнозначности

x1

х2

с

помощью

мультиплексора "4—1".

Большое число настроечных входов затрудняет реализацию УЛМ. Для УЛМ,

расположенных внутри кристалла, можно вводить код настройки последовательно в сдвигающий регистр, к разрядам которого подключены входы настройки. Тогда внешним входом настройки будет всего один, но настройка

будет занимать не один такт, а 2n тактов. Возможны и промежуточные последовательно-параллельные варианты ввода кода настройки.

8.2.2. Второй способ настройки УЛМ

Большее число входов настройки наталкивает на поиск возможностей их

уменьшения. Такие возможности существуют и заключаются в расширении

алфавита настроечных сигналов. Если от алфавита {0,1} перейти к алфавиту

{0,1, xi}, где хi — литерал одного из аргументов, то число входов аргументов

сократится на единицу, а число настроечных входов— вдвое. Напомним, что

под литералом переменной принимается либо сама переменная, либо се

инверсия. Перенос одного из аргументов в число сигналов настройки не

влечет за собою каких-либо схемных изменений. На том же оборудовании

будут реализованы функции с числом аргументов на единицу больше, чем

при настройке константами.

Для нового алфавита код настройки находится следующим образом. Аргументы за исключением хi полаются на адресующие входы, что соответствует

их фиксации в выражении для искомой функции, которая становится

функцией единственного аргумента хi. Эту функцию, которую назовем

остаточной, и нужно подавать на настроечные входы.

Если искомая функция зависит от и аргументов и в число сигналов настройки

будет перенесен один из аргументов, то возникает n вариантов решения

задачи, т. к. в сигналы настройки может быть перенесен любой аргумент.

Спрашивается, какой именно аргумент целесообразно переносить в сигналы

настройки? Здесь можно опираться на рекомендацию: в настроечные

сигналы следует переводить аргумент, который имеет минимальное число

вхождений в термы функции. В этом случае будут максимально использованы как бы внутренние логические ресурсы мультиплексора, а среди

сигналов настройки увеличится число констант, что и считается благоприятным для схемной реализации УЛМ.

Проиллюстрируем сказанное примером воспроизведения функции трех аргументов F=х|х2х3\/х2х3. Минимальное число вхождений в выражение

функции имеет переменная х1 которую и перенесем в число сигналов настройки. Остаточная функция определится табл. 2.3, а.

Схема УЛМ приведена на рис. 2.12, в.

По пути расширения алфавита сигналов настройки можно идти и дальше, но

при этом понадобятся дополнительные логические схемы, воспроизводящие

остаточные функции, которые будут уже зависеть более чем от одного

аргумента.

a

б

Рис. 2.13. Логический блок выработки сигналов настройки УЛМ с переносом

двух аргументов в сигналы настройки (а) и пример схемы воспроизведения

функции четырех аргументов на мультиплексоре "4—1" (б)

Если в сигналы настройки перевести два аргумента, то дополнительные логические схемы будут двухвходовыми вентилями, что мало усложняет УЛМ

и может оказаться приемлемым решением. В этом случае для сохранения

универсальности УЛМ мультиплексору нужно предпослать блок выработки

остаточных функций, в котором формируются все функции 2-х переменных

(за исключением констант 0 и 1 и литералов самих переменных, которые не

требуется вырабатывать). Такой блок показан на рис. 2.13, а. Пример реализации функции F=х|х2\/х3х4 при алфавите настройки {0,1, x1, x2} показан на

рис. 2.13, б. Таблица остаточной функции для этого примера приведена в

табл. 2.3, 6.

8.3. Демультиплексоры

Демультиплексорами

называются

устройства,

которые

позволяют

подключать один вход к нескольким выходам. Демультиплексор можно

построить на основе точно таких же схем логического "И", как и при

построении мультиплексора. Существенным отличием от мультиплексора

является возможность объединения нескольких входов в один без

дополнительных схем. Однако для увеличения нагрузочной способности

микросхемы, на входе демультиплексора для усиления входного сигнала

лучше поставить инвертор.

Схема демультиплексора приведена на рисунке 5. В этой схеме для выбора

конкретного

выхода

демультиплексора,

как

и

в

мультиплексоре,

используется двоичный дешифратор.

Рисунок

5.

Принципиальная

схема

демультиплексора,

управляемого

двоичным кодом.

Однако, если рассмотреть принципиальную схему самого дешифратора, то

можно значительно упростить демультиплексор. Достаточно просто к

каждому логическому элементу 'И', входящему в состав дешифратора просто

добавить ещё один вход – In. Такую схему часто называют дешифратором с

входом

разрешения

работы.

Условно-графическое

изображение

демультиплексора приведено на рисунке 6.

Рисунок 6. Условно графическое обозначение демультиплексора с четырьмя

выходами.

В этом обозначении вход In обозначен как вход E, а выходы не названы

никак, оставлены только их номера.

В

МОП

микросхемах

не

существует

отдельных

микросхем

демультиплексоров, так как МОП мультиплексоры, описанные ранее по

информационным сигналам не различают вход и выход, т.е. направление

распространения информационных сигналов,

точно также

как

и

в

механических ключах, может быть произвольным. Если поменять входы и

выход местами, то КМОП мультиплексоры будут работать в качестве

демультиплексоров. Поэтому их часто называют просто коммутаторами.

8.4. Компараторы

Компараторы (устройства сравнения) определяют отношения между двумя

словами. Основными отношениями, через которые можно выразить остальные, можно считать два — "равно" и "больше".

Определим функции, вырабатываемые компараторами, следующим образом:

они принимают единичное значение (истинны), если соблюдается условие,

указанное в индексе обозначения функции. Например, функция Р А=В =1, если

А = В и принимает нулевое значение при А В.

Приняв в качестве основных отношения "равно" и "больше", для остальных

можно записать:

FA B=FA=B;

FA<B=FB>A;

FA≥B=FB>A; FA≤B= FA>B

Эти отношения используются как логические условия в микропрограммах, в

устройствах контроля и диагностики ЭВМ и т. д.

В сериях цифровых элементов обычно имеются компараторы с тремя выходами: "равно", "больше" и "меньше" (рис. 2 16) Для краткости записей в индексе выходных функций указывается только слово А.

Рис. 2.16- Условное обозначение компаратора с тремя выходами

Устройства сравнения на равенство строятся на основе поразрядных операций над одноименными разрядами обоих слов. Слова равны, если равны все

одноименные их разряды, т. е. если в обоих нули или единицы. Признак

равенства разрядов

Признак неравенства разрядов

Признак равенства слов R = rn-1 rn-2 … r0.

Схема компаратора на равенство в базисе И-НЕ показана на рис. 2.17, а.

Схема без парафазных входов (рис. 2.17, 6) основана на выражениях

для гр преобразованных следующим образом:

Построение

компаратора

одноразрядных

слов

на

"больше"

(табл. 2.7)

для

требует

реализации функции FA>B =аb.

Функцию FA>B Для многоразрядных слов проще

всего

получить

на

основе

рассуждений.

Пусть

нужно

сравнить

двухразрядные слова. Если старшие разряды а1 и b1 не равны, то результат

известен независимо от младших разрядов: при а1 = 1 и b1 = 0 имеем А>В, а

при а1 = 0 и b1 = 1 имеем A<В. Если же а1=b1, результат еще неизвестен, и

требуется анализ следующего разряда по тому же алгоритму. Поэтому для

двухразрядных слов можно записать

Подобный же подход справедлив и для слои любой разрядности — к анализу

следующего разряда нужно переходить только при равенстве предыдущих.

Таким образом, для общего сличая п-разрядных слов имеем

ТЕМА 9. Шифраторы и дешифраторы. Сумматоры и полусумматоры.

9.1 Шифраторы, дешифраторы и преобразователи кодов

Шифратор — это комбинационное устройство, преобразующее десятичные

числа в двоичную систему счисления, причем каждому входу может быть

поставлено в соответствие десятичное число, а набор выходных логических

сигналов соответствует определенному двоичному коду. Шифратор иногда

называют «кодером» (от англ. coder) и используют, например, для перевода

десятичных чисел, набранных на клавиатуре кнопочного пульта управления,

в двоичные числа. Если количество входов настолько велико, что в

шифраторе используются все возможные комбинации сигналов на выходе, то

такой шифратор называется полным, если не все, то неполным. Число входов

и выходов в полном шифраторе связано соотношением n = 2m, где n — число

входов, m — число выходов. Так, для преобразования кода кнопочного

пульта в четырехразрядное двоичное число достаточно использовать лишь 10

входов, в то время как полное число возможных входов будет равно 16 (n =

24 = 16), поэтому шифратор 10x4 (из 10 в 4) будет неполным.

Рассмотрим

пример

построения

шифратора

для

преобразования

десятиразрядного единичного кода (десятичных чисел от 0 до 9) в двоичный

код. При этом предполагается, что сигнал, соответствующий логической

единице, в каждый момент времени подается только на один вход. Условное

обозначение такого шифратора и таблица соответствия кода приведены на

рис. 3.61. Используя данную таблицу соответствия, запишем логические

выражения, включая в логическую сумму те входные переменные, которые

соответствуют единице некоторой выходной переменной. Так, на выходе у,

будет логическая «1»тогда, когда логическая «1» будет или на входе X,, или

Х3, или Х5, или Х7, или X,, т. е.

У1 = X1 + Х3 + Х5 + Х7 + X9.

Аналогично получаем

У2 = X2 + X3 + X6 + X7

У3 = X4 + X5 + X6 + Х7, у4 = Х8+ Х9.

Представим на рис. 3.62 схему такого шифратора, используя элементы ИЛИ.

На практике часто используют шифратор с приоритетом. В таких

шифраторах код двоичного числа соответствует наивысшему номеру входа,

на который подан сигнал «1», т. е. на приоритетный шифратор допускается

подавать сигналы на несколько входов, а он выставляет на выходе код числа,

соответствующего старшему входу.

Рассмотрим в качестве примера (рис. 3.63) шифратор с приоритетом

(приоритетный шифратор) К555ИВЗ серии микросхем К555 (ТТЛШ).

Шифратор имеет 9 инверсных входов, обозначенных через PR1, ... , РР9.

Аббревиатура PR обозначает «приоритет». Шифратор имеет четыре инверсных выхода В\, ... , В8. Аббревиатура В означает «шина» (от англ. bus).

Цифры определяют значение активного уровня (нуля) в соответствующем

разряде двоичного числа. Например, В8 обозначает, что ноль на этом выходе

соответствует числу 8. Очевидно, что это неполный шифратор.

Если на всех входах — логическая единица, то на всех выходах также

логическая единица, что соответствует числу 0 в так называемом инверсном

коде (1111). Если хотя бы на одном входе имеется логический ноль, то

состояние выходных сигналов определяется наибольшим номером входа, на

котором имеется логический ноль, и не зависит от сигналов на входах,

имеющих меньший номер.

Например, если на входе PR\ — логический ноль, а на всех остальных входах

— логическая единица, то на выходах име-ются следующие сигналы: В1 - О,

В2 -1, В4 -1, В8 -1, что соответствует числу 1 в инверсном коде (1110).

Если на входе PR9 логический ноль, то независимо от других входных

сигналов на выходах имеются следующие

сигналы: В1 — 0, В2-1, В4-\, .88-0, что соответствует числу 9 в инверсном

коде (0110).

Основное назначение шифратора — преобразование номера источника

сигнала в код (например, номера нажатой кнопки некоторой клавиатуры).

Для получения шифраторов с большим числом входов, т. е. наращивания

размерности

шифратора,

объединяют

микросхемы

шифраторов

с

дополнительными выводами.

Так микросхема К555ИВ1 (рис. 3.64) представляет собой приоритетный

шифратор 8 х 3, т. е. имеет 8 инверсных входов и 3 инверсных выхода.

Помимо этого она имеет вход разрешения EI, выход переноса Е0 и выход G,

определяющий признак входного информационного сигнала.

Если на всех информационных входах логическая 1, то при подаче на вход EI

логического 0, на выходах 1—2—4 и G будут такие логические 1, а на

выходе переноса ЕО — логический 0.

Если активизировать один из информационных входов (подать на него

логический

0),

то

на

выходах

1—2—4

появится

инверсный

код,

соответствующий номеру активизированного входа, на входе G —

логический 0, являющийся признаком подачи входного сигнала, а на выходе

ЕО — логическая 1.

Если же микросхема не активизирована, т. е. на вход разрешения Е1 подана

логическая 1, то на всех выходах микросхемы также будет логическая 1

независимо от того, что будет подано на информационные входы.

Дешифратором называется комбинационное устройство, преобразующее nразрядный двоичный код в логический сигнал, появляющийся на том выходе,

десятичный номер которого соответствует двоичному коду. Число входов и

выходов в так называемом полном дешифраторе связано соотношением

т = 2 n , где п — число входов, а т — число выходов. Если в работе

дешифратора используется неполное число выходов, то такой дешифратор

называется неполным. Так, например, дешифратор, имеющий 4 входа и 16

выходов, будет полным, а если бы выходов было только 10, то он являлся бы

неполным.

Обратимся для примера к дешифратору К555ИД6 серии К555 (рис. 3.65).

Дешифратор имеет 4 прямых входа, обозначенных через А\, ..., Л8.

Аббревиатура А обозначает «адрес» (от англ. address). Указанные входы

называют адресными. Цифры определяют значения активного уровня

(единицы) в соответствующем разряде двоичного числа.

Дешифратор имеет 10 инверсных выходов У0, ... , К9. Цифры определяют

десятичное число, соответствующее заданному двоичному числу на входах.

Очевидно, что этот дешифратор неполный.

Значение активного уровня (нуля) имеет тот выход, номер которого равен

десятичному числу, определяемому двоичным числом на входе. Например,

если на всех входах — логические нули, то на выходе ко— логический ноль,

а на остальных выходах — логическая единица. Если на входе А2 —

логическая единица, а на остальных входах — логический ноль, то на выходе

Y2 — логический ноль, а на остальных выходах — логическая единица. Если

на входе — двоичное число, превышающее 9 (например, на всех входах

единицы, что соответствует двоичному числу 1111 и десятичному числу 15),

то на всех выходах — логическая единица.

Помимо информационных имеется один или более входов, называемых

входами разрешения, или адресными входами. Так, микросхема КР531ИД14

представляет собой два дешифратора 2 х 4, т. е. каждый дешифратор имеет

два информационных входа и четыре инверсных выхода, а также инверсный

вход разрешения (рис. 3.66).

9.2 Сумматоры и полусумматоры.

Полусумматор это логическая цепь, которая вырабатывает сигналы

суммы (S) и переноса (С) при сложении двух двоичных чисел а и в.

Составим таблицу функционирования.

Из таблицы получим:

. – сигнал суммы;

- сигнал переноса.

Эти выражения упрощению не поддаются.

Приведем к виду, удобному для реализации на элементах ИЛИ-НЕ.

Исходя из полученных формул составим схему полусумматора (рис. 2.31, а):

Рисунок 2.31 – Схема полусумматора

Поскольку полусумматор имеет широкое применение и его выпускают

в виде отдельной микросхемы, он имеет собственное обозначение (рис. 2.31

б).

Составляя дизъюнктивную нормальную форму для полусумматора, мы

получили следующие булевы функции:

Следовательно, перенос происходит с помощью функции И, а

выработка сигнала суммы (функции неравнозначности) производится

элементом ИСКЛЮЧАЮЩЕЕ – ИЛИ. На рис.2.32 показана схема

полусумматора, составленная из этих элементов.

Рисунок 2.32 – Схема полусумматора.

Сумматор. В отличие от полусумматора должен воспринимать 3

входных сигнала: 2 слагаемых и сигнал переноса с предыдущего разряда.

Сумматором называется операционный узел ЭВМ, выполняющий

операцию арифметического сложения двух чисел.

Чтобы

понять

сущность

работы

комбинационного

сумматора,

рассмотрим примеры суммирования двух одноразрядных двоичных чисел:

Из приведенных примеров (1 - 4) видно, что если отсутствует перенос

из младшего разряда, то перенос в старший разряд может быть только в

одном случае, когда оба числа равны единице. Если же имеется перенос из

младшего разряда, то перенос в старший разряд будет всегда, кроме одного

случая, когда оба слагаемых равны нулю.

Составим таблицу функционирования:

Таблица 15

Схема сумматора может быть реализована на двух полусумматорах,

соединенных как указано на схеме рис. 2.33. В этой схеме выделим

промежуточные сигналы Pi, gi, ri. Введем эти сигналы в новую таблицу

функционирования. Соответствие работы этой схемы (рис. 2.33) и таблицы

фунционирования можно проверить перебором всех возможных вариантов.

Рисунок 2.33 – Схема полного сумматора

Многоразрядный сумматор с последовательным переносом. Таким

образом, в общем случае для каждого разряда необходима логическая схема с

тремя входами ai, bi, Ci и двумя выходами Si, Ci+1. Такая схема и есть полный

сумматор. Ее можно реализовать с помощью двух полусумматоров.

Таблица 16

Для сложения двух многоразрядных двоичных чисел на каждый разряд

необходим один полный сумматор. Только в младшем разряде можно

обойтись полусумматором. На рис. 2.34 приведена схема, предназначенная

для сложения двух четырехразрядных чисел А и В. Эта схема выпускается в

интегральном исполнении. В ее младшем разряде также используется

полный сумматор, чтобы иметь возможность наращивания разрядности

схемы.

Рисунок 2.34 – Сумматор с последовательным переносом

Сумматоры с параллельным переносом. Время выполнения операции в

сумматоре с параллельным переносом намного больше времени сложения в

одноразрядном сумматоре. Действительно, сигнал переноса С4 только тогда

может принять истинное значение, когда будет установлено правильное

значение

С3.

Такой

порядок

выполнения

операций

называется

последовательным переносом (Ripple Carry).

Чтобы уменьшить время операции сложения многоразрядных чисел

можно использовать схемы параллельного переноса (Carry look-ahead). При

этом все сигналы переноса вычисляются непосредственно по значениям

входных переменных.

Согласно таблице переключений, в общем случае для сигнала переноса

любого i-го разряда справедливо соотношение:

(1)

Величины gi, ri вычисляются в качестве промежуточных результатов и

в

полном

сумматоре.

Следовательно,

их

получение

не

требует

дополнительных затрат. Смысл этих величин объясняется совсем просто.

Сигнал gi вырабатывается тогда, когда в данном разряде перенос происходит

из-за комбинации входных переменных ai,bi. Поэтому его называют

функцией генерации переноса. Сигнал Pi показывает, передается ли

полученный в младшем разряде сигнал переноса Ci дальше. Поэтому он

называется функцией распространения переноса.

Пользуясь выражением (1), можно вывести следующие формулы для

вычисления сигналов переноса:

(2)

Очевидно, что хотя полученные выражения достаточно сложные, время

формирования

вспомогательных

сигнала

переноса

функций

в

определяется

любой

только

разрад

с

времением

помощью

здержки

распространения сигнала на двух элементах. Эти функции реализуются

специальным комбинационным устройством – схемой ускоренного переноса.

Схема сумматора с параллельным переносом приведена на рис. 2.35, а.

На рис. 2.35, б изображена схема устройства параллельного переноса в

группе из четырех разрядов. Эта схема реализует систему уравнений (2).

Рисунок 2.35 –Схема сумматора с параллельным переносом

Рисунок 2.36 –Схема ускоренного переноса

Схема выпускается в интегральном исполнении.

Сложение чисел, содержащих более четырех разрядов, можно реализовать

подключением нескольких четырехразярадных сумматоров.

ТЕМА 10. Арифметико-логические устройства (АЛУ). Программируемые

логические матрицы (ПЛМ). Матричные умножители

10.1 Арифметико-логические устройства и блоки ускоренного переноса

Арифметико-логические устройства АЛУ (ALU, Arithmetic-Logic Unit)

выполняют над словами ряд действий. Основой АЛУ служит сумматор,

схема

которого

дополнена

логикой,

расширяющей

функциональные

возможности АЛУ и обеспечивающей его перестройку с одной операции на

другую.

Обычно АЛУ четырехразрядны и для наращивания разрядности

объединяются с формированием последовательных или параллельных

переносов. Логические возможности АЛУ разных технологий (ТТЛШ,

КМОП, ЭСЛ) сходны. В силу самодвойственности выполняемых операций

условное обозначение и таблица истинности АЛУ встречаются в двух

вариантах, отличающихся взаимно инверсными значениями переменных.

АЛУ (рис. 2.35) имеет входы операндов А и В, входы выбора операций

S, вход переноса Ci и вход М (Моdе), сигнал которого задает тип выполняемых операций: логические (М = 1) или арифметико-логические (М = 0). Результат операции вырабатывается на выходах F, выходы G и Н дают функции

генерации и прозрачности, используемые для организаций параллельных переносов при наращивании размерности АЛУ. Сигнал Со — выходной перенос, а выход А = В есть выход сравнения на равенство с открытым коллектором.

Рис. 2.35. Условнее обозначение АЛУ

Перечень выполняемых АЛУ операций дан в табл. 2.13. Для краткости двоичные числа s3s2s1s0 представлены их десятичными эквивалентами. Под

утолщенными обозначениями 1 и 0 следует понимать наборы 1111 и 0000,

входной перенос поступает в младший разряд слова, т. е. равен 000Сi. При

арифметических операциях учитываются межразрядные переносы.

Таблица 2.13.

Шестнадцать логических операций позволяют воспроизводить все функции

двух переменных. В логико-арифметических операциях встречаются и логические и арифметические операции одновременно.

Запись типа А\/В + АВ следует понимать так: вначале поразрядно выполняются операции инвертирования (В), логического сложения (А\/В) и умножения (АВ), а затем полученные указанным образом два четырехразрядных числа складываются арифметически.

При операциях над словами большой размерности АЛУ соединяются друг с

другом с организацией последовательных (рис. 2.36, а) или параллельных

(рис. 2.36, б) переносов. В последнем случае совместно с АЛУ применяют

микросхемы — блоки ускоренного переноса (СRU, Саrrу Unit), получающие

от отдельных АЛУ функции генерации и прозрачности, а также входной

перенос и вырабатывающие сигналы переноса

Рис. 2.36. Схемы наращивания АЛУ при последовательном (в) и

параллельном (б) переносах и реализация функций компаратора для группы

АЛУ (в)

Блок СКГ вырабатывает также функции генерации и прозрачности для всей

группы обслуживаемых им АЛУ, что при необходимости позволяет организовать параллельный перенос на следующем уровне (между несколькими

группами из четырех АЛУ).

На рис. 2.36, в показаны способы выработки сигналов сравнения слов для

группы АЛУ. Выход сравнения на равенство выполняется по схеме монтажной логики для выходов типа ОК. Комбинируя сигнал равенства слов с сигналом переноса на выходе группы при работе АЛУ в режиме вычитания,

легко получить функции FA≥B и FA≤B. Если А < В, то при вычитании возникает заем из старшего разряда и FA≤B = 1. Если заем отсутствует (А>В), то подучим FA≥B = 1.

10.2. Матричные умножители

Микросхемы множительных устройств появились в 1980-х годах, когда достигнутый уровень интеграции позволил разместить на одном кристалле достаточно большое количество логических элементов.

Структура

матричных

умножителей

тесно

связана

со

структурой

математических выражений, описывающих операцию умножения.

Пусть имеются два целых двоичных числа без знаков Аm = аm-1...ао и Вn = bn1...bо,

Их перемножение выполняется по известной схеме "умножения

столбиком". Если числа четырехразрядные, т. е. m = n = 4, то

Произведение выражается числом Рm+n = Рm+n-1 Pm+n-2 … Ро.

Члены вида аibj, где i = 0... (m-1) и j = 0... (n-1) вырабатываются параллельно

во времени конъюнкторами. Их сложение в столбцах, которое можно

выполнять разными способами, составляет основную операцию для умножителя и определяет почти целиком время перемножения.

Матричные перемножители могут быть просто множительными блоками

(МБ) или множительно-суммирующими (МСБ), последние обеспечивают

удобство наращивания размерности умножителя.

МСБ реализует операцию Р = Аm х Вn + Сm + Dn, т. е. добавляет к произведению два слагаемых: одно разрядности m, совпадающей с разрядностью

множимого, другое разрядности n, совпадающей с разрядностью множителя.

10.2.1. Множительно-суммирующие блоки

Множительно-суммирующий блок для четырехразрядных операндов без

набора конъюнкторов, вырабатывающих члены вида аibj, показан на рис.

2.37, а, где для одноразрядного сумматора принято обозначение (рис. 2.37, б).

Для построения МСБ чисел равной разрядности потребовалось n2 конъюнкторов и n2 одноразрядных сумматоров.

Рис. 2.37. Схема множительно-суммирующего блока для четырехрезрядных

сомножителей (а), обозначение одноразрядного сумматоре для данной схемы

(б)

Рис. 2.38. К пояснению принципа наращивания размерности множительных

устройств (в), условное обозначение множительно-суммирующего блока (б)

и схема умножителя 4x4", построенная на множительно-суммирующих

блоках "4 х 2" (в)

Максимальная длительность умножения — сумма задержек сигналов в

конъюнкторах для выработки членов аibj и задержки в наиболее длинной

цепочке передачи сигнала в матрице одноразрядных сумматоров, равной 2n 1 (m + n - 1 в общем случае). Таким образом, tМРL = tк + (2n - 1)tsм,

Схема множительного блока отличается от схемы МСБ тем, что в ней отсутствуют сумматоры правой диагонали, т. к. при Сm = 0 и Dn = 0 они не требуются.

Построение умножителей большей размерности из умножителей меньшей

размерности на основе МБ требует введения дополнительных схем, называемых "деревьями Уоллеса", которые имеются в некоторых зарубежных

сериях. При использовании МСБ дополнительные схемы не требуются.

Принцип наращивания размерности умножителя иллюстрируется на рис.

2.38, а на примере построения МРЬ "4 х 4" из МСБ "4 х 2". На поле

частичных

произведений

выделены

зоны,

воспроизведение

которых

возможно на блоках размерности 4x2 (это две первые строки и две

последние).

Перемножение

в

пределах

зон

дает

частичные

произведения

Р51Р41РЗ1Р21Р11Р01 и Р2 = Р52Р42Р32Р22Р12Р02. Для

р1 =

получения

конечного значения произведения эти частичные произведения нужно

сложить с учетом их взаимного положения (сдвига одного относительно

другого).

Схема, реализующая указанный принцип, изображена на рис. 2.38, в. В ней

использовано условное обозначение МСБ (рис. 2.38, б). Для общности оба

блока размерности 4x2 показаны как МСБ, хотя первый может быть просто

множительным блоком, т. к. для него слагаемые С и D имеют нулевое

значение.

10.2.2. Схемы ускоренного умножения

Для ускорения умножения разработан ряд алгоритмов, большой вклад в эти

разработки внес Э. Бут (Е. Вооt). Рассмотрим процесс умножения по гак

называемому модифицированному алгоритму Бута (умножение сразу на два

разряда).

Из изложенного выше видно, что основную задержку в процесс выработки

произведения вносит суммирование частичных произведений. Уменьшение

их числа сократило бы время суммирования. К этому приводит алгоритм,

основанный на следующих рассуждениях.

Пусть требуется вычислить произведение

Р = А х В = А х (b n-1 2 n - 1 + b n -2 2 n - 2 +…+b020).

(a)

Непосредственное воспроизведение соотношения (а) связано с выработкой

частичных произведений вида

(i = 0...n - 1). Число таких произведений

равно разрядности множителя n.

Выражение (а) можно видоизменить с помощью соотношения

,

справедливость которого очевидна.

(б)

Это соотношение позволяет разреживать последовательность (спектр) степеней в сумме частичных произведений. Можно, например, исключить четные степени, как показано на рис. 2.39, а. Исключение четных (или нечетных) степеней не только изменяет значения оставшихся частичных произведений, но и сокращает их число примерно вдвое, что, в конечном счете, ускоряет выработку произведения. Для того чтобы "разнести по соседям" член

со степенью

, расширим разрядную сетку, введя слагаемое

(нулевой разряд с номером -1).

Оставшиеся частичные произведения имеют вид

.

Так как число частичных произведений уменьшилось примерно вдвое, при

применении этого алгоритма говорят об умножении сразу на два разряда.

Рис- 2.39- К пояснению принципа быстрого умножения "срезу на два

разряда" (в) и схема быстрого умножения (б)

Для всех возможных сочетаний bi+1, bi , bi-1 можно составить таблицу

(табл. 2.14) частичных произведений.

Модуль 4. Цифровые запоминающие устройства. Устройства

сопряжения аналоговых и цифровых схем.

ТЕМА 14. Основные сведения. Основные структуры ЗУ

14.1 Виды памяти

Память компьютера – совокупность устройств для хранения информации. Вся

память компьютера делиться на внутреннюю и внешнюю. Внутренняя делиться на

оперативную, постоянную и кэш – память, а внешняя на жёсткие диски, гибкие

диски, cd и dvd диски и магнитные ленты.

Основная память предназначена для хранения и оперативного обмена

информацией с другими блоками компьютера. Делится на постоянное

запоминающее устройство (ПЗУ) и оперативное запоминающее устройство

(ОЗУ).

1. ПЗУ (ROM)

служит для хранения неизменяемой программной и

справочной информации. Постоянная память хранит в себе системные файлы,

которые необходимы для загрузки операционной системы, проверки устройств

компьютера, а так же файлы BIOS. Такая память называется ROM – (read only

memory), Просмотр этой памяти невозможен так как эта память постоянная. Бывает

два вида: однократно программируемые и многократно программирумая.

2. ОЗУ (Оперативная память) - это обязательная составная часть

компьютера, предназначенная для хранения переменной информации и

допускающая

изменение

своего

содержимого

в

ходе

выполнения

процессором операций по обработке информации. Вся информация,

вводимая в ЭВМ и возникающая в ходе ее работы, хранится в этой памяти.

ОП представляет собой совокупность ячеек, разделенных на разряды для

хранения в каждом бите информации. В любую ячейку памяти может быть

записан некоторый набор нулей и единиц, образующий машинное слово -

фиксированную,

упорядоченную

последовательность

битов,

рассматриваемую аппаратной частью компьютера как единое целое.

Машинное слово может быть различной длины в зависимости от типа ЭВМ и

определяет наибольшее число, которое может удерживаться в ячейке памяти.

При байтовой архитектуре минимальной единицей измерения информации

является байт, а машинное слово (команда процессора) может равняться 2, 4

или 8 байтам. Следовательно, можно говорить об объеме памяти

компьютера, измерять его в килобайтах, мегабайтах, гигабайтах в соответствии с количеством байтовых ячеек как дискретных структурных единиц

памяти.

Помимо дискретности структуры свойством оперативной памяти

является ее адресуемость. Все ячейки памяти пронумерованы, номер ячейки это ее адрес. Он позволяет отличать ячейки друг от друга, обращаться к

любой ячейке, чтобы записать в нее новую информацию вместо старой или

воспользоваться уже хранящейся в ячейке, для выполнения каких-то

действий с ней. При таком считывании хранящееся в ячейке слово не

изменяется. В оперативной памяти в виде последовательности машинных

слов хранятся как данные, так и программы. Поскольку в любой момент

времени доступ может осуществляться к произвольно выбранной ячейке, то

этот вид памяти также называют памятью с произвольной выборкой - RAM

(Random Access Memory).

Из микросхем памяти (RAM - Random Access Memory, память с

произвольным доступом) используется два основных типа: статическая

(SRAM - Static RAM) и динамическая (DRAM - Dynamic RAM).

В статической памяти элементы (ячейки) построены на различных

вариантах триггеров - схем с двумя устойчивыми состояниями. После записи

бита в такую ячейку она может пребывать в этом состоянии сколь угодно

долго - необходимо только наличие питания. При обращении к микросхеме

статической памяти на нее подается полный адрес, который при помощи

внутреннего дешифратора преобразуется в сигналы выборки конкретных

ячеек. Ячейки статической памяти имеют малое время срабатывания

(единицы-десятки наносекунд), однако микросхемы на их основе имеют

низкую удельную плотность данных (порядка единиц Мбит на корпус) и

высокое энергопотребление. Поэтому статическая память используется в

основном в качестве буферной (кэш-память).

В динамической памяти ячейки построены на основе областей с

накоплением зарядов, занимающих гораздо меньшую площадь, нежели

триггеры, и практически не потребляющих энергии при хранении. При

записи бита в такую ячейку в ней формируется электрический заряд, который

сохраняется в течение нескольких миллисекунд; для постоянного сохранения

заряда ячейки необходимо регенерировать - перезаписывать содержимое для

восстановления

зарядов.

Ячейки

микросхем

динамической

памяти

организованы в виде прямоугольной (обычно - квадратной) матрицы; при

обращении к микросхеме на ее входы вначале подается адрес строки

матрицы, сопровождаемый сигналом RAS (Row Address Strobe - строб адреса

строки), затем, через некоторое время - адрес столбца, сопровождаемый

сигналом CAS (Column Address Strobe - строб адреса столбца). При каждом

обращении к ячейке регенерируют все ячейки выбранной строки, поэтому

для полной регенерации матрицы достаточно перебрать адреса строк. Ячейки

динамической памяти имеют большее время срабатывания (десятки-сотни

наносекунд), но большую удельную плотность (порядка десятков Мбит на

корпус) и меньшее энергопотребление. Динамическая память используется в

качестве основной.

Обычные виды SRAM и DRAM называют также асинхронными потому, что установка адреса, подача управляющих сигналов и чтение-запись

данных могут выполняться в произвольные моменты времени - необходимо

только соблюдение временных соотношений между этими сигналами. В эти

временные соотношения включены так называемые охранные интервалы,

необходимые для стабилизации сигналов, которые не позволяют достичь

теоретически возможного быстродействия памяти. Существуют также

синхронные виды памяти, получающие внешний синхросигнал, к импульсам

которого жестко привязаны моменты подачи адресов и обмена данными;

помимо экономии времени на охранных интервалах, они позволяют более

полно использовать внутреннюю конвейеризацию и блочный доступ.

FРM DRAM (Fast Рage Mode DRAM - динамическая память с быстрым

страничным доступом) активно используется в последние несколько лет.

Память со страничным доступом отличается от обычной динамической

памяти тем, что после выбора строки матрицы и удержанием RAS допускает

многократную установку адреса столбца, а также быструю регенерацию по

схеме «CAS прежде RAS». Первое позволяет ускорить блочные передачи,

когда весь блок данных или его часть находятся внутри одной строки

матрицы, называемой в этой системе страницей, а второе - снизить

накладные расходы на регенерацию памяти.

EDO (Extended Data Out - расширенное время удержания данных на

выходе) фактически представляют собой обычные микросхемы FPM, на

выходе которых установлены регистры-защелки данных. При страничном

обмене такие микросхемы работают в режиме простого конвейера:

удерживают на выходах данных содержимое последней выбранной ячейки, в

то время как на их входы уже подается адрес следующей выбираемой ячейки.

Это позволяет примерно на 15 % по сравнению с FPM ускорить процесс

считывания последовательных массивов данных. При случайной адресации

такая память ничем не отличается от обычной.

BEDO (Burst EDO - EDO с блочным доступом) - память на основе EDO,

работающая

не

одиночными,

а

пакетными

циклами

чтения/записи.

Современные процессоры, благодаря внутреннему и внешнему кэшированию

команд и данных, обмениваются с основной памятью преимущественно

блоками слов максимальной ширины. В случае памяти BEDO отпадает

необходимость постоянной подачи последовательных адресов на входы

микросхем с соблюдением необходимых временных задержек - достаточно

стробировать переход к очередному слову отдельным сигналом.

SDRAM (Synchronous DRAM - синхронная динамическая память) память с синхронным доступом, работающая быстрее обычной асинхронной

(FРM/EDO/BEDO).

Помимо

синхронного

метода

доступа,

SDRAM

использует внутреннее разделение массива памяти на два независимых

банка, что позволяет совмещать выборку из одного банка с установкой

адреса в другом банке. SDRAM также поддерживает блочный обмен.

Основная

выгода

от

использования

SDRAM

состоит

в

поддержке

последовательного доступа в синхронном режиме, где не требуется

дополнительных тактов ожидания. При случайном доступе SDRAM работает

практически с той же скоростью, что и FPM/EDO.

РВ SRAM (Pipelined Burst SRAM - статическая память с блочным

конвейерным доступом) - разновидность синхронных SRAM с внутренней

конвейеризацией, за счет которой примерно вдвое повышается скорость

обмена блоками данных.

Алгоритм работы оперативной памяти:

1.

Включение компьютера загрузка файлов BIOS.

2.

Загрузка файлов системы

3.

Обработка

программ,

которые

открывает

пользователь

После выключения компьютера оперативная очищается. Является

связкой между винчестером и процессором.

Винчестер

Винчестер – это жёсткий диск компьютера. На нём храниться вся

информация. Первая модель жёсткого диска имела 30 дорожек по 30

сектаров – это совпало с калибром ружья “Винчестер”. Сейчас используются

такие модули подключения: IDE, MiniIDE, SATA I, SATA II.

IDE и MiniIDE подключаются через 40-pi слот, такой же слот

используется для CD-rom. Но MiniIDE используется в ноутбуках, и поэтому

он намного компактнее и дороже, чем его собрат IDE.

Но сейчас на рынке появились новые винчестеры: SATA I и SATA II.

Эти винчестеры стоят в несколько раз дороже, чем IDE.

Но они имеют большую скорость записи, и с помощью пары

винчестеров можно создать RAID массив. Массивы бывают разные

1. Raid 0 (striping) объединяет два диска в одну метку тома, тем самым

увеличивает скорость записи и объем.

2. Raid 1 (data mirroring) делает точную копию одного винчестера на

другом, тем самым увеличивается безопасность сохранения информации

3. Raid 0+1 объединяет в себе Raid 1 и Raid 0, но требует 4 винчестера

4. JBOD позволяет установить операционную систему на SATA диск (ни

в одном другом режиме

массив RAID не позволяет устанавливать

операционную систему на диск SATA).

Примерно такие же массивы существуют в SATA II.

Cache - память

Одним

из

использование

способов

кэш-памяти

повышения

(Cache

-

быстродействия

запас),

МП

расположенной

является

между

центральным процессором и ОЗУ. Cache - самая быстродействующая часть

оперативной памяти, к которой процессор обращается напрямую, а не через

системную шину. Она имеет относительно небольшой объем и хранит в себе

наиболее часто используемые участки оперативной памяти, а так как время

доступа к кэш-памяти в несколько раз меньше чем к оперативной, то среднее

время доступа к памяти уменьшается.

Физически Cache представляет собой часть устройства процессора или