Микропроцессорная система

реклама

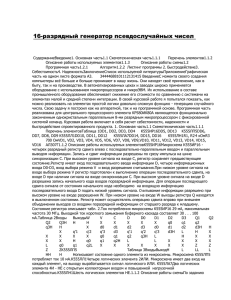

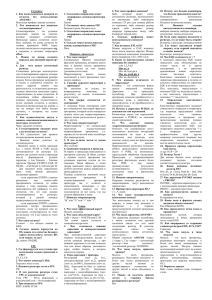

СКГМИ ОСНОВЫ МИКРОПРОЦЕССОРНОЙ ТЕХНИКИ Доц. Кабышев А.М 2011 ВВЕДЕНИЕ Целью изучения дисциплины «Основы микропроцессорной техники» является формирование у студентов знания общей методологии, а также методов проектирования современных микропроцессорных систем (МС). Уникальность применения МС состоит в том, что устройства на их основе обладают «гибкой логикой», это означает, что используя одну и туже, аппаратную часть системы, можно решать различные технологические задачи, изменяя только программное обеспечение системы. При создании автоматизированных систем различного назначения в качестве их основы широко используются два класса средств цифровой техники: а) устройства с жесткой структурой, выполненные на базе цифровых логических схем; б) устройства с гибкой логикой (микропроцессорные системы) Устройства с жесткой структурой обычно содержат большое число интегральных схем (ИС) малой и средней степени интеграции. Эти схемы устанавливаются на платах, а их выводы соединяются в соответствии с реализуемыми функциями. Любое изменение функций требует изменения схемы (перепайки соединений, замены ИС), конструкции, проверочных тестов. Поэтому главные недостатки устройств с жесткой структурой - большое время проектирования и изготовления и трудности внесения изменений. Системы на основе МС могут легко перестраиваться с реализации одной функции на другую, для этого достаточно составить и занести в память новую программу. При этом значительно сокращаются сроки проектирования, изготовления и настройки системы. Успехи полупроводниковой технологии привели к появлению больших интегральных схем (БИС) с плотностью размещения компонентов до десятков тысяч транзисторов на кристалле. Использование БИС позволяет значительно повысить эффективность цифровых систем увеличить их производительность и надежность, уменьшить габариты, массу, потребляемую мощность. При изучении дисциплины будем использовать следующие основные понятия и определения: Процессор - центральное устройство (или комплекс устройств) ЭВМ или вычислительной системы, которое выполняет арифметические и логические операции, управляет вычислительным процессом и координирует работу периферийных устройств системы, под действием программного управления. Микропроцессор - это обрабатывающее и управляющее устройство, выполненное с использованием технологии БИС (часто на одном кристалле) и обладающее способностью выполнять под программным управлением обработку информации, включая ввод и вывод информации, арифметические и логические операции и принятие решений (Микропроцессор –это процессор выполненный на основе одной или нескольких БИС). Микропроцессорная БИС - интегральная микросхема, выполняющая функцию МП или его части (БИС с процессорной организацией, разработанная для построения микропроцессорных систем). Микропроцессорный комплект (МПК) - совокупность микропроцессорных и других интегральных микросхем, совместимых по конструктивно-технологическому исполнению и 2 предназначенных для совместного применения при построении микро-ЭВМ и других средств вычислительной техники. Контроллер - это микро-ЭВМ с небольшими вычислительными ресурсами, обедненной периферией и упрощенной системой команд ориентированная не на производство вычислений, а на выполнение процедур логического управления различным оборудованием. Контроллеры часто применяют в качестве встраиваемых в различные станки, машины, технологические процессы. Микроконтроллер - это микропроцессорное устройство ориентированное не на производство вычислений, а на реализацию заданной функции управления. Микро-ЭВМ - это вычислительная или управляющая система, выполненная на основе одного или нескольких МП содержащая БИС постоянной и оперативной памяти, БИС управления вводом и выводом информации и оснащенная необходимым периферийным оборудованием (дисплей, печатающее устройство, накопители на магнитных дисках и т. п.). Мини-ЭВМ (малая ЭВМ) - малогабаритные ЭВМ общего применения малой или средней производительности используемые главным образом для решения несложных инженерно-технических задач. Специализированные мини-ЭВМ используются в системах автоматического управления. Микропроцессорная система (МС) - специализированная информационная или управляющая система, построенная на основе микропроцессорных средств, т. е. набора микропроцессорных схем. ПРЕДСТАВЛЕНИЕ ИНФОРМАЦИИ В МИКРО-ЭВМ И СИСТЕМЫ СЧИСЛЕНИЯ Цифровые электронные устройства строятся на схемах способных находиться в двух состояниях. Если этим состояниям поставить в соответствие символы 1 и 0, то любому числу, букве или символу можно приписать определенное сочетание единиц и нулей. Представление чисел с помощью двух цифр 1 и 0 получило название двоичной или бинарной системы счисления (в основании системы лежит число 2). Каждый разряд двоичной записи числа называют битом. Любое число в системе с любым основанием можно записать в виде суммы, где слагаемыми являются весовые коэффициенты умноженные на значащую цифру. Например, число 245 в десятичной системе можно записать так: 205 = 2 × 102 + 0 × 101 + 5 × 100 = 200 + 0 + 5 Аналогично, число 45 в двоичной системе можно представить как 101101 = 1× 25 + 0× 24 +1× 23 +1× 22 + 0× 21 +1× 20 = 32 + 0 + 8 + 4 + 0 +1 = 45 В первом случае весовые коэффициенты могут принимать значения от 0 до 9 и в основании системы лежит число 10 (десятичная система счисления), а во втором случае весовые коэффициенты могут принимать значения только 0 и 1, а в основании системы лежит число 2 (двоичная система счисления). КЛАССИФИКАЦИЯ ЭВМ 3 Существуют различные критерии для классификации ЭВМ, из которых наиболее распространены следующие: По назначению: общего пользования (универсальные), ориентированные на решение разнообразных задач. По быстродействию: малые (до 100 тыс. операций в секунду), средние (до 500 тыс.), большие (до 1,5 млн.), сверхбольшие (свыше 1,5 млн. операций в секунду). Здесь указано быстродействие центрального процессора. Реальное быстродействие ЭВМ существенно ниже за счет “медленных” устройств ввода-вывода. По составу оборудования: базовые, включающие стандартный минимальный комплект для поставки потребителю; типовые, включающие комплект оборудования, наиболее используемый в настоящее время; специализированные, включающие комплект оборудования, поставляемого по спецификации заказчика. Следует иметь ввиду, что классификация ЭВМ постоянно изменяется. ТИПОВАЯ СТРУКТУРА МИКРОПРОЦЕССОРНЫХ УСТРОЙСТВ. РЕЖИМЫ ФУНКЦИОНИРОВАНИЯ Применение МП позволило создать новый класс вычислительной техники микропроцессорные системы, обобщенная логическая структура которых приведена на рисунке 1. Центральное место в этой структуре занимает микропроцессор, который выполняет арифметические и логические операции над данными, осуществляет программное управление процессом обработки информации, организует взаимодействие всех устройств, входящих в систему. Работа МП происходит под воздействием сигналов схемы синхронизации и начальной установки, часто выполняемой в виде отдельного кристалла. Показанный на рисунке 1 МП может представлять собой или однокристальный МП с фиксированной системой команд или многокристальный МП с микропрограммным управлением. Представленная на рисунке 1 структура отражает магистрально-модульный принцип организации микропроцессорных устройств и систем. Отдельные блоки являются функционально законченными модулями со своими встроенными схемами управления, выполненными в виде одного или нескольких кристаллов БИС или СБИС. Межмодульные связи и обмен информацией между модулями осуществляются посредством коллективных шин (магистралей), к которым имеют доступ все основные модули системы. В каждый данный момент времени возможен обмен информацией только между двумя модулями системы. Магистральный принцип построения сопряжения модулей (интерфейс ЭВМ) предполагает наличие информационно-логической совместимости модулей, которая реализуется путем использования единых способов представления информации, алгоритма управления обменом, форматов команд и способа синхронизации. 4 ША ШД ШУ МП ПЗУ ОЗУ Таймер Контрол лер ввода-вывода INT Контрол лер прерываний R CLK Схема синхронизации и начального сброса Внешнее устройство КПД Рисунок 1 - Обобщенная структура МП-системы Для большинства микропроцессоров характерна трех шинная структура, содержащая шину адреса (ША), двунаправленную шину данных (ШД) и шину управления (ШУ). Как видно из рисунка 1, типовая структура МП-системы предполагает наличие общего сопряжения для модулей памяти (постоянных и оперативных запоминающих устройств) и периферийных устройств (устройств ввода-вывода). В качестве периферийных устройств в МП-системах используются устройства ввода с перфоленты, дисплеи, магнитофоны, гибкие и жесткие магнитные диски, телетайпы, печатающие устройства, клавиатура и т.п. Периферийное устройство подсоединяется к шинам МП не непосредственно, а через программируемый периферийный адаптер (ППА) или программируемый связной адаптер (ПСА), обслуживающие периферийные устройства соответственно с передачей информации параллельным или последовательным кодом. Наличие программно настраиваемых адаптеров делает весьма гибкой и функционально богатой систему ввода-вывода информации в МПсистеме. Постоянное запоминающее устройство (ПЗУ) хранит системные программы, необходимые для управления процессом обработки. В оперативном запоминающем устройстве (ОЗУ) хранятся прикладные программы, данные и результаты вычислений. Работа МП синхронизируется тактовыми сигналами CLK, поступающими на его входы от генератора синхронизации. Схема начальной установки вырабатывает сигнал RESET (сброса) микропроцессора на основе анализа напряжений на выходе блока питания или при принудительной остановке работы МПС с ее клавиатуры. В состав этих МПС, как правило, входят: - шинный контролер для сопряжения устройств с системной шиной по параллельному интерфейсу; - адаптер последовательного интерфейса для построения многопроцессорных систем или сопряжения источников и приемников сигналов, не увеличивающих нагрузку на системный интерфейс; - специализированный процессор арифметической обработки сигналов (сопроцессор); - ПЗУ команд и констант; - ОЗУ операндов. 5 Для обеспечения работы МПС к их системному интерфейсу можно подключать устройства специализированной обработки арифметических алгоритмов, таких как быстрое преобразование Фурье, и устройства обработки аналоговых сигналов. В состав таких устройств обработки аналоговых сигналов входят: -аналого-цифровые (АЦП) и цифроаналоговые (ЦАП) преобразователи, обеспечивающие непосредственное сопряжение цифрового устройства обработки с аналоговыми сигналами датчиков и приемников; - система памяти ПЗУ и ОЗУ; - буферы данных, используемые для временного хранения (буферизации) данных при передаче между устройствами; - МП, предназначенный для цифровой обработки аналоговых сигналов. В рассматриваемых структурах МПС реализуются три способа организации (обслуживания) передачи информации: 1) программно-управляемая передача, инициируемая процессором; 2) программно-управляемая передача, инициируемая запросом прерывания от периферийного устройства; 3) прямой доступ к памяти (ПДП). При первом способе передача инициируется самим процессором, а при втором запросом прерывания от периферийного устройства. При программно-управляемой передаче данных МП на все время этой операции отвлекается от выполнения основной программы, что ведет к снижению производительности МП-системы. Кроме того, скорость передачи данных через МП может оказаться недостаточной для работы с высокоскоростными внешними устройствами. Прямым доступом к памяти называется способ обмена данными, обеспечивающий автономно от МП установление связи и передачу данных между ОЗУ и внешним устройством. Прямой доступ к памяти, повышая предельную скорость ввода-вывода информации и общую производительность МП-системы, делает ее более приспособленной для работы в системах реального времени. Прямым доступом к памяти управляет контролер ПДП, выполняющий следующие функции: - управление инициируемой процессором или ПУ передачей данных между ОЗУ и ПУ; - задание размера блока данных, который подлежит передаче, и области памяти, используемой при передаче; - формирование адресов ячеек ОЗУ, участвующих в передаче; - подсчет числа байт, передаваемых, через интерфейс, и определение момента завершения заданной операции ввода-вывода. МИКРОПРОЦЕССОРЫ Архитектура с тремя шинами Архитектура с тремя шинами является наиболее общей для микропроцессорных систем. Шиной системы называют физическую группу линий передачи сигналов, имеющих схожие 6 функции в рамках системы. Все три шины являются специализированными с точки зрения их функций. Эти шины именуются так: а) адресная шина; б) шина данных; в) шина управления. По адресной шине передаются лишь выходные сигналы микропроцессора, т. е. от микропроцессора к внешнему устройству. Эта шина предназначена для того, чтобы открывать или выбирать правильный тракт для электрического соединения в пределах микропроцессорной системы. Для удобства будем в дальнейшем полагать, что все электрические соединения в микропроцессорной системе осуществляются между микропроцессором и устройством, открытым (выбранным) с помощью адресной шины. В качестве устройства здесь выступает любая электрическая схема, принимающая данные от микропроцессора либо вырабатывающая данные для него. Важнейшей характеристикой адресной шины является ее емкость. Емкость шины определяется числом входящих в нее отдельных электрических линий. К примеру, 16разрядная адресная шина представляет собой 16 независимых физических линий для передачи электрических сигналов. Шина данных является двунаправленной шиной. Это означает, что передача данных может производиться в обоих направлениях. В первом случае, данные передаются от микропроцессора во внешнее устройство (выбранное адресной шиной ). Этот режим называется выводом данных. Во втором случае, данные передаются от внешнего устройства (выбранного шиной адреса) в микропроцессор. Этот режим называется вводом данных. Хотя передача данных по шине данных может производиться в обоих направлениях, однако в каждый заданный момент времени она осуществляется лишь в одном из двух направлений. Это означает, что для передачи данных в устройство (систему) и их приема из системы микропроцессор переводится в соответствующий режим. Также как и адресная шина, шина данных обладает определенной емкостью (разрядностью). По емкости шины данных судят о классе микропроцессора. К примеру, при 8-разрядной шине данных микропроцессор будет отнесен к классу 8-разрядных микропроцессоров. На шине управления действует несколько типов сигналов. Основные из них: а) чтение данных из памяти; б) запись данных в память; в) чтение данных с устройства ввода-вывода; г) запись данных в устройство ввода-вывода. Позднее для этой шины мы введем некоторые добавочные сигналы. Однако для понимания существа процессов пока достаточно ограничиться указанным списком сигналов. Шина управления используется лишь для вывода сигналов, т. е. является однонаправленной. АРХИТЕКТУРА 8-РАЗРЯДНОГО ОДНОКРИСТАЛЬНОГО МИКРОПРОЦЕССОРА СЕРИИ КР580. 7 Общая характеристика однокристального МП серии К580 Микропроцессор КР580ВМ80А является программируемой универсальной БИС, может считывать информацию из внешних устройств, памяти и производить над ней арифметические и логические операции, анализировать результаты вычислений и записывать данные в память и внешние устройства, функционируя при этом под управлением команд из некоторого фиксированного множества. Зарубежными аналогами микропроцессора серии К580 являются БИС Intel8080 и NTE8080A. Микропроцессорная БИС КР580ВМ80А представляет собой однокристальный 8разрядный МП с двумя магистралями: однонаправленной 16-разрядной адресной магистралью (МА), двунаправленной 8-разрядной магистралью данных (МД) и 12 сигналами управления (шесть входных и шесть выходных). Таблица 1 - Технические характеристики БИС КР580ВМ80А. Наименование Технол огия Количество БИС Количество выводов Количество транзисторов в кристалле Тип корпуса Быстродействие: -количество операций в секунду -тактовая частота, Мгц -длительность цикла, мкс Напряжение питания, В Потребляемая мощность, Вт Нагрузочная срособность Характеристики n-МОП 1 40 4500 2123.40-2 500000 < 2.5 1.6 -5;+5;+12 1.25 1 вход ТТЛ схемы Условное обозначение МП БИС К580ВМ80А приведено на рис. 2. D0 D1 D2 D3 D4 D5 D6 D7 Ф1 Ф2 Г З.ПР З.ЗХ СБР +12 В +5 В -5 В ОБЩ A0 CPU A1 A2 A3 A4 A5 A6 A7 A8 A9 A10 A11 A12 A13 A14 A15 П ЗП ОЖД Р.ПР П .ЗХ СИНХ Рисунок 2 - Обозначение МП с ерии КР580ВМ80 Функциональное назначение внешних выводов МП БИС КР580ИК80: Адресная шина (А0-А15), обеспечивающая адресацию к любой из 216 8-разрядной ячейке памяти или внешнего устройства (ВУ); Двунаправленная шина данных (Д0-Д7), используемая для обмена информации с памятью или ВУ; Шина управления (выходная): СИНХР (SYNC) - на этом выходе МП БИС формируется сигнал СИНХР в начале каждого машинного цикла; П (DBIN,прием) - сигнал ПРИЕМ на этом выходе указывает на готов8 ность МП БИС к приему данных; ОЖД (WAIT,ожидание) - сигнал ОЖД на этом выходе указывает что МП находится в состоянии ожидания; ЗП (WR)- на этом выходе МП БИС сигнал ЗП указывает, что данные выданы МП БИС и установлены на МД (магистраль данных) и могут быть записаны в ВУ; П.ЗХ (HLDA, подтверждение захвата) - на этом выходе МП БИС сигнал П.ЗХ появляется в ответ на сигнал З.ЗХ (запрос захвата) и указывает, что МД и МА находятся в состоянии высокого сопротивления; Р.ПР (INTE, разрешение прерывания) - на этом выходе сигнал Р.ПР указывает на состояние внутреннего триггера разрешения прерывания МП БИС. Состояние триггера может быть установлено программно с помощью команд EI,DI. При уровне “0” на выходе Р.ПР прием запросов прерывания МП БИС невозможен. Шина управления (входная): Г (READY, готов) - сигнал ГОТОВ на этом входе информирует о готовности ВУ к обмену информацией с МП БИС . При уровне “0” МП БИС будет находиться в состоянии ОЖИДАНИЕ. З.ЗХ (HOLT, запрос захвата) - вход, используемый для подачи сигнала З.ЗХ на переход МП БИС в состояние ЗАХВАТ, в котором МА и МД переходят в третье состояние (высокое сопротивление). Обычно состояние используется для организации обмена информацией по каналу прямого доступа к памяти; З.ПР (INT, запрос прерывания) - вход, используемый для подачи сигнала З.ПР. Сигнал поступает от внешнего источника на прерывание выполнения основной программы и переход на выполнение подпрограмм обслуживания прерывания. Сигнал запроса прерывания не воспринимается МП БИС при работе его в режимах ЗАХВАТ, ОЖИДАНИЕ или нулевом состоянии внутреннего триггера разрешения прерывания; R (RESET)- вход, по которому поступает сигнал на начальную установку МП БИС, при этом обнуляется его программный счетчик, внутренние триггеры, формирующие сигналы Р.ПР и П.ЗХ; CLK1,2 - входы для подачи тактовых сигналов Ф1(СДК1) и Ф2(СДК2). Эти сигналы являются не пересекающимися во времени сигналами, определяющими тактовую частоту работы МП БИС. Структурная схема МП Микропроцессорная БИС, представленная на рис. 3, включает в себя следующие функциональные блоки: 9 - блок регистров; - арифметико-логический блок; - устройство управления (УУ); - буферные схемы шины данных (БФД) и шины адреса (БФА). Секция регистров включает шесть 16-разрядных регистров: W,Z,B,C,D,E,H,L; РС (программный счетчик) и SP (указатель стека). Шесть 8-разрядных регистров общего назначения составлены в пары регистров: B, C; D, E; H, L. Они могут быть использованы в программах как отдельные 8-разрядные регистры или как три 16-разрядных регистра (B,D,H). Программный счетчик РС содержит текущий адрес памяти, к которому обращается программа. Содержание РС автоматически изменяется в течении каждого цикла команды. Указатель стека SР содержит адрес памяти, начиная с которого ее можно применять для хранения и восстановления содержимого программно- доступных регистров МП БИС. Указатель стека SP служит для работы со стековой памятью и определяет адрес последней занятой ячейки стека. Буферные регистры 0W,Z не являются программно доступными регистрами и используются для выполнения команд внутри МП БИС. ШД (D0-D7) БФД А БФРг Флаги РгК · · БФА ДШК АЛУ · МХ W B D H Z C E L SP PC PA · ДК Устройство управления БФА (A0-A15) Выходная ШУ ША Входная ШУ Рису нок 3 - Структу рная с хема микропроцессора КР580ВМ80 Арифметико-логический блок выполняет арифметические и логические операции под воздействием устройства управления МП БИС. Он включает в себя 8-разрядное АЛУ, схему десятичной коррекции ДК, построенной на базе ПЗУ, 5-ти разрядный регистр признаков, аккумулятор А, буфер аккумулятора БФА и буферный регистр БФРг. Арифметикологический блок позволяет осуществить арифметические операции сложения, вычитания, а также основные логические операции (И, ИЛИ, исключающее ИЛИ) и сдвиг. При проведении операции одно число всегда берется из буфера аккумулятора, а другое - из буферного регистра. По результату выполнения арифметико-логических операций АЛБ устанавливает в регистре признаков пять знаков. 10 Признак переноса (Carry - C) устанавливается в единицу, если при выполнении команд появляется единица переноса из старшего разряда. Дополнительный признак переноса (Auxiliary carry - АС) устанавливается в единицу, если при выполнении команд возникает единица переноса из третьего разряда числа. Состояние разряда может быть проанализировано лишь командой десятичной коррекции числа. Признак знака (Sign - S) в машинном слове можно представить числом от -128 до 127. В этом случае седьмой (старший) разряд числа - его знак. Единица в седьмом разряде при такой записи будет указывать на отрицательное число, а ноль- на положительное. В разряд нулевого признака (Zero -Z) записывается единица, если при выполнении команды результат равен нулю. В разряд признака четности (Parity - P) записывается единица, если при выполнении команды количество единиц в разрядах результата будет четным. Регистр команд РгК и дешифратор команды ДШК используются в МП БИС для получения и дешифрации кода команды. При извлечении команды первый байт, содержащий ее код, помещается в регистр команды и поступает на дешифратор команд. Дешифратор совместно с устройством управления и синхросигналами Ф1 и Ф2 формируют управляющие сигналы для всех внутренних блоков МП БИС, а также его выходные сигналы управления и состояния. Выполнение каждой команды производится в МП БИС в строго определенной последовательности, определяемой кодом команды, и синхронизируется во времени сигналами Ф1 и Ф2 тактового генератора. Период синхросигналов CLK1 и CLK2 называется МАШИННЫМ ТАКТОМ (Т). Длительность машинного такта Т может быть установлена произвольно в диапазоне от 0.5 до 2 микросекунд. При использовании МП БИС необходимо ясно представлять динамику его работы, т.е. на каких магистралях, в зависимости от каких управляющих сигналов и когда МП БИС будет выдавать ту или иную информацию. Это в дальнейшем поможет понимать работу схем, позволяющих согласовывать ее с различными периферийными устройствами микро-ЭВМ. При анализе процессов будем использовать следующие понятия: Машинный цикл (М)-время , требуемое для извлечения из памяти один байт информации или выполнение команды, определяемой одним машинным словом. Машинный цикл может состоять из 3-5 машинных тактов. Время выполнения команды - время получения, декодирования и выполнения команды. В зависимости от вида команды это время может состоять из 1-5 машинных циклов. Для МП БИС КР580ИК80 существует 10 различных типов машинных циклов: 1. Извлечение кода команды (М1). 2. Чтение данных из памяти. 3. Запись данных в память. 4. Извлечение из стека. 5. Запись данных в стек. 6. Ввод данных из внешнего устройства. 7. Запись данных во внешнее устройство. 11 8. Цикл обслуживания прерывания. 9. Останов. 10. Обслуживание прерываний при работе МП БИС в режиме останова. Тип выполняемого цикла МП указывает на первом такте каждого машинного цикла с помощью 8-разрядного слова состояния, выдаваемого на ШД. Отдельные разряды слова состояния задействуются в микро-ЭВМ для формирования магистрали управления. Слово состояния выдается на ШД лишь на интервале синхросигналов С (такты Т1 и Т2), а используется на протяжении всего машинного цикла, поэтому необходимо записать его в специальный регистр слова состояния РгСС. На рисунке 4 приведена схема записи слова состояния. Т1 Ф1 Ф2 Синхр Д 0-Д7 Выход РгСС Т2 МП Д 0-Д7 Прием ШФ РгСС Синхро Ф1 ШД Слово состояния & Рисунок 4 - Временные диаграммы и схема записи слова состояния Запись осуществляется с использованием сигнала “Синхро” и тактового импульса Ф1. Сигнал “Синхро” появляется в начале каждого цикла и занимает промежуток времени между положительными фронтами тактового импульса Ф2 на тактах Т1 и Т2. Таким образом, запись слова состояния осуществляется сигналом Ф1 на такте Т2. Состояние разрядов в регистре состояний для всех типов машинных циклов приведены в таблице 2. Таблица 2 - Слово состояния процессора Разряды регистра D0 D1 D2 D3 D4 D5 D6 D7 Состояние процессора ППР ЗП Сте к ПО Выв М1 ВВ Чт Выборка команды 0 1 0 0 0 1 0 1 Чтение из памяти 0 1 0 0 0 0 0 1 Запись в память 0 0 0 0 0 0 0 0 Чтение из стека 0 1 1 0 0 0 0 1 Запись в стек 0 0 1 0 0 0 0 0 Чтение из УВВ 0 1 0 0 0 0 1 0 Запись в УВВ 0 0 0 0 1 0 0 0 Разрешение прерывания 1 1 0 0 0 1 0 0 Разрешение останова 0 0 0 1 0 0 0 1 Прерыв.во время останова 1 1 0 1 0 1 0 0 Рассмотрим временные диаграммы работы процессора при различных машинных циклах. Извлечение кода команды или данных из памяти или внешнего устройства. Цикл М1 является основным циклом с которого начинается выполнение любой команды, поэтому временные процессы для него рассмотрим более подробно. Анализ процессов будем проводить по каждому машинному такту Т (рисунок 5). 12 На такте Т1 программный счетчик МП выдает на ША адрес ячейки памяти, из которой будет считываться код команды. При этом схема приращения адреса МП автоматически увеличивает на единицу значение числа, записанного в программном счетчике. Положительным фронтом тактового импульса Ф2 формируется сигнал “Синхро” и выдается слово состояния на ШД. Сигнал “Прием”, управляющий двунаправленным шинным формирователем (ШФ) шины данных (рисунок 6), на этом такте равен нулю, что позволяет слову состояния поступить на ШД процессора. Т1 Т2 Тw Т3 Т4 Т5 Ф1 Ф2 Синхро А0-А15 D0-D7 Готов Ожидание Прием Запись Установка Выдача адреса и слова выдача состояния информаПроверка ции о состоянии готовности процессора внешнего устройства Ц икл не обязательный. Присутств только при неготовностии вн. устр. Выборка команды или данных или запись данных Не обязательно. Выполнение операции (если нужно) Рисунок 5 -Временные диаграммы цикла выполнения команды 13 A0-A15 Память МП D0-D7 Прием ДШ · & Синхрo Чт.памяти · РгСС Ф1 ВУ & & Чт.ВУ Рисунок 6 - Схема организации режима чтения кода команды или данных из памяти и данных из ВУ На такте Т2 слово состояния записывается в регистр. Положительным фронтом Ф2 заканчивается сигнал “Синхро” и формируется единичный сигнал “Прием”, позволяющий данным поступить на вход МП через ШФ. На такте Т2 из сигнала “Прием” и седьмого разряда слова состояния (Д7) формируется сигнал на чтение данных из памяти (Чт. памяти), позволяющий данным поступать из памяти на ШД (см. рисунок 5 ). На этом же такте анализируется состояние сигналов “Готов” и “Захват”. При нулевом сигнале на входе “З.Зх” и единичном сигнале на входе “Готов” МП переходит к выполнению такта Т3. Если к моменту появления отрицательного фронта Ф2 на такте Т2 сигнал на входе “Готов” будет иметь нулевой потенциал, то МП на такте Т3 переходит в режим ожидания. В этом режиме приостанавливается процесс обработки данных и формируется единичный сигнал на выходе “Ожидание”, подтверждающий это состояние. Время ожидания выражается целым числом тактов и может длиться бесконечно долго. На каждом такте в этом режиме при отрицательном фронте Ф2 будет проверяться состояние сигнала на входе “Готов”. Изменения в диаграммах работы МП в режимах “Захват”, “Останов” и “Прерывание” будут рассмотрены отдельно. На такте Т3 в момент отрицательного фронта сигнала Ф1 производится запись данных во внутренний регистр кода команды. Положительным фронтом Ф2 снимается сигнал “Прием” на выходе МП и, следовательно, сигнал “Чт. памяти”. На последующих тактах Т4 и Т5 . дешифратор кода команды расшифровывает код команды, определяет количество байтов в команде, формирует команды на внутренние пересылки данных и подготавливает МП к выполнению следующих машинных циклов. Отличие машинных циклов чтения данных из памяти или внешнего устройства будет заключаться лишь в том, что МП будет воспринимать числа, полученные на такте Т3 по ШД не как код команды, а как данные. При приеме данных из внешнего устройства на ШУ формируется сигнал чтение устройства ввода-вывода (Чт.ВУ) из сигнала “Прием” и разряда Д6 регистра состояния. Этот сигнал позволяет именно ВУ выдать информацию на ШД процессора. Запись данных в память или внешнее устройство Процесс записи данных в память иллюстрируется на схеме, показанной на рисунке 7. 14 A0-A15 Память МП ДШ D0-D7 Прием Запись 1 Синхро Ф1 ВУ · & РгСС & & Зп.память Зп.в ВУ Рисунок 7 - Схема организации режима записи данных в память или во внешнее устройство (ВУ) На такте Т1 содержимое регистра адреса МП выдается на ША, а на ШД выдается слово состояния. На такте Т2 на ШД выдаются данные для записи в память. На такте Т3 формируется сигнал “Запись”, по которому будет проходить запись данных в память или ВУ. На протяжении всего машинного цикла записи данных в память сигнал “Прием” находится на нулевом уровне, что позволяет двунаправленному шинному формирователю работать в режиме выдачи данных на ШД МП. Процесс записи данных во внешнее устройство аналогичен записи данных в память. Единственное отличие этого процесса заключается в том, что вместо сигнала “Зп.память” формируется сигнал “Зп.в ВУ”, т.е. в первом случае выполнялась сборка по “И” для сигналов “Запись” с МП и “Память” с РгСС, а во втором - сборка по “И” для сигналов “Запись” и “Вывод”. Работа в режиме «ЗАХВАТ» Режим “Захват” используется для приостановки процесса управления работой всех периферийных устройств. При работе в этом режиме выходные магистрали МП переводятся в третье состояние и отключаются от магистралей внешних устройств, обеспечивая тем самим возможность обмена информацией по каналу прямого доступа к памяти. Режим “Захват” инициируется подачей лог.1 на вход управления МП “З.Зх”. Переход МП в этот режим подтверждается путем выдачи сигнала лог.1 на выходе МП “П.Зх”. Состояние “Захват” будет длиться целое число машинных тактов. Снятие сигнала “Захват”, т.е. появление лог.0 на входе “З.Зх” проверяется на каждом сигнале Ф2 и при его обнаружении МП перейдет к выполнению очередного машинного цикла начиная с такта Т1. Работа в режиме «ОСТАНОВ» Режим ОСТАНОВ является результатом выполнения команды HALT. Находясь в этом режиме, магистрали МП БИС не отключаются от магистралей микро-ЭВМ, а процессор 15 просто отмечает время, в течение которого он ничего не выполняет. Состояние микро-ЭВМ в этом режиме аналогично состоянию ОЖИДАНИЕ, за исключением того, что это состояние устанавливается программно. Обычно режим ОСТАНОВ оканчивается тогда, когда ВУ выдают запрос на обслуживание. Одним из методов формирования запроса на обслуживание является подача запроса прерывания на вход З.Пр процессора. Если сигналы прерывания не воспринимаются процессором (например, после выполнения команды DI), то остается один выход из состояния ОСТАНОВ - подача сигнала начальной установки на вход R процессора. Специфика режима ОСТАНОВ заключается в том, что в этом состоянии МП может входить в режим ЗАХВАТ и выходить из него. В режиме ОСТАНОВ запрос на ЗАХВАТ не будет удовлетворяться, если запрос на прерывание был уже подан на вход З.Пр., но не было еще подтверждено его обслуживание. После подтверждения получения прерывания (уровень “0” на выходе П.Пр) микро-ЭВМ может войти в состояние ЗАХВАТ. Обслуживание запросов на прерывание Внешние устройства выдают сигнал запроса прерывания асинхронно по отношению к работе МП путем подачи уровня “1” на вход З.Пр. Запрос может быть удовлетворен только в том случае, если МП находится в состоянии разрешения восприятия запросов прерывания. МП автоматически устанавливается в состояние запрета запросов прерывания после выполнения начальной установки, а также после начала обслуживания запроса прерывания. Управление состоянием восприятия запросов прерывания может осуществляться программно с помощью команд: EI “Разрешение прерываний” и DI - “Запрет прерываний”. Состояние восприятия запросов прерывания МП указывает на своем выходе Р.Пр. Если на этом выходе присутствует уровень “1”, то запросы прерывания могут быть восприняты, в противном случае (уровень “0” на выводе Р.Пр) запросы восприниматься не будут. Если запрос на прерывание принят, то начинается цикл обслуживания прерывания. Машинный цикл прерывания, который начинается в такте Т1 в условиях разрешенного прерывания, в основных чертах повторяет машинный цикл выборки команды. В течение времени, определяемого единичным значением сигнала синхронизации ШД выставляется слово состояния “Разрешение прерывания”. На такте Т2 слово состояния записывается в регистр состояний и формируется единичный сигнал “Прием”, позволяющий поступление на ШД кода прерывания. Имеется два способа задания кода прерывания: с помощью команды RST (N) или команды CALL (A1), (A2). Отличие машинного цикла прерывания от машинного цикла извлечения кода команды из памяти состоит в том, что содержимое программного счетчика не увеличивается, а запоминается, чтобы оно могло быть восстановлено после окончания программы прерывания и возврата к прерванному процессу (программе). В такте Т3 по шине данных начальная команда программы прерывания RST, подготовленная периферийным устройством, помещается в регистр команд МП. 16 Получив команду на первом машинном цикле, МП на циклах М2 и М3 записывает в область памяти, отведенной под стек, текущее значение программного счетчика РС. Сохранение содержимого РС в стеке необходимо для возврата к прерванной программе после окончания выполнения подпрограммы обслуживания прерывания. Возврат из подпрограммы осуществляется командой RET, которая загружает содержимое двух верхних ячеек стека в РС. Начальная установка В течение всего времени, пока входе R установлен уровень “1”, все операции в МП будут приостановлены. За это время обнуляются программный счетчик, триггер разрешения прерывания и внутренняя логика, связанная с формированием сигнала П.Зх. Следовательно, первая выполняемая команда будет считываться по адресу 0000. После начала выполнения программы прерывания остаются отключенными. Для восстановления возможности восприятия запросов прерывания в программу необходимо включить команду EI. ОСНОВЫ ПРОГРАММИРОВАНИЯ МИКРОПРОЦЕССОРНЫХ УСТРОЙСТВ Классификация команд микропроцессора Как уже отмечалось, принципиальным достоинством МП является программируемость. Это означает, что подавая на вход МП команды, можно обеспечить нужную последовательность операций, т.е. реализацию определенного алгоритма. Алгоритм решаемой задачи может быть сколь угодно сложным, необходимо лишь, чтобы этот алгоритм был разбит на шаги в соответствии с системой команд МП. Поэтому система команд важна не только с точки зрения, что МП может делать, но и как выполняется алгоритм. Наличие или отсутствие какой-либо команды или группы команд может существенно повлиять на выбор МП для конкретного применения. Классификация команд МП представлена на рисунке 8. По числу ячеек памяти, необходимых для размещения одной команды, различают команды длиной в одно, два или три слова. Команды длиной в два или три слова требуют для выборки соответственно два или три цикла обращения к памяти. Во многих случаях, в частности при сравнении МП со сходной архитектурой, оказывается полезной классификация команд в соответствии с архитектурными характеристиками МП. С функциональной точки зрения команды разделяются на три большие группы: передачи, управления и обработки данных. Рассмотрим подробно основные команды, применяемые в МП, пользуясь классификацией по функциональным признакам. Названия команд обозначим русскими словами, указывающими на смысл выполняемых операций. Команды передачи данных обеспечивают простую пересылку информации без выполнения каких-либо операций обработки. Команды этой группы делятся на команды 17 связанные с обращением к памяти, команды обращения к регистрам и команды ввода вывода. К командам связанным с обращением к памяти относятся: ЗАГРУЗИТЬ (ПРОЧИТАТЬ), по которой содержимое одной из ячеек памяти засылается в регистр; ЗАПОМНИТЬ (ЗАПИСАТЬ), по которой содержимое регистра засылается в ячейку памяти. В командах, связанных с пересылкой байта или слова, должны указываться номер конкретного регистра, адрес ячейки памяти и, если необходимо, номер модуля ЗУ. Команды, связанные с обращением к регистрам, должны указывать номер источника информации и номер регистра результата. В эту подгруппу команд передачи данных входят команды: ЗАГРУЗИТЬ НЕПОСРЕДСТВЕННО, по которой в регистр записывается константа, указанная в коде команды; ПЕРЕСЛАТЬ, по которой содержимое одного регистра пересылается в другой. К командам ввода-вывода относятся: ВВОД, по которой содержимое устройства ввода засылается во внутренний регистр МП; ВЫВОД, по которой содержимое внутреннего регистра МП (обычно аккумулятора) пересылается в устройство вывода. 18 КЛАССИФИКАЦИЯ КОМАНД По длине По архи тектурным признакам По функциональным признакам Команды длиной в одно слово Команды изменения содержимого ячеек памяти Команды передачи данных Команды длиной в два слова Команды изменения содержимого аккумулятора Команды управления Команды длиной в три слова Команды изменения содержимого РОН Команды обработки данных Команды выполнения операций со стеком Команды выполнения операций в АЛУ Команды передачи управления Команды изменения содержимого прогр. регистра Рисунок 8 Команды ввода-вывода Команды управления, часто называемые командами перехода, позволяют выполнять различные действия в соответствии со значением внешних сигналов или выработанных внутри системы условий. Все команды управления делятся на команды безусловного и условного перехода. К командам безусловного перехода относятся: БЕЗУСЛОВНЫЙ ПЕРЕХОД (БП), по которой в программный счетчик записывается содержимое адресного поля команды БП, т.е. обеспечивается переход в программе по адресу, указанному в команде; БЕЗУСЛОВНЫЙ ПЕРЕХОД С ВОЗВРАТОМ (переход к подпрограмме), по которой в программный счетчик записывается новое содержимое (адрес первой команды подпрограммы), но в отличие от команды БП в памяти сохраняется состояние программного счетчика и некоторых других регистров. При выполнении подпрограммы по ее последней команде ВОЗВРАТ восстанавливается содержимое программного счетчика и всех регистров. 19 Команды условного перехода проверяют состояние какого-либо разряда регистра, флагового триггера или другого параметра. От результата проверки зависит, будет выполняться переход или нет. Обычно переход осуществляется, если результат проверки соответствует указанному в команде условию. В эту подгруппу команд управления входят: УСЛОВНЫЙ ПЕРЕХОД (УП) по адресу. В коде команды УП обязательно указывается проверяемое условие, в качестве которого в МП используются нулевое или ненулевое значение результата, положительный или отрицательный знак результата, наличие или отсутствие сигналов переноса, переполнения и др. При выполнении условия в программный счетчик записывается содержимое адресного поля команды УП, т.е. обеспечивается переход в программе по адресу указанному в команде. При невыполнении условия управление передается следующей команде программы; УСЛОВНЫЙ ПЕРЕХОД С ВОЗВРАТОМ, которая отличается от команды БЕЗУСЛОВНЫЙ ПЕРЕХОД С ВОЗВРАТОМ тем, что переход к подпрограмме происходит только при выполнении указанного условия. Обычно в систему команд МП включается еще несколько вспомогательных команд, которые позволяют управлять состоянием регистров или триггеров влияющих на выполнение условных переходов, например: УСТАНОВИТЬ ФЛАГ, СБРОСИТЬ ФЛАГ, УСТАНОВИТЬ СТАРШИЙ РАЗРЯД АККУМУЛЯТОРА, СБРОСИТЬ СТАРШИЙ РАЗРЯД АККУМУЛЯТОРА и др. Команды обработки данных делятся на арифметические и логические. К арифметическим относятся: СЛОЖИТЬ содержимое двух регистров или регистра и ячейки памяти; ВЫЧЕСТЬ из содержимого ячейки памяти или регистра содержимое регистра; УВЕЛИЧИТЬ НА 1 (ИНКРЕМЕНТ) содержимое ячейки памяти или регистра (указателя стека, индексного регистра, аккумулятора); УМЕНЬШИТЬ НА 1 (ДЕКРЕМЕНТ) содержимое ячейки памяти или регистра; СЛОЖИТЬ С УЧЕТОМ ПЕРЕНОСА, по которой выполняется сложение с учетом состояния триггера переноса. Это позволяет легко организовать обработку чисел большой длины; ВЫЧЕСТЬ С УЧЕТОМ ЗАЕМА; СДВИГ содержимого ячейки памяти или регистра (обычно на один разряд). В подгруппу логических команд входят команды: И (ЛОГИЧЕСКОЕ УМНОЖИТЬ), по которой выполняется операция конъюнкции между содержимым двух регистров или ячейки памяти и регистра; ИЛИ (ЛОГИЧЕСКИ СЛОЖИТЬ), по которой выполняется операция дизъюнкции между содержимым двух регистров или ячейки памяти и регистра; НЕРАВНОЗНАЧНОСТЬ, по которой производится поразрядное сравнение содержимого двух регистров или ячейки памяти и регистра; ИНВЕРСИЯ содержимого ячейки памяти или регистра. Виды адресации 20 Одной из важнейших архитектурных характеристик МП является перечень возможных способов обращения к памяти или видов адресации. Возможности МП по адресации существенны с двух точек зрения. Во-первых, большой объем памяти требует большой длины адреса, так как n-разрядный адрес позволяет обращаться к памяти емкостью 2n слов. Типовые 8-разрядные слова МП дают возможность непосредственно обращаться только к 256 ячейкам памяти, что явно недостаточно. Если учесть, что обращение к памяти является наиболее часто встречающейся операцией, то очевидно, что эффективность использования МП во многом определяется способами адресации к памяти большого объема при малой разрядности МП. Во-вторых, для удобства программирования желательно иметь простую систему формирования адресов данных при работе с массивами, таблицами и указателями. Рассмотрим способы решения этих проблем. Если адресное поле в команде является ограниченным и недостаточным для непосредственного обращения к любой ячейке памяти, то память в таких случаях разбивают на страницы, где страницей считается 2n ячеек памяти. Для согласования адресного поля команды малой разрядности с памятью большого объема (для решения “страничной” проблемы) в МП применяются различные виды адресации: Прямая адресация к текущей странице. При такой адресации программный счетчик разбивается на два поля; старшие разряды указывают номер страницы, а младшие - адрес ячейки на странице. В адресном поле команды размещается адрес ячейки на странице, а адрес страницы должен быть установлен каким-то другим способом, например с помощью специальной команды. Прямая адресация с использованием страничного регистра. В МП должен быть предусмотрен программно доступный страничный регистр, загружаемый специальной командой. Этот регистр добавляет к адресному полю команды несколько разрядов, необходимых для адресации ко всей памяти. Прямая адресация с использованием двойных слов. Для увеличения длины адресного поля команды под адрес отводится дополнительное слово (а если нужно, то и два). Адресация относительно программного счетчика. Адресное поле команды рассматривается как целое со знаком, которое складывается с содержимым программного счетчика для формирования исполнительного адреса. Такой способ относительной адресации создает плавающую страницу и упрощает перемещение программ в памяти. Адресация относительно индексного регистра. Исполнительный адрес образуется суммированием содержимого индексного регистра и адресного поля команды, рассматриваемого как целое со знаком. Индексный регистр загружается специальными командами. Косвенная адресация. При косвенной адресации в адресном поле команды указывается адрес на текущей странице, по которому хранится исполнительный адрес. В поле команды при этом требуется дополнительный разряд - признак косвенной адресации. Исполнительный адрес может храниться не в ячейке памяти, а в регистре общего назначения. В этом случае косвенная адресация называется регистровой. Структура и форматы команд МП КР580ВМ80 21 Система команд МП серии КР580ВМ80 содержит команды трех форматов: однобайтные, двухбайтные и трехбайтные. Содержимое первого байта указывает на формат команды, код операции, вид адресации и регистры или регистровые пары, если они участвуют в выполнении операции. При этом невозможно указать конкретные разряды, которые отводятся под первые три из указанных составляющих команды, потому что они могут находиться в любых разрядах команды. Но, несмотря на это, будем считать, что они кодируются как одно поле, которое называется полем кода операции. Варианты форматов первого байта команды приведены на рисунке 9. Если в выполнении операции участвуют регистры, то один или два из них могут быть указаны в первом байте команды. При этом под номера регистров в поле команды отводятся вполне определенные разряды: три младших разряда (b2 - b0) кодируют номер регистра источника, содержащего операнд, а три средних (b5 - b3) - номер регистра-приемника, в который засылается результат операции. В тех случаях, когда оба или один из этих регистров не участвуют в выполнении операции, соответствующие разряды используются под код операции. Принято следующее кодирование регистров: 000 - регистр В, 100 - регистр Н, 001 - регистр С, 101 - регистр L, 010 - регистр D, 110 - ячейка памяти, 011 - регистр Е, 111 - аккумулятор А. Код 100 является признаком косвенной адресации к памяти с помощью 16-разрядного адреса, размещенного в регистрах Н и L. В зависимости от расположения этого кода в команде, обращение к соответствующей ячейке памяти производится или за операндом, или для записи результатов операции. 22 Форматы однобайтных команд DDD Поле кода операции SSS 7 6 5 4 3 2 1 0 DDD - трехбитный номер регистра-приемника DDD SSS SSS - трехбитный номер регистра-источника ССС - трехбитный указатель условия передачи управления CCC NNN NNN - трехбитный код, определяющий адрес вектора прерывания RP 7 6 5 4 3 2 1 0 RP - двухбитный указатель, адресующий пару регистров Форматы двухбайтных команд DDD Непосредствен ный операнд Непосредствен ный операнд Форматы трехбайтных команд CCC RP Младш.полуадрес Старш.полуадрес Младш.полуадрес Старш.полуадрес Младш.полуадрес Старш.полуадрес Р исунок 9 - Форматы команд МП серии КР580 ВМ80 Ряд команд МП предусматривает обработку или передачу чисел двойной длины. В этих случаях пары регистров В и С, D и Е или Н и L объединяются в 16-разрядные регистры, имеющие номера 00, 01 и 10 соответственно. Под номера регистровых пар в командах отводятся разряды b2 и b1 (регистр-источник), b5 и b4 (регистр-приемник), а разряды b0 и b3 используются для указания кода операции. К двухбайтным командам в МП относятся команды с непосредственной адресацией и команды ввода-вывода. Соответственно второй байт команды этой группы содержит 8разрядный операнд или 8-разрядный адрес устройства ввода или вывода. В трехбайтных командах второй и третий байты содержат 16-разрядные адреса (в командах с прямой адресацией) или 16-разрядные операнды (в командах загрузки регистровых пар и указателя стека). После выполнения каждой операции, а АЛУ вырабатывается пять признаков, значения которых могут влиять на выполнение последующих команд обработки информации и условной передачи управления. Однако следует иметь ввиду, что различные команды, поразному влияют на отдельные признаки. 23 Для удобства сохранения и восстановления состояния МП во время прерываний и перехода к подпрограммам все указанные признаки сохраняются в специальном регистре регистре признаков. Расположение признаков в разрядах регистра приведено в таблице. D7 S D6 Z D5 0 D4 AC D3 0 D2 P D1 1 D0 CY где, S - признак “знака” (принимает значение старшего разряда результата); Z - признак нулевого результата; АС - признак вспомогательного переноса (если есть перенос между тетрадами байта, то АС=1, иначе АС=0; Р - признак четности результата (если число единиц в байте результата четно, то Р=1, иначе Р=0); С - признак переноса или займа (если при выполнении команды возник перенос из старшего разряда или заем в старший разряд то С=1, иначе С=0). Примечание: Для команд логического умножения признак вспомогательного переноса АС принимает значение четвертого разряда результата. Полностью система команд МП серии КР580ВМ80 приведена в приложении учебного пособия "Микропроцессоры и микропроцессорные системы". Там же для каждой команды указывается как, после ее выполнения, изменяется значение каждого признака: устанавливается в соответствии с результатом операции (+), не изменяется (-), сбрасывается в нуль (0) или устанавливается в единицу (1). В общем случае команда должна содержать следующую информацию: -код операции, указывающий операцию, которую должен выполнить МП; -адреса двух операндов (слагаемых, вычитаемых и т.д.). Если какой- либо из операндов является константой, то вместо его адреса в команде может быть задано значение самого операнда. Однако это обстоятельство должно быть отображено в коде операции, что бы МП использовал соответствующую часть команды с указанным ее назначения; -адрес ячейки памяти в которую должен быть помещен результат операции; -адрес следующей команды. Т.е. команда в общем случае является четырехадресная. Однако, такая структура команд приводит к более длинному формату команд, что, в свою очередь, сопряжено с более сложным процессом их обработки и структурой процессора. Поэтому, в МП технике наибольшее распространение получили безадресные и одноадресные команды, позволяющие построить простой процессор. Однако, при выполнении сложных операций находят применение различные форматы команд. В системе команд МП серии 580 имеются однобайтные, двухбайтные и трехбайтные команды. Информация о способе адресации выполняемой команды содержится в коде операции первого байта команды. Для ускорения вычислений некоторые операнды хранятся в блоке РОН. Команды, работающие с этими операндами, используют укороченные адресные коды (регистровую адресацию). 24 Эти команды позволяют исключить сравнительно длинный цикл обращения к ОЗУ и тем самым существенно повысить скорость выполнения операций. В связи с ограниченной разрядностью РОН и при работе с большим массивом данных, используются другие методы адресации, которые позволяют обращаться к операндам, расположенным во внешней по отношению к МП памяти. Наиболее распространенной является косвенная регистровая адресация, которая использует регистровую пару HL. 25 КОМАНДЫ 0 МИКРОПРОЦЕССОРА 2 3 КР580ВМ80А 5 6 7 8 9 А В С D E F 0 NOP LXI B,& STAX B INX B INR B DCR B MVI B,# RLC - DAD B LDAX B DCX B INR C DCR C MVI C,# RRC 0 1 - LXI D,& STAX D INX D INR D DCR D MVI D,# RAL - DAD D LDAX D DCX D INR E DCR E MVI E,# RAR 1 2 - LXI H,& SHLD * INX H INR H DCR H MVI H,# DAA - DAD H LHLD * DCX H INR L DCR L MVI L, # CMA 2 3 - LXI SP , & STA * INX SP INR M DCR M MVI M,# STC - DAD SP LDA * DCX SP INR A DCR A MVI A, # CMC 3 4 MOV B,B MOV B,C MOV B,D MOV B,E MOV B,H MOV B,L MOV B,M MOV B ,A MOV C,B MOV C,C MOV C,D MOV C,E MOV C,H MOV C,L MOV C,M MOV C ,A 4 5 MOV D,B MOV D,C MOV D,D MOV D,E MOV D,H MOV D,L MOV D,M MOV D,A MOV E,B MOV E,C MOV E,D MOV E,E MOV E,H MOV E,L MOV E,M MOV E,A 5 6 MOV H,B MOV H,C MOV H,D MOV H,E MOV H,H MOV H,L MOV H,M MOV H,A MOV L, B MOV L, C MOV L, D MOV L, E MOV L, H MOV L, L MOV L, M MOV L,A 6 7 MOV M,B MOV M,C MOV M,D MOV M,E MOV M,H MOV M,L HLT MOV M ,A MOV A, B MOV A, C MOV A, D MOV A, E MOV A, H MOV A, L MOV A, M MOV A,A 7 8 ADD B ADD C ADD D ADD E ADD H ADD L ADD M ADD A ADC B ADC C ADC D ADC E ADC H ADC L ADC M ADC A 8 9 SUB B SUB C SUB D SUB E SUB H SUB L SUB M SUB A SBB B SBB C SBB D SBB E SBB H SBB L SBB M SBB A 9 A ANA B ANA C ANA D ANA E ANA H ANA L ANA M ANA A XRA B XRA C XRA D XRA E XRA H XRA L XRA M XRA A A B ORA B ORA C ORA D ORA E ORA H ORA L ORA M ORA A CMP B CMP C CMP D CMP E CMP H CMP L CMP M CMP A B C RNZ POP B JNZ * JMP * CNZ * PUSH B ADI # RST 0 RZ RET JZ * - CZ * CALL * ACI # RST 1 C D RNC POP D JNC * OUT N CNC * PUSH D SUI # RST 2 RC - JC * IN N CC * - CBI # RST 3 D E RPO POP H JPO * XTHL CPO * PUSH H ANI # RST 4 RPE PCHL JPE * XCHG CPE * - XLI # RST 5 E F RP POP PSW JP * DI CP * PUSH PSW ORI # RST 6 RM SPHL JM * EI CM * - CPI # RST 7 F 0 1 2 3 4 5 6 7 8 9 A B C D E F 1 4 ПРОГРАММИРУЕМОЕ УСТРОЙСТВО ВВОДА-ВЫВОДА ПАРАЛЛЕЛЬНОЙ ИНФОРМАЦИИ КР580ВВ55 БИС КР580ВВ55 представляет собой программируемый периферийный адаптер (ППА), используемый для ввода-вывода параллельной информации. Схема позволяет осуществлять обмен 8-разрядными данными по трем портам (каналам): А, В и С. Направление обмена и режима работы для каждого канала задается программно. Каналы служат для передачи, как данных, так и управляющих слов. Упрощенно схема состоит из регистра управления и трех регистров, предназначенных для ввода-вывода данных. Структурная схема ППА КР580ВВ55 приведена на рисунке 10,а, а ее условное графическое обозначение на рисунке 10,б. D0 - D7 А0 А1 ЧТ ЗП Буфер данных Сема выбора канала и управления ВУ КАНАЛЫ A КА0-КА7 D0 D1 D2 D3 D4 D5 B КB0-КB7 D6 D7 A0 R A1 Схема управления каналом С C КC0-КC3 C КC4-КC7 ЧТ ЗП ВУ R КА0 ППА КА1 КА2 КА3 КА4 КА5 КА6 КА7 КB0 КB1 КB2 КB3 КB4 КB5 КB6 КB7 КC0 КC1 КC2 КC3 КC4 КC5 КC6 КC7 б) а) схема программируемого параллельного Рисунок 10 - Упрощенная интерфейса КР580ВВ55 (а) и его условное обозначение (б) Назначение выводов: D0-D7 - двунаправленная магистраль данных для передачи данных, управляющих слов и информации состояния; КА0-КА7 – квазидвунаправленный порт А; КВ0-КВ7 - квазидвунаправленный порт В; КС0-КС7- квазидвунаправленный порт С (магистрали каналов передачи данных, управляющих сигналов и сигналов запроса на прерывание от ВУ и МП); А0-А1 - входы, необходимые для выбора одного из портов А, В, С или регистра управляющих слов РУС (на приведенном рисунке РУС входит в состав схемы выбора канала и управления); ЧТ - вход, на который подается сигнал на выдачу данных из внутренних регистров схемы на ШД; ЗП - вход, на который подается сигнал на ввод данных во внутренние регистры схемы; ВУ - вход разрешения работы схемы; R - вход, используемый для начальной установки схемы. При подаче лог.1 все порты настраиваются на ввод информации в нулевом режиме. Упрощенная программная модель и интерфейс схемы КР580ВВ55 состоит из трех регистров А, В, С, предназначенных для ввода-вывода данных и регистра управляющего слова (РУС). Регистр канала С может быть подразделен на два 4-разрядных регистра вводавывода данных КС0-КС3 и КС4-КС7, доступ к которым осуществляется как к независимым регистрам. Кроме того, имеется возможность подразделения трех каналов на две группы: - группа А, которая включает канал А и КС4-КС7, где линии КС4-КС7 выполняют функции управления обменом по КА0-КА7; - группа В, которая включает канал В и КС0-КС3, где линии КС0-КС3 выполняют функции управления обменом по КВ0-КВ7. Режимы работы каналов задаются путем записи управляющего слова в РУС. Формат управляющего слова УС приведен на рис.11. УС, где в старшем разряде “1”, программирует группы А, В и С для параллельного обмена в нескольких режимах: Режим 0. Линии РА7...0, РВ7...4 и РС...0 индивидуально настаиваются на простой ввод или вывод в соответствии со значениями разрядов D4, D3, D1, D0 управляющего слова (рис.4.28). D7 D6 D5 D4 D3 D2 D1 D0 Группа В КС0 - КС3 (“1”- ввод, “0”- вывод) Порт В (“1”- ввод, “0”- вывод) Выбор режима “0”- режим 0, “1” - режим 1 Группа А КС4 - КС7 (“1”- ввод, “0”- вывод) Порт А “1” - установка режима D7 D6 D5 D4 D3 D2 D1 D0 (“1”- ввод, “0”- вывод) Выбор режима "0"- режим 0, "01" - режим 1 “10” или “11” - режим 2 Флаг сброса - установки “0” - сброс, “1” - установка Безразличное состояние “0” - установка-сброс битов регистра С Выбор бита D3 D2 D1 0 0 0 0 0 1 0 1 0 .................. 1 1 1 Рисунок 11 - Формат управляющего слова Бит порта С 0 1 2 ............ 7 В режиме <<0>> с помощью УС=10010001 линии РА7...0 и РС3...0 настраивается на ввод, а линии РВ7...0, РС7...4-на вывод. Обмен с МП осуществляется по инициативе МП обращением к РА, РВ и РС. В режиме 0 могут работать все три порта, причем порт С разделяется на два независимых 4-битных порта. Выводимые данные фиксируются в регистрах- защелках этих портов, а вводимые данные не запоминаются. Режим 0 применяется в программно-управляемом вводе-выводе с медленнодействующими периферийными устройствами. Режим 1. Этот режим позволяет осуществлять обмен данными по каналам А и В с помощью сигналов управления, передаваемых по каналу С. При расширенном интерфейсе возможно информирование МП о готовности данных по вводу. Режим 1 предназначен для стробируемого ввода-вывода однонаправленных передач данных, инициируемых прерываниями. Режим 2. Канал А используется для двунаправленной передачи данных, а канал С - для записи управляющих сигналов, обеспечивающих передачу данных по каналу А. (В режиме 2 может работать только канал А.) Вводимые и выводимые данные фиксируются в регистрах-защелках. Наиболее часто группы А и В используются в режиме 0 (простого ввода или вывода). Формат УС предназначен для побитового управления каналом С. В разрядах D3...D1 содержится двоичный код NNN номера бита порта С, который должен быть установлен в состояние, определяемое разрядом D0 УС. Интерфейс БИС КР580ВВ55 включает двунаправленную шину данных D7...D0, линии управления направления передачи по шине данных WR (запись), RD (чтение), вход системного сброса R, сигнал выборки микросхемы CS и разряды шины адреса А1, А0 для выборки регистров (00 -регистр А, 01- регистр В, 10 - регистр С, 11 - регистр УС). Такой набор линий интерфейса позволяет легко подключать до 64 микросхем КР580ВВ55 и МП КР580ВМ80А. В состав базового комплекта серии КР580 входит 8-ми разрядный параллельный процессор КР580ВМ80А, программируемый последовательный интерфейс КР580ВВ51, программируемый таймер КР580ВИ53, программируемый параллельный интерфейс КР580ВВ55А, программируемый контроллер прямого доступа к памяти КР580ВТ57, программируемый контроллер прерываний КР580ВН59, системный контроллер КР580ВК28, генератор тактовых импульсов КР580ГФ24, шинный формирователь КР580ВА86, буферный регистр КР580ИР82. На основе этих специализированных БИС разрабатываются микропроцессорные системы. Микро-ЭВМ серии К1816 (MCS-48) 29 Микропроцессорный комплект серии КР1816 состоит из микросхем КР1816ВЕ35, КР1816ВЕ39, КМ1816ВЕ48, КР1816ВЕ49. Существуют многочисленные зарубежные аналоги этих микросхем, в частности БИС фирмы Intel: 8035, 8039, 8048, 8049. Эти БИС представляют собой однокристальную 8-ми разрядную микро-ЭВМ, содержащую центральный процессор, ОЗУ данных, интерфейс ввода-вывода, 8-ми разрядный таймер, тактовый генератор, программную память, векторную систему прерываний. Перечисленные микросхемы имеют одинаковую структуру и отличаются быстродействием, объемом ОЗУ, наличием или отсутствием памяти программ. Например, БИС КР1816ВЕ48 содержит электрически перепрограммируемое ППЗУ емкостью 1К с ультрафиолетовым стиранием информации. На рис.12 показано графическое обозначение микросхем серии. Рис.12 На рисунке приняты следующие обозначения выводов БИС: Т0 – используется как вход при выполнении команд JT0, JNT0 и как выход тактовых сигналов после выполнения команды ENT0 CLK; BQ1,BQ2 – используются для подключения кварцевого резонатора, LC – цепи или внешнего генератора; SR- сигнал инициализации; SS – используется для организации пошагового режима; INT – сигнал прерывания; EMA- сигнал обращения к внешней памяти программ; RD – сигнал чтения из внешней памяти данных; WR – сигнал записи во внешнюю память данных; PME – сигнал чтения из внешней памяти программ; ALE – стробирующий сигнал адреса; P0 – восьмиразрядный двунаправленный трехстабильный порт; Р1- восьмиразрядный квазидвунаправленный порт; Р2 – восьмиразрядный квазидвунаправленный порт; GND – общий; PR – используется как выход для расширения каналов ввода/вывода и как вход для программирования ППЗУ КР1816ВЕ48; Udd – напряжение питания +5В (при программировании КР1816ВЕ48 30 +25В); Т1 – вход для счетчика после выполнения команды STRT CNT, а также сигнал проверяемый командами JT1, JNT1; Ucc – напряжение питания +5В. Структурная схема микро-ЭВМ серии К1816 показана на рис.13. Рис.13 Здесь, приняты следующие обозначения: ППЗУ- постоянное перепрограммируемое запоминающее устройство; ДС- дешифратор; ОЗУ- оперативное запоминающее устройство; АЛУ- арифметико-логическое устройство; ДК- десятичный корректор; ССПслово состояния процессора; РА- регистр адреса; СК- двенадцати разрядный счетчик команд; А- восьми разрядный регистр, аккумулятор; Т – вспомогательный регистр; РКрегистр команд; УУ- устройство управления. Микро-ЭВМ также содержит восьмиразрядный таймер и три восьмиразрядных порта для подключения внешних устройств. Микро-ЭВМ допускает расширение памяти программ до 4К (включая внутреннюю память) и есть возможность подключить внешнюю память данных объемом 256 байт. Память программ разбита на два банка по 2К в каждом, а каждый банк состоит из восьми страниц объемом 256 байт. Выбор банков осуществляется программным путем. ОЗУ на кристалле содержит два банка регистров общего назначения, переключение банков осуществляется программно, содержит восьми уровневый стек и ОЗУ данных. ССП предназначено для хранения флажков: СУ-флаг переноса из старшего бита; АС- флаг арифметического переноса; F0-флаг пользователя. Также в ССП находится селектор банка РОН и трех разрядный указатель стека. Команды микро-ЭВМ также оперируют флажками, такими как: Z- флаг нуля; B- флаг наличия единицы в проверяемом бите аккумулятора; F1- флаг пользователя и FT- флаг переполнения таймера. Микроконтроллеры фирмы Microchip Technology. Производимое фирмой Microchip Technology семейство интегральных микросхем PIC16FXX, представляет собой восьмиразрядные микроконтроллеры с RISC архитектурой. Это 31 семейство микроконтроллеров отличается низким энергопотреблением, высокой скоростью выполнения команд, низкой ценой. Микроконтроллеры имеют встроенное ПЗУ для хранения программ и энергонезависимое ОЗУ данных. Одним из простейших представителей этого семейства является микроконтроллер PIC16F84. Контроллер выполнен по КМОП технологии, имеет внутреннее 1Кх14 бит электрически перепрограммируемое ПЗУ (EEPROM), предназначенное для хранения выполняемой программы и 64 байта энергонезависимого ОЗУ данных. Команды, выполняемые контроллером, состоят из одного слова шириной 14 бит и выполняются в течение одного цикла (400нс. при частоте синхронизации 10 Мгц.), команды передачи управления выполняются за два цикла. Длительность цикла составляет четыре периода тактовой частоты. Контроллер сохраняет работоспособность в диапазоне частот от 0 до 10 Мгц. Контроллер обеспечивает прерывания от 4-х источников и имеет для их обслуживания восьмиуровневый аппаратный стек. Содержит 8-битный таймер/счетчик с 8битным программируемым предварительным делителем. Для подключения периферийных устройств (датчиков, клавиатур, исполнительных механизмов) контроллер имеет 13 линий, программно настраиваемых на ввод или вывод информации. Высокая нагрузочная способность этих линий (20мА) упрощает схемную реализацию драйверов ввода/вывода. Разработки устройств на базе этих контроллеров поддерживаются ассемблером, программаторами и программным симулятором (PIC Simulator IDE), который позволяет проводить отладку программ и моделировать поведение внешних устройств, подключенных к портам контроллера. На Рис.14 показана функциональная схема контроллера. Рис.14 На схеме приняты следующие обозначения: выводы OSC1 и OSC2 предназначены для подключения кварцевого резонатора или RC-цепочки, или генератора тактовых импульсов. Выводы RA0-RA4 образуют разряды порта А (PORTA). TOCK1 может также использоваться как вход таймера/счетчика. Выводы RB0-RB7 являются разрядами порта В (PORTB). INTвход внешнего прерывания. RB4, RB5 могут использоваться как входы прерывания по 32 изменению сигнала. RB6 - вход прерывания по изменению сигнала или вход тактового сигнала при программировании контроллера. RB7 - вход прерывания по изменению сигнала или сигнал данных при программировании. MCLR - вход сигнала сброса или напряжение программирования, при программировании. VDD- питания. GND- общий вывод. На рис.15 показан простой пример применения контроллера. Схема содержит цифровой индикатор, подключенный к разрядам порта «В» и матричную клавиатуру (4х4). Клавиши клавиатуры пронумерованы символами от 0 до F. Опрос клавиатуры осуществляется методом сканирования при этом разряды порта « А» (RA0-RA3) контроллера должны быть настроены на ввод, а разряды порта «В» на вывод информации. Разряд RA4 порта «А» должен быть настроен на вывод этот разряд позволяет разрешать (выводится лог.1) или запрещать (выводится лог.0) работу индикатора. Рис.15 Ниже приведен текст программы, отображающей на индикаторе цифры: 0, 1, 2, 3, что зависит от номера нажатой клавиши клавиатуры (0, 1, 2, 3). Текст ассемблер программы bsf status,5h movlw 0fh movwf trisa ; разряды 0-3 порта А на ввод movlw 00h movwf trisb ; порт В на вывод bcf status,5h m0: clrf porta ; очистка порта А (запрет индикатора) movlw 01h movwf portb ; выбор кнопок 0, 1, 2, 3 (вывод лог.1 в RB0) btfss porta,0h ; проверка RA0 goto m1 33 m1: m2: m3: m10: movlw 3fh movwf portb ; вывод символа «0» goto m10 btfss porta,1h ; проверка RA1 goto m2 movlw 06h movwf portb ; вывод символа «1» goto m10 btfss porta,2h ; проверка RA2 goto m3 movlw 5bh movwf portb ; вывод символа «2» goto m10 btfss porta,3h ; проверка RA3 goto m0 movlw 4fh movwf portb ; вывод символа «3» movlw 10h movwf porta ; разрешить работу индикатора goto m0 34