К.А. ПЕТРОВ Научный руководитель – В.Я. СТЕНИН, д.т.н., профессор

реклама

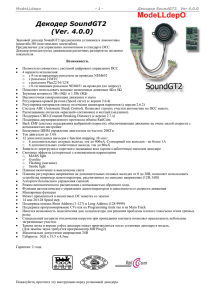

К.А. ПЕТРОВ Научный руководитель – В.Я. СТЕНИН, д.т.н., профессор Национальный исследовательский ядерный университет «МИФИ», НИИ системных исследований РАН, Москва, СИНТЕЗ ТОПОЛОГИЙ ДЕКОДЕРОВ КОДА ХСЯО Представлены результаты синтеза топологий декодеров кода Хсяо, содержащих упрощенные элементы конструкции, что позволило снизить аппаратурные затраты до 40% при сохранении быстродействия и функциональности. Использование оперативных запоминающих устройств (ОЗУ) с элементами помехоустойчивого кодирования обеспечивает повышение достоверности хранящейся информации и является обязательным атрибутом сбоеустойчивых вычислительных систем. Также использование помехоустойчивого кодирования является одной из обязательных мер для создания высокопроизводительных микропроцессоров для суперЭВМ [1]. При этом повышаются требования к быстродействию и аппаратурным затратам элементов помехоустойчивого кодирования при сохранении параметров надежности функционирования ОЗУ. Наиболее распространенными кодами для повышения достоверности хранящейся информации в ОЗУ являются линейные блочные коды Хсяо [2]. В литературе широко представлены математические свойства помехоустойчивых кодов, в частности кодов Хсяо. Схемотехника кодердекодеров и ее особенности с точки зрения быстродействия и аппаратурных затрат представлены недостаточно полно [3, 4]. Ранее с целью снижения аппаратурных затрат декодера было предложено использовать укороченную и упрощенную схемы вычисления вектора ошибки [5]. В данной статье представлены результаты синтеза топологий декодеров кода Хсяо для информационных слов наиболее распространенных размеров от 4 до 64 бит. Для моделирования, синтеза топологий и их сравнительного анализа были выбраны четыре конфигурации декодера Хсяо, содержащие различные наборы элементов и связей между ними. Для всех конфигураций декодера были разработаны поведенческие модели кодов Хсяо на языке Verilog для информационных слов от 4 до 64 бит. Был проведен синтез топологии в САПР Cadence Encounter по проектным нормам 0,18 мкм КМОП. Результаты синтеза топологии, в процентах от конфигурации №1 для каждого информационного слова приведены на рис. 1. 100 90 80 70 60 50 40 30 20 10 0 4 бит 8 бит 16 бит 32 бит конфигурация №1, % конфигурация №2, % конфигурация №3, % конфигурация №4, % 64 бит Рис. 1. Диаграмма зависимости площадей декодеров Хсяо различной конфигурации от размера информационного слова, где конфигурация №1 взята за 100% Синтез топологий показал, что использование в декодерах Хсяо укороченной схемы исправления однократной ошибки, упрощенной схемы вычисления вектора ошибки, а также схемы формирования сигнала ошибки без вектора ошибки (конфигурация №4) позволяет снизить аппаратурные затраты на декодер на 25-40% для ОЗУ с разрядностью информационных слов от 4 до 64 бит при сохранении быстродействия и функциональности декодера. Изменением параметров синтеза возможно вместо снижения аппаратурных затрат добиться повышения быстродействия декодера, что приводит к снижению времени доступа к ОЗУ. 1. 2. 3. 4. 5. Список литературы Бобков В. Г. Электроника, микро- и наноэлектроника. Сборник на-учных трудов / под ред. В. Я. Стенина. – М.: НИЯУ МИФИ, 2012. – С. 129-140. Hsiao M.Y., A Class of Optimal Minimum Odd-Weight-Column SEC-DED Codes // IBM J. Res. Develop. 1970. Vol. 14. P. 395–401. Хетагуров Я. А. Руднев Ю. П. Повышение надежности цифровых устройств методами избыточного кодирования // М.: Энергия, 1974. -240 с. Петров К. А. Особенности помехоустойчивого кодирования информации в ОЗУ // Электроника, микро- и наноэлектроника. Сборник научных трудов / под ред. В. Я. Стенина. – М.: НИЯУ МИФИ, 2010. – С. 167-172 Петров К.А. Упрощенная схема вычисления вектора ошибки вдекодерах Хсяо // Электроника, микро- и наноэлектроника. Сборник научных трудов / под ред. В. Я. Стенина. – М.: НИЯУ МИФИ, 2013. – С. 221-223.