литература - kosrad.ru

реклама

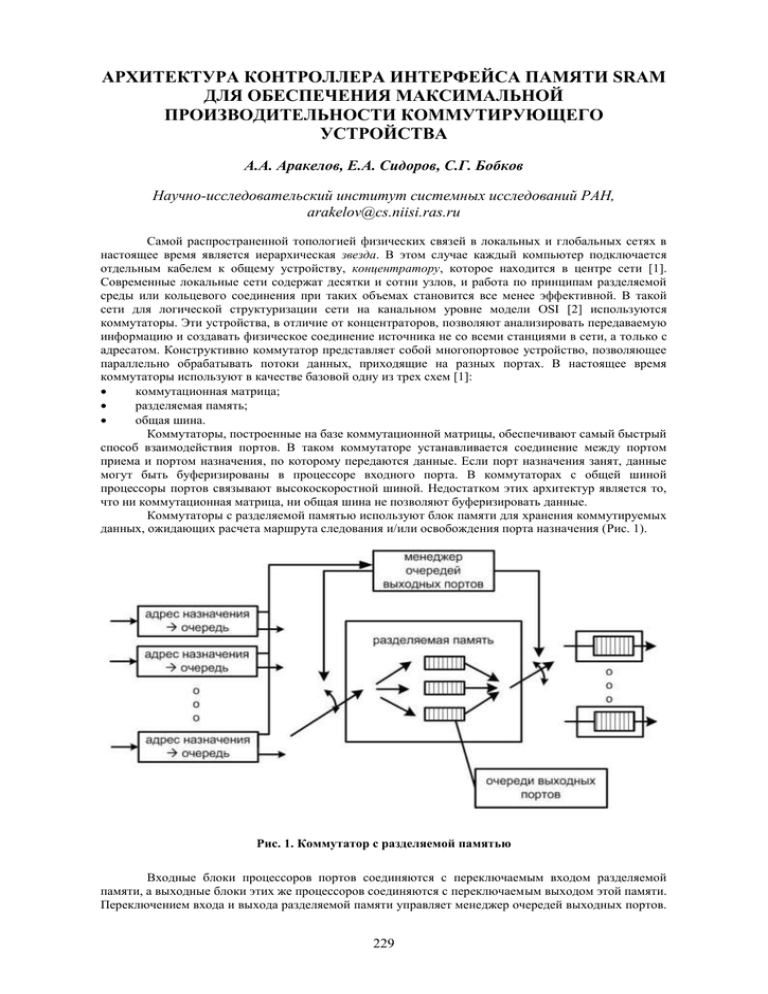

АРХИТЕКТУРА КОНТРОЛЛЕРА ИНТЕРФЕЙСА ПАМЯТИ SRAM ДЛЯ ОБЕСПЕЧЕНИЯ МАКСИМАЛЬНОЙ ПРОИЗВОДИТЕЛЬНОСТИ КОММУТИРУЮЩЕГО УСТРОЙСТВА А.А. Аракелов, Е.А. Сидоров, С.Г. Бобков Научно-исследовательский институт системных исследований РАН, [email protected] Самой распространенной топологией физических связей в локальных и глобальных сетях в настоящее время является иерархическая звезда. В этом случае каждый компьютер подключается отдельным кабелем к общему устройству, концентратору, которое находится в центре сети [1]. Современные локальные сети содержат десятки и сотни узлов, и работа по принципам разделяемой среды или кольцевого соединения при таких объемах становится все менее эффективной. В такой сети для логической структуризации сети на канальном уровне модели OSI [2] используются коммутаторы. Эти устройства, в отличие от концентраторов, позволяют анализировать передаваемую информацию и создавать физическое соединение источника не со всеми станциями в сети, а только с адресатом. Конструктивно коммутатор представляет собой многопортовое устройство, позволяющее параллельно обрабатывать потоки данных, приходящие на разных портах. В настоящее время коммутаторы используют в качестве базовой одну из трех схем [1]: коммутационная матрица; разделяемая память; общая шина. Коммутаторы, построенные на базе коммутационной матрицы, обеспечивают самый быстрый способ взаимодействия портов. В таком коммутаторе устанавливается соединение между портом приема и портом назначения, по которому передаются данные. Если порт назначения занят, данные могут быть буферизированы в процессоре входного порта. В коммутаторах с общей шиной процессоры портов связывают высокоскоростной шиной. Недостатком этих архитектур является то, что ни коммутационная матрица, ни общая шина не позволяют буферизировать данные. Коммутаторы с разделяемой памятью используют блок памяти для хранения коммутируемых данных, ожидающих расчета маршрута следования и/или освобождения порта назначения (Рис. 1). Рис. 1. Коммутатор с разделяемой памятью Входные блоки процессоров портов соединяются с переключаемым входом разделяемой памяти, а выходные блоки этих же процессоров соединяются с переключаемым выходом этой памяти. Переключением входа и выхода разделяемой памяти управляет менеджер очередей выходных портов. 229 Такой коммутатор обладает большей задержкой передачи данных, но меньшими потерями данных. В таких коммутаторах обработка данных делится на три основных действия: прием данных — процессоры входных портов записывают входящие пакеты данных в разделяемую память; расчет маршрута и коммутация — коммутирующее ядро работает только с дескрипторами данных (включающими необходимую информацию об источнике данных, назначении данных и адрес хранения кадра в запоминающем устройстве); процессоры выходных портов получают в результате коммутации дескриптор кадра, извлекают из него адрес хранения данных в запоминающем устройстве (ЗУ), считывают данные и передают их в среду. К производительности запоминающего устройства при такой архитектуре предъявляются особые требования. ЗУ должно обеспечить достаточную пропускную способность, чтобы входящие порты успевали получать доступ к памяти для записи данных без потерь; в то же время выходные порты должны вовремя считывать данные, чтобы не произошло прерывания данных, передаваемых в среду, до окончания блока. То есть производительность ЗУ в разы превышает производительность каждого канала. Рассмотрим требования к ЗУ для 6-портового коммутатора Gigabit Ethernet. Каждый порт, работающий в полнодуплексном режиме, одновременно принимает и передает данные со скоростью 1Гбит/с. То есть ЗУ должно обеспечивать пропускную способность 12 Гбит/с. В таких системах используется статическая память SRAM. Такая память имеет более простой интерфейс, хотя ее стоимость выше. В худшем случае 12 портов коммутатора обращаются в произвольные области памяти для записи и чтения данных, что требует дополнительных циклов активации и закрытия строк и циклов регенерации. При использовании компонентов DRAM с конвейерной обработкой данных, задержка переключения между произвольными строками составляет 2 такта при длине пакета данных в 4 такта. При такой работе динамическая память, обеспечивающая требуемую производительность коммутатора, потребует большей частоты работы по сравнению со статической памятью SRAM. Размещение блока памяти SRAM на кристалле коммутатора сопряжено с большими затратами на разработку/покупку быстродействующего блока памяти SRAM, а также предъявляет повышенные требования к производству микросхемы, в частности, требует совмещения технологии обычной логики и памяти больших объемов (для коммутатора использовалось ЗУ объемом 4 Мбайт). Использование внешней микросхемы памяти SRAM позволяет сократить такие затраты, но требует расположения элемента на печатной плате, используемой в системе. Микросхема коммутатора была спроектирована для использования с внешним ЗУ SRAM. Обычная микросхема ЗУ типа SRAM с одним 32-битным портом для чтения/записи, работающая на 200 МГц, позволяет пропускать 6,4 Гбит данных в секунду, то есть обеспечивает работу 3х портов. Для создания 6-портового коммутатора необходимо увеличить пропускную способность ЗУ в два раза. Для этого потребуется использовать одно из следующих ЗУ: двухпортовая 32-разрядная память, работающая на 200 МГц; 64-разрядная память, работающая на 200 МГц; память DDR (double-data rate) на 200 МГц; однопортовая 32-разрядная память, работающая на 400 МГц. Все эти подходы имеют свои преимущества и недостатки: Использование двухпортовой памяти упрощает работу арбитра памяти (работающего на высокой частоте), которому теперь требуется отслеживать и обрабатывать в два раза меньше запросов, но одновременно увеличивает количество сигналов, выходящих из микросхемы. При этом двухпортовая память может быть «истинно» двухпортовой, когда каждый порт ЗУ работает на чтение и на запись, или «простой» двухпортовой памятью, когда один порт работает только в режиме чтения, а второй – только записи. Для коммутирующего устройства запросы чтения и записи распределены поровну, и такое деление функциональности портов ЗУ несущественно; для других устройств такую память нужно выбирать с учетом требований проекта. Простое увеличение ширины порта ЗУ в два раза увеличивает только количество сигналов данных, выходящих из микросхемы, и оставляет прежние управляющие сигналы и адресную шину. Такой подход является относительно недорогим решением, но не упрощает работу арбитра, и требует выравнивания данных по ширине доступа к ЗУ – 64 разряда – либо введения дополнительных сигналов маски записи. Выбор микросхемы ЗУ, работающей на частоте 400 МГц, или использование памяти DDR сопряжены с технологическими трудностями, поскольку требуют проектирования не только внутреннего логического блока, способного работать на 400 МГц (что сказывается на времени проектирования и используемой технологии производства), но и более сложной разработки печатной платы, используемой в системе. Использование памяти DDR требует небольшого изменения схемы работы контроллера доступа к ЗУ. 230 Возможно комбинирование подходов, например, использование памяти DDR с более широкой шиной данных и более низкой частотой работы. Тут также требуется изменение работы контроллера доступа к ЗУ и большее количество выходных сигналов микросхемы коммутатора; кроме того, рыночная стоимость памяти DDR SRAM как компонента превышает стоимость обычной памяти SRAM в среднем в 2 раза [2004 г.]. В настоящее время на рынке предоставлены микросхемы памяти SRAM, работающие на частотах до 300 МГц (16-бит интерфейс), а при 32-битном интерфейсе – до 250 МГц (конец 2004 года). 64разрядный интерфейс не представлен в данном сегменте, и достигается установкой двух микросхем 32-х разрядной памяти параллельно, при этом контрольные сигналы (сброс, синхросигнал, адрес, сигнал записи и пр.) являются общими для двух блоков, и увеличивается только ширина шины данных. Наиболее оптимальным подходом по соотношению сложность разработки/стоимость является увеличение ширины шины данных. При этом коммутатор имеет один 64х разрядный канал обращения к ЗУ для чтения/записи, работающий на частоте 200 МГц (что в итоге дает 12,8 Гбит/с), а представленные 6 портов коммутатора используют 12 каналов обращения к памяти (для чтения и записи). Контроллер доступа к памяти обрабатывает запросы портов коммутатора на обращение к памяти и обеспечивает своевременный и непрерывный поток данных. Для обеспечения низкой стоимости разработки, необходимо, чтобы ядро микросхемы коммутатора работало на более низких частотах – 50-100 МГц. Такие частоты достигаются при помощи систем автоматизированного проектирования с гораздо меньшими усилиями, чем 200-250 МГц, требующими от разработчика больших временных затрат или использования более дорогих технологий производства. Предлагается архитектура контроллера интерфейса памяти (Рис. 2): блок интерфейса памяти для работы на требуемой высокой частоте обращения к памяти (200-250 МГц); «Внутренние» по отношению к коммутатору интерфейсы памяти, работающие на средней/требуемой частоте 50-100 МГц; Буферы синхронизации и подкачки для связывания этих двух интерфейсов. Однопортовая память SRAM требует арбитрации между 12 каналами запросов. Для равномерного распределения доступа портов к ЗУ лучше всего подходит циклическое распределение (Round-Robin Schedule). Для обеспечения требуемой скорости арбитрации, работа блока может быть конвейеризирована и осуществляться за несколько тактов. При этом, для уменьшения временных затрат на доступ к памяти, операции чтения/записи выгоднее проводить в пакетном режиме, когда при получении доступа к памяти один канал последовательно читает/записывает несколько слов. В то же время размер пакета не должен быть слишком большим, чтобы один канал записи или чтения не блокировал работу остальных портов. В данной работе доступ к ЗУ осуществлялся в виде пакетов размером четыре 64-разрядных слова. Рис. 2. Схема контроллера доступа к ЗУ 231 Синхронизация данных между запросами к ЗУ со стороны портов коммутатора и шиной доступа к памяти осуществляется с помощью буферов FIFO. Эти же буферы позволяют осуществлять подкачку данных на чтение и набор данных для пакетной работы. Пакетная запись здесь нужна только со стороны памяти, в то время как коммутатор может писать одиночными словами. Например, после 4х отдельных операций записи коммутатором слова в буфер FIFO, выставляется запрос арбитру на доступ к памяти, и, после получения доступа, эти четыре слова в виде пакета данных попадают в память. Операция пакетного чтения несколько более сложная. При сохранении блока данных, приходящего из среды (например, Ethernet), запись производится по последовательным адресам в ЗУ. Зная такое расположение данных, для уменьшения времени чтения буферу FIFO можно задать начальный адрес пакета, после чего буфер читает пакеты данных, начиная с этого адреса, до заполнения. По мере того, как коммутатор считывает данные из буфера FIFO, последний может читать из ЗУ следующие данные, таким образом со стороны коммутатора задержка при последующих чтениях отсутствует. Буферы FIFO строятся на основе двухпортовых блоков памяти RAM; один порт используется для записи данных в блок памяти буфера, второй – для чтения этих данных [4, 5]. Порты записи и чтения внутреннего блока памяти буфера принадлежат разным доменам синхросигналов. Буфер не имеет внешних адресных линий, а для доступа к данным внутренней памяти RAM используются указатели записи и чтения, последовательно перемещающиеся при операциях с буфером. Для предотвращения перезаписи непрочитанных данных буфер FIFO имеет флаг заполнения, а для блокировки повторного чтения – флаг отсутствия данных в буфере. Эти флаги вырабатываются в результате сравнения указателей записи и чтения. Поскольку указатели принадлежат разным доменам синхросигналов, для их сравнения требуется предварительно их синхронизовать. Для этого используется стандартная синхронизация с помощью двух триггеров. Для уменьшения ошибки синхронизации указателей, последние передаются в виде кода Грэя. Увеличение указателя, представленного в виде кода Грэя, на единицу приводит к изменению лишь одного бита в указателе, что позволяет избежать менее надежной синхронизации нескольких одновременно изменяющихся бит указателя, представленного в обычном двоичном коде (например, при переключении в двоичной форме 7 8 происходит изменение нескольких бит 0111 1000). Недостатком использования кода Грэя является то, что для его наиболее эффективного использования (исключения нескольких одновременно переключающихся бит) последовательность счета оказывается кратной 2n. На рисунке 3 изображена упрощенная архитектура буфера FIFO, используемого для записи данных в ЗУ. Данные, предназначающиеся на запись, попадают сначала во внутренний блок памяти RAM буфера. Глубина буфера – 8 слов (ширина указателя – 3 бита для доступа в блок памяти буфера, для генерации флагов заполнения и отсутствия данных фактически используется 4 бита указателя). Коммутатор получает подтверждение записи в ЗУ при неактивном флаге заполнения буфера. После записи четырех слов в буфер, последний снимает флаг отсутствия данных, то есть посылает запрос в ЗУ на запись. Во время обработки запроса этого буфера и ожидания буфером в очереди доступа к ЗУ коммутатор продолжает заполнять внутренний блок памяти буфера. При данном количестве каналов обращения к ЗУ (портов) и указанных частотах работы коммутатора и ЗУ, глубины буфера в 8 слов оказывается достаточно для обеспечения непрерывного потока данных от коммутатора к ЗУ. Внутренние блоки памяти буферов FIFO могут быть как заказными, так и результатом синтеза HDL-моделей. Адресные линии канала записи могут передаваться через буфер FIFO вместе с данными на запись или генерироваться с внутренней стороны буфера. В первом случае это приводит к использованию больших ресурсов микросхемы. Во втором случае ограничивается произвольный доступ канала записи к ЗУ. Каждый порт коммутатора имеет программируемые границы области хранения данных в статическом ЗУ, в которую (область) он записывает приходящие кадры Ethernet. При гарантированной последовательной записи, вместо синхронизации адресных линий на каждом такте можно передавать лишь границы областей в ЗУ и адрес начала записи кадра при их изменении. В остальное время буфер FIFO самостоятельно вырабатывает последовательные адреса для записи данных в ЗУ. Организация пакетной работы с памятью приводит к усложнению работы буферов FIFO и арбитрации. Так, для чтения необходимо введение дополнительных схем для загрузки нового адреса чтения. Для записи требуется выравнивать входящие данные по ширине пакета (например, добавлением «пустых», не значащих данных в конце записываемого кадра данных), или введение дополнительных сигналов для обозначения конца пакета, чтобы буфер не ждал заполнения пакета и мог записать последние не выровненные данные в память. Для сетевых технологий, требующих высокой скорости обращения к ЗУ, на рынке представлены компоненты памяти ZBT® / NoBL™ SRAM (Zero Bus Turnaround – нулевой цикл переключения шины, No Bus Latency – отсутствующая задержка шины). Такая память обеспечивает максимальную пропускную способность шины за счет устранения цикла переключения между операциями записи и чтения (Рис. 4). Устройства памяти ZBT® SRAM работают как по потоковой, так и по конвейерной технологии. Конвейерные устройства работают на более высоких частотах, а потоковые имеют меньшую задержку данных. 232 Большинство производителей выпускают память SRAM с увеличенной шиной данных, позволяющей записывать и считывать дополнительные биты побайтовой четности (18/36 разрядная шина данных). При установке двух микросхем памяти с 36 разрядной шиной данных параллельно, доступные 8 дополнительных бит дают возможность использовать избыточные коды, обнаруживающие и исправляющие ошибки. Так, например, код Хэмминга позволяет исправлять однобитовые ошибки на шине данных и обнаруживать ошибки в двух битах. Для 32 разрядов данных код Хэмминга использует 7 дополнительных бит, для 64 разрядов – 8 бит. Кодирование/ исправление ошибок перед непосредственным доступом к памяти позволяет избежать увеличения ширины буферов синхронизации. Конвейерная работа блока арбитрации запросов к памяти позволяет также конвейеризировать относительно медленный блок кодирования/декодирования Хэмминга, требующий операции исключающего ИЛИ над 64 разрядами шины данных. Таким образом, достигается прозрачное для коммутатора исправление ошибок. Предложенная архитектура обладает следующими свойствами: Две микросхемы ЗУ, установленные параллельно, для обеспечения необходимой пропускной способности. Синхронизация данных разных доменов синхросигналов с помощью буферов FIFO. Пакетная обработка для уменьшения времени доступа / арбитрации. Подкачка данных на чтение – возможна при последовательной адресации сохраняемых данных. Дополнительные сигналы начала/конца блока данных и/или загрузки нового адреса чтения. Исправление однобитовых ошибок / обнаружение ошибок в двух битах с помощью кода Хэмминга. Рис. 3. Буфер FIFO, используемый для записи данных в ЗУ Представленное решение использует максимальную производительность компонента памяти SRAM. Для разработки коммутатора с большим количеством портов или поддерживающего более быстрые технологии (быстрее, чем 1 Гбит/с) потребуется дальнейшее увеличение пропускной способности канала обращения к памяти. При этом использованные подходы могут оказаться неподходящими, и наиболее вероятным решением видится использование внешнего ЗУ типа DDR(II) SDRAM, обладающего большей частотой работы (для SRAM пределом является 300 МГц), или использование других технологий производства микросхем, позволяющих расположить общую память на кристалле коммутатора. 233 Рис. 4. Синхронная память с нулевым циклом переключения в сравнение с традиционной памятью В работе предложена архитектура контроллера интерфейса памяти, обеспечивающая максимальное использование памяти SRAM при сохранении относительно невысоких частот работы ядра микросхемы коммутатора. Такая архитектура предоставляет необходимый непрерывный доступ нескольких гигабитных каналов коммутатора к ЗУ и позволяет уменьшить затраты на использование микросхем памяти SRAM и разработку ВЧ интерфейса доступа к ЗУ. ЛИТЕРАТУРА 1. 2. 3. 4. 5. 6. Олифер В. Г., Олифер Н. А. Компьютерные сети. Принципы, технологии, протоколы. – СПб.: Питер, 2001. - 672 с.: ил. Стандарт ISO 35.100 - Open systems interconnection // www.iso.org. Jan M. Rabaey, “Digital Integrated Circuits. A Design Perspective”, Prentice Hall, 1996. Clifford E. Cummings, “Simulation and Synthesis Techniques for Asynchronous FIFO Design,” // Synopsys Users Group Conference, San Jose, CA, 2002. Clifford E. Cummings, “Simulation and Synthesis Techniques for Asynchronous FIFO Design with Asynchronous Pointer Comparisons,” // Synopsys Users Group Conference, San Jose, CA, 2002. Altera Stratix Device Handbook, Altera Corporation. 234