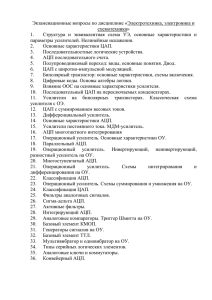

L-791 Руководство пользователя Модуль АЦП общего назначения (многоканальный) Цифровой ввод-вывод, ЦАП (опция)

реклама