1. История развития вычислительной техники

реклама

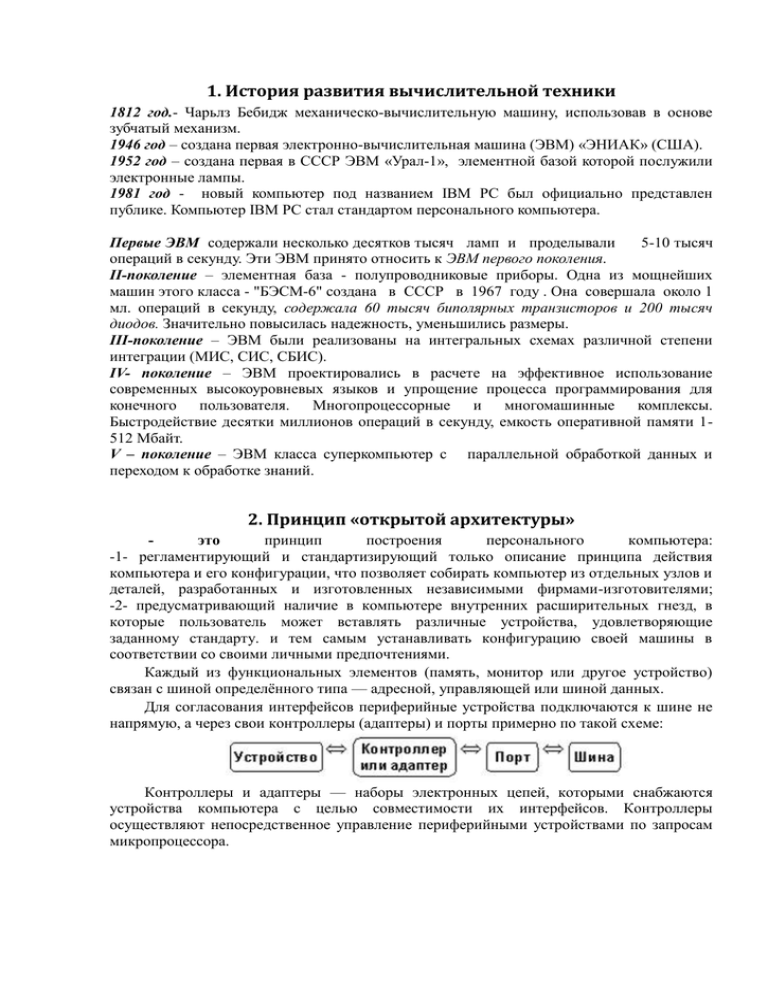

1. История развития вычислительной техники 1812 год.- Чарьлз Бебидж механическо-вычислительную машину, использовав в основе зубчатый механизм. 1946 год – создана первая электронно-вычислительная машина (ЭВМ) «ЭНИАК» (США). 1952 год – создана первая в СССР ЭВМ «Урал-1», элементной базой которой послужили электронные лампы. 1981 год - новый компьютер под названием IBM PC был официально представлен публике. Компьютер IBM PC стал стандартом персонального компьютера. Первые ЭВМ содержали несколько десятков тысяч ламп и проделывали 5-10 тысяч операций в секунду. Эти ЭВМ принято относить к ЭВМ первого поколения. II-поколение – элементная база - полупроводниковые приборы. Одна из мощнейших машин этого класса - "БЭСМ-6" создана в СССР в 1967 году . Она совершала около 1 мл. операций в секунду, содержала 60 тысяч биполярных транзисторов и 200 тысяч диодов. Значительно повысилась надежность, уменьшились размеры. III-поколение – ЭВМ были реализованы на интегральных схемах различной степени интеграции (МИС, СИС, СБИС). IV- поколение – ЭВМ проектировались в расчете на эффективное использование современных высокоуровневых языков и упрощение процесса программирования для конечного пользователя. Многопроцессорные и многомашинные комплексы. Быстродействие десятки миллионов операций в секунду, емкость оперативной памяти 1512 Мбайт. V – поколение – ЭВМ класса суперкомпьютер с параллельной обработкой данных и переходом к обработке знаний. 2. Принцип «открытой архитектуры» это принцип построения персонального компьютера: -1- регламентирующий и стандартизирующий только описание принципа действия компьютера и его конфигурации, что позволяет собирать компьютер из отдельных узлов и деталей, разработанных и изготовленных независимыми фирмами-изготовителями; -2- предусматривающий наличие в компьютере внутренних расширительных гнезд, в которые пользователь может вставлять различные устройства, удовлетворяющие заданному стандарту. и тем самым устанавливать конфигурацию своей машины в соответствии со своими личными предпочтениями. Каждый из функциональных элементов (память, монитор или другое устройство) связан с шиной определённого типа — адресной, управляющей или шиной данных. Для согласования интерфейсов периферийные устройства подключаются к шине не напрямую, а через свои контроллеры (адаптеры) и порты примерно по такой схеме: Контроллеры и адаптеры — наборы электронных цепей, которыми снабжаются устройства компьютера с целью совместимости их интерфейсов. Контроллеры осуществляют непосредственное управление периферийными устройствами по запросам микропроцессора. 3. Процессорное ядро состоит из арифметическо-логического устройства, блока битовых операций, программного контроллера с блоком аппаратных циклов и блока формирования адресов. АЛУ выполняет основные арифметические и логические операции, а также сдвиги. Блок формирования адресов вычисляет эффективный адрес операндов, находящихся в памяти. Программный контроллер выполняет выборку и декодирование команд, обработку прерываний, реализует операции управления программой, в том числе, циклические процедуры. Для обмена данными используются адресные шины и шины данных, которые соединяют модули ядра, память и блоки, обеспечивающие интерфейс с периферийными устройствами. 4. BIOS предназначен для для обеспечения совместной работы системных устройств ПК. BIOS также является "посредником" между операционной системой и аппаратными ресурсами. BIOS производит инициализацию устройств, подключённых к материнской плате, сразу после включения питания компьютера. BIOS проверяет работоспособность устройств, задаёт низкоуровневые параметры их работы (например, частоту шины центрального микропроцессора), и после этого ищет загрузчик операционной системы на доступных носителях информации и передаёт управление операционной системе. Также BIOS содержит минимальный набор сервисных функций (например, для вывода сообщений на экран или приёма символов с клавиатуры). 5. Подсистема синхронизации построена на микросхемах и предназначена Для контроля временных параметров в цифровые схемы встраиваются тактовые генераторы, позволяющие обеспечить синхронизацию. Тактовый генератор — это схема, которая вызывает серию импульсов. Все импульсы одинаковы по длительности. Интервалы между последовательны- ми импульсами также одинаковы. Временной интервал между началом одного импульса и началом следующего называется временем такта. Частота импульсов обычно составляет от 1 до 500 МГц. Частота тактового генератора обычно контролируется кварцевым генератором, позволяющим добиться высокой точности. Связав различные события с разными перепадами (фронтами и спадами), можно достичь требуемой последовательности выполнения действий. Если в пределах одного такта нужно более четырех точек начала отсчета, можно сделать еще несколько ответвлений от задающей линии с различным временем задержки. Синхронная шина содержит линию, которая запускается кварцевым генератором. Сигнал на этой линии представляет собой меандр с частотой обычно от 5 до 100 МГц. Любое действие шины занимает целое число так называемых циклов шины. Асинхронная шина не содержит задающего генератора. Циклы шины могут быть произвольными и не обязательно одинаковыми для всех пар устройств. Синхронная шина MREQ - указывает, что осуществляется доступ к памяти, а не к устройству вводавывода, RD – указывает, что осуществляется чтение, а не запись. Чтобы центральный процессор не ожидал поступления данных, память устанавливает сигнал WAIT. Считав данные, центральный процессор сбрасывает сигналы MREQ и RD. В случае необходимости на следующем фронте может начаться еще один цикл памяти. Эта последовательность может повторяться бесконечно. 6. Шинные формирователи и буферные регистры обеспечивают Подключение устройств производится параллельно, через разветвляющиеся схемы (системные контроллеры, буферные регистры, шинные формирователи), т.е. схемы имеющие 3-и состояния выхода: логический «0», логическая единица «1», состояние высокого сопротивления. Схемы построены так, что при подаче низкого сигнала, выход элементов подключается к магистрали. Все остальное время выход не оказывает влияние на состояние магистрали. Однонаправленный шинный формирователь. Информация передается от А к В, если на ОЕ поступает низкий сигнал Пример однонаправленного шинного формирователя (для парралл.кода) Что бы не произошло наслоение информации, на МД, на один из передатчиков подается сигнал низкого уровня, который разблокирует его выход. Другие передатчики в это время должны быть отключены. Приемники не влияют на состояние магистрали, их может быть подключено несколько. Прием информации осуществляется только по стробу чтения от логического устройства. Двунаправленный формирователь. ОЕ- сигнал разрешения передачи информации А-вход, В- выход (или наоборот) Тсигнал выбора направления передачи информации 7. Временная диаграмма шины ISA . Описание, пояснения, основные сигналы. В фазе данных цикла чтения (рис. 2.6) процессор выставляет отрицательный сигнал чтения данных из устройства ввода/вывода -IOR. В ответ на него устройство-исполнитель должно выдать на шину данных SD свой код данных (читаемые данные). Логика на шине данных положительная. Через установленное время строб обмена -IOR снимается процессором, после чего снимается также и код адреса с шины SA. Цикл заканчивается без учета быстродействия исполнителя. Рис. 2.6. Цикл чтения из УВВ на магистрали ISA. Рис. 2.7. Цикл записи в УВВ на магистрали ISA. Но так происходит только в случае основного, синхронного обмена. Кроме него на магистрали ISA также предусмотрена возможность асинхронного обмена. Для этого применяется сигнал готовности канала (магистрали) I/O CH RDY. Тип выходного каскада для данного сигнала — ОК, для предотвращения конфликтов между устройствамиисполнителями. При синхронном обмене сигнал I/O CH RDY всегда положительный. Но медленное устройство-исполнитель, не успевающее работать в темпе процессора, может этот сигнал снять, то есть сделать нулевым сразу после начала строба обмена. Тогда процессор до того момента, пока сигнал I/O CH RDY не станет снова положительным, приостанавливает завершение цикла, продлевает строб обмена. Конечно, слишком большая длительность этого сигнала рассматривается как аварийная ситуация. Для простоты понимания можно считать, что устройство-исполнитель формирует в данном случае отрицательный сигнал неготовности завершить обмен. На время этого сигнала обмен на магистрали приостанавливается. В режиме программного обмена информацией на шины ISA выполняются четыре типа циклов: Цикл записи в память Цикл чтения из памяти Цикл записи в устройство ввода/вывода Цикл чтения из устройства ввода/вывода 8. Временная диаграмма шины PCI. Описание, пояснения, основные сигналы. Шина PCI в действительности очень проста. Чтобы лучше понять это, рассмотрим временную диаграмму на рис. 3.52. Здесь мы видим транзакцию чтения, за ней следуют пустой цикл и транзакция записи, которая осуществляется тем же задающим устройством. Во время цикла Т1 на спаде синхронизирующего сигнала задающее устройство помещает адрес на линии AD и команду на линии С/ВЕ#. Затем задающее устройство устанавливает сигнал FRAME#, чтобы начать транзакцию. Во время цикла Т2 задающее устройство переключает шину, чтобы подчиненное устройство могло воспользоваться ею во время цикла Т3. Задающее устройство также изменяет сигнал С/ВЕ#, чтобы указать, какие байты в слове ему нужно считать. Во время цикла Т3 подчиненное устройство устанавливает сигнал DEVSEL#. Этот сигнал сообщает задающему устройству, что подчиненное устройство получило адрес и собирается ответить. Подчиненное устройство также помещает данные на линии AD и выдает сигнал TRDY#,- который сообщает задающему устройству о данном действии. Если подчиненное устройство не может ответить быстро, оно не снимает сигнал DEVSEL#, извещающий о присутствии этого устройства, но при этом не устанавливает сигнал TRDY# до тех пор, пока не сможет передать данные. При такой процедуре вводится один или несколько периодов ожидания. В нашем примере (который вполне может произойти в действительности) следующий цикл — пустой. Мы видим, что в цикле Т5 то же самое задающее устройство инициирует процесс записи. Сначала оно, как обычно, помещает адрес и команду на шину. В следующем цикле оно выдает данные. Поскольку линиями AD управляет одно и то же устройство, цикл переключения не требуется. В цикле Т7 память принимает данные. 9. Подсистема прерываний предназначена для обеспечения реакции программы на события, происходящие вне программы. Такие события возникают, как правило, случайно и асинхронно по отношению к программе и требуют прекращения (чаще временного) выполнения текущей программы и переход на выполнение другой программы (подпрограммы), соответствующей возникшему событию. Подсистема прерываний должна обеспечивать выполнение следующих функций: обнаружение изменения состояния внешней среды (запрос на прерывание); идентификация источника прерывания; разрешение конфликтной ситуации в случае одновременного возникновения нескольких запросов (приоритет запросов); определение возможности прерывания текущей программы (приоритет программ); фиксация состояния прерываемой (текущей) программы; переход к программе, соответствующей обслуживаемому прерыванию; возврат к прерванной программе после окончания работы прерывающей программы. 10. Контроллер ПДП предназначен для непосредственного обращения к памяти, минуя процессор. Прямой доступ к памяти (Direct Memory Access - DMA) используется для выполнения операций передачи данных непосредственно между оперативной памятью и устройствами ввода/вывода. При использовании DMA процессор не участвует в операциях ввода/вывода, контроллер прямого доступа сам формирует все сигналы, необходимые для обмена данными с устройством. Скорость такого непосредственного обмена значительно выше, чем при традиционном вводе/выводе с использованием центрального процессора и команд INP, OUT. 11. Структурная схема контроллера 8259. 8259 – контроллер прерываний. 12. структурная схема контроллера ПДП 8237. Структурная схема контроллера ПДП Функциональная схема контроллера 8237А-5 13. ПРОГРАММНАЯ ДИАГНОСТИКА основана НА СТАНДАРТНЫХ ПРИЛОЖЕНИЯХ … И ОБЕСПЕЧИВАЕТ Различают системы тестового и функционального диагностирования. В системах тестового диагностирования воздействия на диагностируемое устройство (ДУ) поступают от средств диагностирования (СД). В системах функционального диагностирования воздействия, поступающие на ДУ, заданы рабочим алгоритмом функционирования. В средних и больших ЭВМ используются, как правило, встроенные (специализированные) средства диагностирования. В микро-ЭВМ чаще используются встроенные средства подачи тестовых воздействий в внешние универсальные средства (например, сигнгатурные анализаторы) для снятия ответов и анализа результатов. Процесс диагностирования состоит из определенных частей (элементарных проверок), каждая из которых характеризуется подаваемым на устройство тестовым или рабочим воздействием я снимаемым с устройства ответом. Получаемое значение ответа (значения сигналов в контрольных точках) называется результатом злементарной проверки. Объектом элементарной проверки назовем ту часть аппаратуры диагностируемого устройства на проверку которой рассчитано тестовое или рабочее воздействие элементарной проверки. Совокупность элементарных проверок, их последовательность и правила обработки результатов определяют алгоритм диагностирования. Средства диагностирования позволяют ЭВМ самостоятельно локализовать неисправность при условии исправности диагностического ядра, т. е. той части аппаратуры, которая должна быть заведомо работоспособной до начала процесса диагностирования. При диагностировании ЭВМ наиболее широкое распространение получил принцип раскрутки, или принцип расширяющихся областей, заключающийся в том, что на каждом wane диагностирования ядро и аппаратура уже проверенных исправных областей устройства представляют собой средства тестового диагностирования, а аппаратура очередной проверяемой области является объектом диагностирования. 14. КЛАССИФИКАЦИЯ ОЗУ, ХАРАКТЕРИСТИКИ, СТРУКТУРНАЯ СХЕМА ДИНАМИЧЕСКОГО ОЗУ Часто для оперативной памяти используют обозначение RAM (Random Access Memory), то есть память с произвольным доступом. Это означает, что обращение к данным, хранящимся в оперативной памяти, не зависит от порядка их расположения в памяти. Полупроводниковая оперативная память в настоящее время делится на статическое ОЗУ (SRAM) и динамическое ОЗУ (DRAM). Динамическая оперативная память ( Dynamic RAM – DRAM) Используется в большинстве систем оперативной памяти персональных компьютеров. Основное преимущество - ячейки упакованы очень плотно. Ячейки памяти в микросхеме DRAM – это крошечные конденсаторы, которые удерживают заряды. Память должна постоянно регенерироваться, так как в противном случае электрические заряды в конденсаторах памяти будут “стекать”, и данные будут потеряны. Регенерация в микросхеме происходит одновременно по всей строке матрицы при обращении к любой из ее ячеек. Максимальный период обращения к каждой строке TRF (refresh time) для гарантированного сохранения информации у современной памяти лежит в пределах 8-64 мс. Каждая ячейка способна хранить только один бит. Если конденсатор ячейки заряжен, то это означает, что бит включен, если разряжен – выключен. Время доступа к данным ~ 30нс. Статическое ОЗУ (SRAM) Быстрее DRAM, но занимает больше места. Используется в для кеш-памяти процессоров. Время доступа к данным ~ 5-10нс Типичная ячейка статической двоичной памяти (двоичный триггер) на КМОП-технологии состоит из двух перекрёстно (кольцом) включённых инверторов и ключевых транзисторов для обеспечения доступа к ячейке. Часто для увеличения плотности упаковки элементов на кристалле в качестве нагрузки применяют поликремниевые резисторы. Недостатком такого решения является рост статического энергопотребления.Линия WL (Word Line) управляет двумя транзисторами доступа. Линии BL и BL (Bit Line) — битовые линии, используются и для записи данных и для чтения данных. 15. Контроллер последовательных портов. Интерфейс RS232. В последовательном интерфейсе для передачи данных в одном направлении используется одна сигнальная линия, по которой информационные биты передаются друг за другом — последовательно. Английские названия последовательных интерфейса и порта — Serial Interface и Serial Port, иногда их неправильно переводят как «серийные». Последовательная передача позволяет сократить количество сигнальных линий и добиться улучшения связи на больших расстояниях. Стандарт RS-232C описывает несимметричные передатчики и приемники: сигнал передается относительно общего провода — схемной «земли». Интерфейс не обеспечивает гальванической развязки устройств. Логической единице (состояние MARK) на входе данных (сигнал RxD) соответствует диапазон напряжения от -12 до -3 В; логическому нулю — от +3 до + 12 В (состояние SPACE). Для входов управляющих сигналов состоянию ON («включено») соответствует диапазон от +3 до +12 В, состоянию OFF («выключено») — от -12 до -3 В. Диапазон от -3 до +3 В — зона нечувствительности, обусловливающая гистерезис приемника: состояние линии считается измененным только после пересечения порога. Уровни сигналов на выходах передатчиков должны быть в диапазонах от -12 до -5 В и от +5 до +12 В. Разность потенциалов между схемными «землями» (SG) соединяемых устройств должна быть менее 2 В, при более высокой разности потенциалов возможно неверное восприятие сигналов. 16. Контроллер параллельных портов. Интерфейс Сentronics(LPT). Порт параллельного интерфейса был введен в PC для подключения принтера. Отсюда и пошло его название — LPT (Line Printer Terminal — порт построчного принтера). Традиционный, он же стандартный, LPT-nopm (называемый еще SPP-портом) ориентирован на вывод данных, хотя с некоторыми ограничениями позволяет и вводить данные. Существуют различные модификации LPT- порта — двунаправленный, ЕРР, ЕСР и др., расширяющие его функциональные возможности, повышающие производительность и снижающие нагрузку на процессор. Поначалу они являлись фирменными решениями отдельных производителей, позднее был принят стандарт IEEE 1284. С программной стороны LPT-порт представляет собой набор регистров, расположенных в адресном пространстве ввода-вывода. Регистры порта адресуются относительно базового адреса порта, стандартными значениями которого являются 3BCh, 378h и 278h. Порт может использовать линию запроса аппаратного прерывания, обычно IRQ7 или IRQ5. В расширенных режимах может использоваться и канал DMA. В режиме ЕРР в порт введены новые регистры, обращение к которым обеспечивает 4 типа циклов обмена: ♦ запись данных и чтение данных при обращениях к регистру EPP_Data инструкциями OUT и JW (соответственно); ♦ запись адреса и чтение адреса при аналогичных обращениях к регистру ЕРР_ Address. 17. Интерфейс USB. Структура. Архитектура шины USB подразумевает подключение одного или нескольких USB-устройств к компьютеру. Компьютер называется хостом(главное управляющее устройство). Для соединения компьютера и устройства используються хабы. Компьютер имеет встроенный хаб, называемые корневым хабом(рис. 1.3). Функция – устройство или его часть. Шина USB сотоит из: VBus – питание; +D – данные «плюс»; -D – данные «минус»; GND – земля. В устройстве к линии +D или –D (в зависимости от скорости работы) подключен подтягивающий резистор. При подключении устр-ва к шине резистор подтягивает на ней напряжение (3.3В). Хост понимает, что подключилось новое устр-во , обращается к нему по адресу 0 и дает ему идентификатор (от 1 до 127). Общение хоста с устр-ми осуществляется путем передачи кадров(фреймов) на шину, при этом инициатор передачи данных – всегда хост(типо главный, держит шину) . Структура кадров на рис.3.3 SOF – Start Of Frame; EOF – End Of Frame; PID – Packet ID; CRC – Cyclic Redundancy Checksums (циклический избыточный код), используется для обнаружния ошибок на уровне блоков данных. 18. POST-тестирование – назначение, алгоритм, аппаратные средства POST (англ. Power-On Self-Test) — самотестирование после включения. Проверка аппаратного обеспечения компьютера, выполняемая при его включении. Выполняется программами, входящими в BIOS материнской платы. После тестирования и конфигурирования POST инициирует загрузку операционной системы. Алгоритм POST-тестирования: 1. Тестирование регистров процессора. 2. Проверка контрольной суммы ROM BIOS. 3. Проверка и инициализация таймера 8253/8254, портов 8255. 4. Проверка и инициализация контроллеров DMA 8237. 5. Проверка регенерации памяти. 6. Тестирование 64 Кбайт нижней памяти. 7. Загрузка векторов прерывания и стека в нижнюю область памяти. 8. Инициализация видеоконтроллера 9. Тестирование полного объема ОЗУ. 10. Тестирование клавиатуры. 11. Тестирование CMOS-памяти и часов. 12. Инициализация СОМ- и LPT-портов. 13. Инициализация и тест контроллера НГМД. 14. Инициализация и тест контроллера НЖМД. 15. Сканирование области дополнительной памяти ROM BIOS. 16. Вызов Bootstrap (Int 19h) — загрузка операционной системы, при невозможности — попытка запуска ROM Basic (Int 18h), при неудаче — останов процессора с сообщением System Halted (система остановлена). При прохождении каждой секции POST записывает ее код (номер) в диагностический регистр. Этот регистр физически располагается на специальной диагностической плате POST Card (это не почтовая карточка), устанавливаемой в слот шины расширения. Плата содержит 8-битный регистр со световой (двоичной или шестнадцатеричной) индикацией состояния битов. В пространстве ввода-вывода регистр занимает один адрес, зависящий от архитектуры PC (: ISA, EISA - 80h). По индикаторам платы можно определить, на какой секции остановился тест POST, и выяснить причину неисправности. Однако для такой диагностики необходимы, во-первых, сама плата-индикатор и, во-вторых, «словарь» неисправностей — таблица, специфическая для версии BIOS и системной платы.