Структура измерительной части основного нейрона

реклама

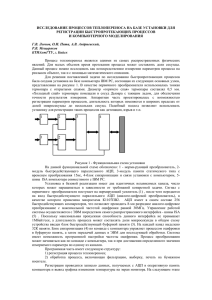

УДК 004.3 А.Н. Корнилков1, А.И. Посягин1 1 Пермский национальный исследовательский политехнический университет, Пермь, Россия Структура измерительной части основного нейрона самомаршрутизирующегося аналого-цифрового преобразователя Аннотация: Рассматривается структура самомаршрутизирующегося аналого-цифрового преобразователя на основе нейронной сети. Приводится структура основного нейрона, входящего в эту структуру. Ключевые слова: аналого-цифровой преобразователь, нейронная сеть, отказоустойчивость. В настоящее время практически во все сферы человеческой жизни проникают автоматизированные системы управления. Основа каждой такой системы – микроконтроллер, который и осуществляет принятие решений. Но для того чтобы принять решение в микроконтроллер должна поступить информация о состоянии объекта управления. Эта информация зачастую снимается с помощью аналоговых датчиков, выходом которых является аналоговое напряжение. Микроконтроллер при этом является цифровым устройством и для его работы информация должна быть представлена в виде двоичного кода. Для осуществления перехода от аналоговой информации к цифровой используются аналого-цифровые преобразователи (АЦП). Современные АЦП предлагают огромный выбор различных устройств для различных нужд: от быстродействующих параллельных АЦП до миниатюрных конвеерных АЦП. Каждое из этих устройств обладает определенным набором характеристик, но в рамках современных систем управления и общего направления конструирования на микроминитюаризацию, актуальной является задача создания адаптивного АЦП, который за счет минимального количества аппаратных издержек, позволял бы создавать различные структуры для решения конкретных задач, и при этом мог перестраивать в любой удобный момент. Одним из прогрессивных направлений в разработке подобных АЦП являются АЦП, построенные с использованием нейронных сетей [1]. Нейронные сети — это математические модели, а также их программные или аппаратные реализации, построенные по принципу организации и функционирования биологических нейронных сетей — сетей нервных клеток живого организма. Нейронные сети представляют собой систему соединённых и взаимодействующих между собой универсальных элементов (искусственных нейронов). Каждый элемент этой сети имеет дело только с сигналами, которые он периодически получает, и сигналами, которые он периодически посылает другим элементам. И, тем не менее, будучи соединёнными, в достаточно большую сеть с управляемым взаимодействием, такие относительно простые элементы вместе способны выполнять довольно сложные задачи. Ключевое место в создании и совершенствовании устройств, использующих технологии нейронных сетей занимает моделирование их функционирования при нормальной работе создаваемых устройств и при их нештатном функционировании. В настоящее время ведутся работы по созданию самомаршрутизирующегося аналого-цифрового преобразователя (АЦП) на основе нейронной сети [2], в результате этих исследований получена структурная схема (рис.1), включающая в себя следующие блоки: блок компараторов, блок вычисления необходимой разрядности АЦП и непосредственно саму нейронную сеть. На вход системы поступают аналоговые сигналы (U1…Un). Блок компараторов сравнивает полученные аналоговые сигналы с уравновешивающими напряжениями, вырабатываемыми нейронной сетью для каждого входа. Уравновешивающие напряжения получаются в нейронной сети за счёт суммирования токов, соответствующих каждому разряду, генерирующихся матрицей R-2R, образованной нейронами. На выходе компаратора выставляется логический 0, если уравновешивающее напряжение превысило входное напряжение, и 1, если нет. Одновременно эти же входные сигналы обрабатываются и системой вычисления требуемой разрядности для индивидуального аналого-цифрового преобразователя (ИАЦП). На выходе этого блока формируется параллельный код (ki), который, поступив в нейронную сеть (НС), служит для неё сигналом к формированию ИАЦП и соответствует требуемому количеству разрядов. Рис.1. Структурная схема аналого-цифрового преобразователя на основе нейронной сети. НС выполняет основную функцию аналого-цифрового преобразования методом поразрядного взвешивания, когда сформированный ИАЦП поочерёдно взводит каждый разряд в единицу, начиная со старшего. При этом после выставления разряда в единицу, проверяется выход компаратора: если уравновешивающее напряжение превысило входное, то разряд сбрасывается, в противном случае он остаётся в 1, система переходит к следующему разряду. Кроме того НС обеспечивает адаптивность всего самомаршрутизирующегося АЦП, объединяя необходимое количество разрядов, определяемое числом ki. Рассмотрим подробнее структуру самой нейронной сети (рис.2). Она состоит из 4 слоёв: слой входных нейронов, слой коммутаторов (Км), слой основных нейронов (ОН) и выходной слой. Работа всего АЦП делится на три этапа: формирование индивидуального аналого-цифрового преобразователя, непосредственное измерение и третий этап – «разрушение» ИАЦП. На этапе формирования ИАЦП коммутаторы собирают информацию о количестве свободных ОН, на её основе делается вывод о том, где в сети может быть расположен ИАЦП. Сбор информации о количестве свободных ОН осуществляется благодаря горизонтальным связям между ними. По команде Км происходит формирование ИАЦП и соединение его входов с входными нейронами, а выходов с выходными нейронами соответственно. НС переходит к этапу измерения. Рис.2 Структурная схема нейронной сети в самомаршрутизирующемся АЦП Основой НС является множество ОН, с помощью которых происходит непосредственное измерение сигнала. Каждый ОН представляет собой одноразрядный АЦП дополненный системой управления (СУ) и системой маршрутизации (СМ). Каждый из ОН способен подключаться к коммутаторам, выходному слою нейронов, предыдущему и последующему ОН. При этом, так как каждый из ОН подключен сразу к нескольким соседним нейронам, система маршрутизации, при формировании ИАЦП, может выбирать путь для обрабатываемого сигнала по НС. Такая маршрутизация обеспечивается срабатыванием коммутаторов и обработкой флагов готовности, поступающих от других нейронов. Всё измерение проходит за 2n+1 такт, при этом последний такт необходим из-за задержки в сдвиговом регистре выходного нейрона. В результате измерения НС подаёт на свои выходы значения отсчётов каждого из измеряемых сигналов (N1-Nn). На этапе «разрушения» ИАЦП система управления отключает связи в слое ОН и связи ОН с коммутаторами. Этот этап выполняется с минимальной задержкой. После окончания «разрушения» ИАЦП, все задействованные нейроны возвращаются в исходное состояние и система способна формировать новые ИАЦП через них. Нами разработана структурная схема основного нейрона (рис.3), включающая в себя три основные части: измерительную, ответственную за маршрутизацию и осуществляющую самодиагностику ОН. Рис. 3 Структурная схема основного нейрона СУ осуществляет управление входными и выходными ключами ОН, включая его, таким образом, в состав ИАЦП. ОН, соответствующий старшему разряду, получает сигналы от коммутатора: сигнал компаратора, сигналы с цифровой и аналоговой шин. Если ОН не является старшим, то соответствующие сигналы будут поступать с предыдущего ОН. Выходные ключи замыкаются также в соответствии с управляющими сигналами, либо на следующий ОН, либо, если ОН оказался младшим разрядом сформированного ИАЦП, то на выходные нейроны. Схема тестирования обеспечивает самодиагностику ОН и вырабатывает значение флага готовности, который определяет работу системы маршрутизации. На данный момент разработана и промоделирована измерительная часть ОН, которую можно разделить на схему получения разряда, звено матрицы R-2R, схему добавления разряда в цифровую шину ИАЦП. Сигнал с компаратора поступает на схему получения разряда, где ОН определяет значение соответствующего ему разряда. Этот сигнал также поступает на выходные ключи напрямую, без какой либо задержки, распространяясь по сформированному ИАЦП. Сигнал с аналоговой шины поступает на звено матрицы R-2R, с помощью которой формируется опорное напряжение для последующего нейрона и происходит передача тока. Далее сигнал со звена матрицы R-2R подаётся на выходные ключи, таким образом из этих звеньев в итоге получается полноценная матрица R-2R. По цифровой шине от нейрона к нейрону в сформированном ИАЦП передаётся последовательность битов, соответствующая значению отсчёта измеряемого напряжения. При этом каждый ОН в ИАЦП добавляет в эту последовательность выработанное им значение разряда, соответствующего положению этого ОН в ИАЦП, таким образом, что в итоге цифровая шина представляет собой сдвиговый регистр, который заканчивается в выходном нейроне. Поступление сигнала метки на выходной нейрон свидетельствует о том, что преобразование завершено и в сдвиговом регистре выходного нейрона находится значение отсчёта старшим разрядом «вперёд». На данный момент в среде Multisim выполнена разработка действующей модели измерительной части основного нейрона. При этом между собой нейроны соединены напрямую. В дальнейшем планируется уделить внимание вопросам самомаршрутизации, добавлению входных и выходных ключей и реализации системы управления. Кроме того, необходимо разрабатывать СУ ОН с учётом ее взаимодействия с СУ Км Библиографический список 1. Цифровые адаптивные информационно-измерительные системы / Авдеев Б. Я., Белоусов В. В., Брусаков И. Ю. и др. // СПб.: Энергоатомиздат, 1997. 2. Посягин А.И., Южаков А.А. Разработка аналого-цифрового преобразователя на основе нейронной сети // Электротехника. 2013. №11. С.10-13. Об авторах Антон Николаевич Корнилков (Пермь) – студент третьего курса группы АТ-11, ЭТФ, ПНИПУ (e-mail: [email protected]) Антон Игоревич Посягин (Пермь) – ассистент кафедры АТ, ЭТФ, ПНИПУ (614081 г.Пермь, ул. Плеханова 71-79, e-mail: [email protected])