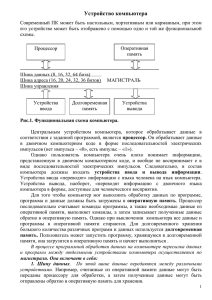

1 Основы микропроцессорной техники 1. Философия

реклама