oevm_examx

advertisement

1Принципы программного управления.

Обобщенная структура ЭВМ с

архитектурой фон-Неймана.

Принцип программного управления (ППУ).

В основу функционирования всех систем положен

ППУ. Он опирается на несколько положений. В

основе ППУ лежит представление алгоритма в

форме операторной схемы, которая задает правила

вычислений, как последовательность операторов

двух типов:

1) операторов обеспечивающих преобразование

либо перемещение информации;

2) операторов анализирующих информацию с

целью определения порядка выполнения операций.

Применительно к ВМ получил способ реализации

ППУ Фон Нейман в 1945 г.

Фон-неймановские принципы:

1)Инфомация кодируется в двоичной форме и

разделяется на единицы, а длинные коды надо

формировать в слова. (группы)

2)Разнотипные слова информации различаются по

способу использования, а не внешним видом.

3) Набор операций также кодируется 2-мя кодами

и эти коды кодируются машинными командами.

4)Алгоритм представляется в форме

последовательности управляющих слов, которые

определяют наименование операции и слова

информации, участвующие в операции. С точки

зрения аппаратуры управляющее слово называется

машинной командой. Алгоритм представленный в

терминах машинных команд называется

программой.

5)Отсутствуют внешние различия между

командами и данными.

6) Все 2-ые коды и команды размещаются в одной

памяти. (признак фон-Неймоновской структуры) и

идентифицируются номерами ячеек памяти (или

адресами).

7)Память является линейной, она одномерна.

Имеет вид вектора слов с последовательными

адресами (0,1,2,3,...). Теоретически границ нет.

8)Память может выполнять 3 действия :

1)Хранить инфу

2)Обеспечить доступ к ячейке при

подаче на вход соотв номера ячейки или

адреса.

3) При обращении к ячеек в 2 операции

a) Чтение ячейки с сохранением

содержимого

b) Замена содержимого внешним

кодом (запись)

4) В процессе решения любой задачи

запись в виде алгоритма, записанного в

виде терминов машинных команд –

называется машинной программой.

9)Выполнение вычислений предписанных

алгоритмом сводится к последовательному

выполнению команд в порядке, однозначно

определяемом программой.

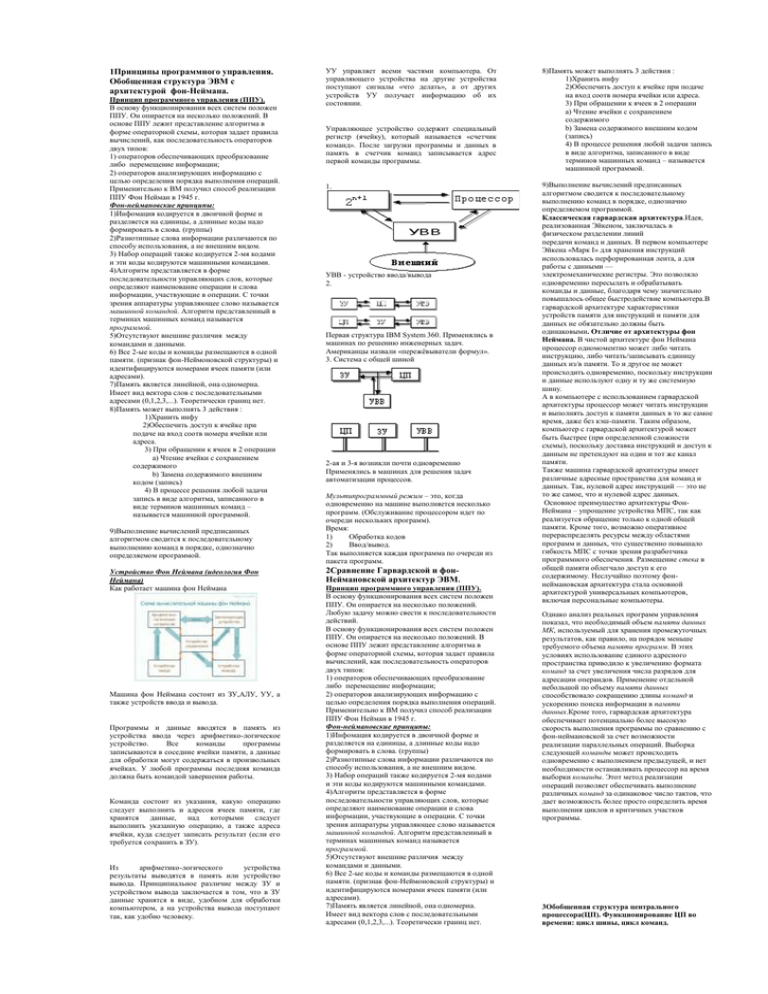

Устройство Фон Неймана (идеология Фон

Неймана)

Как работает машина фон Неймана

Машина фон Неймана состоит из ЗУ,АЛУ, УУ, а

также устройств ввода и вывода.

Программы и данные вводятся в память из

устройства ввода через арифметико-логическое

устройство.

Все

команды

программы

записываются в соседние ячейки памяти, а данные

для обработки могут содержаться в произвольных

ячейках. У любой программы последняя команда

должна быть командой завершения работы.

Команда состоит из указания, какую операцию

следует выполнить и адресов ячеек памяти, где

хранятся данные, над которыми следует

выполнить указанную операцию, а также адреса

ячейки, куда следует записать результат (если его

требуется сохранить в ЗУ).

Из

арифметико-логического

устройства

результаты выводятся в память или устройство

вывода. Принципиальное различие между ЗУ и

устройством вывода заключается в том, что в ЗУ

данные хранятся в виде, удобном для обработки

компьютером, а на устройства вывода поступают

так, как удобно человеку.

УУ управляет всеми частями компьютера. От

управляющего устройства на другие устройства

поступают сигналы «что делать», а от других

устройств УУ получает информацию об их

состоянии.

Управляющее устройство содержит специальный

регистр (ячейку), который называется «счетчик

команд». После загрузки программы и данных в

память в счетчик команд записывается адрес

первой команды программы.

1.

УВВ - устройство ввода/вывода

2.

Первая структура IBM System 360. Применялись в

машинах по решению инженерных задач.

Американцы назвали «пережёвыватели формул».

3. Система с общей шиной

2-ая и 3-я возникли почти одновременно

Применялись в машинах для решения задач

автоматизации процессов.

Мультипрограммный режим – это, когда

одновременно на машине выполняется несколько

программ. (Обслуживание процессором идет по

очереди нескольких программ).

Время:

1)

Обработка кодов

2)

Ввод/вывод.

Так выполняется каждая программа по очереди из

пакета программ.

2Сравнение Гарвардской и фонНеймановской архитектур ЭВМ .

Принцип программного управления (ППУ).

В основу функционирования всех систем положен

ППУ. Он опирается на несколько положений.

Любую задачу можно свести к последовательности

действий.

В основу функционирования всех систем положен

ППУ. Он опирается на несколько положений. В

основе ППУ лежит представление алгоритма в

форме операторной схемы, которая задает правила

вычислений, как последовательность операторов

двух типов:

1) операторов обеспечивающих преобразование

либо перемещение информации;

2) операторов анализирующих информацию с

целью определения порядка выполнения операций.

Применительно к ВМ получил способ реализации

ППУ Фон Нейман в 1945 г.

Фон-неймановские принципы:

1)Инфомация кодируется в двоичной форме и

разделяется на единицы, а длинные коды надо

формировать в слова. (группы)

2)Разнотипные слова информации различаются по

способу использования, а не внешним видом.

3) Набор операций также кодируется 2-мя кодами

и эти коды кодируются машинными командами.

4)Алгоритм представляется в форме

последовательности управляющих слов, которые

определяют наименование операции и слова

информации, участвующие в операции. С точки

зрения аппаратуры управляющее слово называется

машинной командой. Алгоритм представленный в

терминах машинных команд называется

программой.

5)Отсутствуют внешние различия между

командами и данными.

6) Все 2-ые коды и команды размещаются в одной

памяти. (признак фон-Неймоновской структуры) и

идентифицируются номерами ячеек памяти (или

адресами).

7)Память является линейной, она одномерна.

Имеет вид вектора слов с последовательными

адресами (0,1,2,3,...). Теоретически границ нет.

8)Память может выполнять 3 действия :

1)Хранить инфу

2)Обеспечить доступ к ячейке при подаче

на вход соотв номера ячейки или адреса.

3) При обращении к ячеек в 2 операции

a) Чтение ячейки с сохранением

содержимого

b) Замена содержимого внешним кодом

(запись)

4) В процессе решения любой задачи запись

в виде алгоритма, записанного в виде

терминов машинных команд – называется

машинной программой.

9)Выполнение вычислений предписанных

алгоритмом сводится к последовательному

выполнению команд в порядке, однозначно

определяемом программой.

Классическая гарвардская архитектура.Идея,

реализованная Эйкеном, заключалась в

физическом разделении линий

передачи команд и данных. В первом компьютере

Эйкена «Марк I» для хранения инструкций

использовалась перфорированная лента, а для

работы с данными —

электромеханические регистры. Это позволяло

одновременно пересылать и обрабатывать

команды и данные, благодаря чему значительно

повышалось общее быстродействие компьютера.В

гарвардской архитектуре характеристики

устройств памяти для инструкций и памяти для

данных не обязательно должны быть

одинаковыми. Отличие от архитектуры фон

Неймана. В чистой архитектуре фон Неймана

процессор одномоментно может либо читать

инструкцию, либо читать/записывать единицу

данных из/в памяти. То и другое не может

происходить одновременно, поскольку инструкции

и данные используют одну и ту же системную

шину.

А в компьютере с использованием гарвардской

архитектуры процессор может читать инструкции

и выполнять доступ к памяти данных в то же самое

время, даже без кэш-памяти. Таким образом,

компьютер с гарвардской архитектурой может

быть быстрее (при определенной сложности

схемы), поскольку доставка инструкций и доступ к

данным не претендуют на один и тот же канал

памяти.

Также машина гарвардской архитектуры имеет

различные адресные пространства для команд и

данных. Так, нулевой адрес инструкций — это не

то же самое, что и нулевой адрес данных.

Основное преимущество архитектуры ФонНеймана – упрощение устройства МПС, так как

реализуется обращение только к одной общей

памяти. Кроме того, возможно оперативное

перераспределять ресурсы между областями

программ и данных, что существенно повышало

гибкость МПС с точки зрения разработчика

программного обеспечения. Размещение стека в

общей памяти облегчало доступ к его

содержимому. Неслучайно поэтому фоннеймановская архитектура стала основной

архитектурой универсальных компьютеров,

включая персональные компьютеры.

Однако анализ реальных программ управления

показал, что необходимый объем памяти данных

МК, используемый для хранения промежуточных

результатов, как правило, на порядок меньше

требуемого объема памяти программ. В этих

условиях использование единого адресного

пространства приводило к увеличению формата

команд за счет увеличения числа разрядов для

адресации операндов. Применение отдельной

небольшой по объему памяти данных

способствовало сокращению длины команд и

ускорению поиска информации в памяти

данных.Кроме того, гарвардская архитектура

обеспечивает потенциально более высокую

скорость выполнения программы по сравнению с

фон-неймановской за счет возможности

реализации параллельных операций. Выборка

следующей команды может происходить

одновременно с выполнением предыдущей, и нет

необходимости останавливать процессор на время

выборки команды. Этот метод реализации

операций позволяет обеспечивать выполнение

различных команд за одинаковое число тактов, что

дает возможность более просто определить время

выполнения циклов и критичных участков

программы.

3Обобщенная структура центрального

процессора(ЦП). Функционирование ЦП во

времени: цикл шины, цикл команд.

1) Обобщенный алгоритм функционирования

процессора (машины Фон Неймана).

Процессор.

Структура

центрального

процессора

Последовательность действий, которые выполняет

ЦП:

1)

Выставляет адрес команды

2)

Читает команду из памяти

3)

Формирует адрес следующей команды

4)

Расшифровывает операцию

5)

Читает операнд (если нужно)

6)

Выполняет

действия,

предписанные

командой (если нужно)

7)

Записывает результаты в память (если

нужно)

Процессор. Обобщенная структура процессора как

операционного автомата

ЦП – это та часть, которая выполняет основную

программу машины.

Во внешний мир выходит 3 группами сигналов:

шина адреса, данных, управления.

С точки

зрения

цифровых автоматов

процессор состоит из

двух

частей:

управляющий

автомат

и

операционный автомат.

В операционном автомате набор регистров и

комбинационная схема. В управляющем автомате

генератор пространственно-временных кодов.

Внутри ЦП:

блок обработки данных (кодов).

набор регистров, чтобы можно было

хранить кодовую операцию на момент

выполнения каких либо действий (код на

время такта - обязательно).

устройство управления.

Эта

структура

ЦП

является

структурой

операционной системы.

Блок обработки кодов

должен уметь принять команду из внешнего мира

и хранить ее в течение времени выполнения

команды; имеется регистр команд и устройство

дешифрации.

В АЛУ должно быть как минимум две кодовых

группы на вход и одна на выход, т.е. исходные

данные и результат.

В

простейшем

случае

представляет

комбинационную схему: 2 входа для операнда А и

В. Код операции – определяет конкретные

операции кодов, которые поступают.

Разрядность АЛУ и есть разрядность процессора

(т.е. если АЛУ имеет 64 разряда, а обрабатывает

32, то процессор будет 32 разрядный).

Кроме результата данных АЛУ вырабатывает

признаки результата ( от 4 до 6 разрядов) – чтобы

организовать алгоритм выполнения сложных

действий. Признаки нужны для дальнейшего

движения по программе.

Признаки:

1)

Признак знака результата

(1,s<0…0,s>0)

2)

Признак нуля (1,s=0…0,s!=0)

3)

Признак переноса (с), для

обработки кодов большой

длины

4)

Признак

переполнения

разрядной сетки (A). Может

возникнуть в случае когда

данные выходят за знак

5)

Признак паритета (признак

четности) (P) АЛУ считает

четное число или нет “1”

Добавляет число 1 либо до четного, либо до

нечетного. Это для того, чтобы определить

одиночные ошибки, но он не позволяет определить

четное число ошибок.

Для расширения возможностей встраиваются доп

блоки. Для плавающей точки 2 АЛУ, 1 для

мантиссы, другой для порядков т.е это уже на

аппаратном уровне, а не на программном.

Блок регистров Все регистры можно разделить на

2 группы:

1. программно видимые

2. программно невидимые

Программно-видимый регистр – это такой регистр,

содержимое которого мы можем изменить с

помощью программы, он является частью

программной модели машины с которой мы

работаем- это регистры для хранения и явного

преобразования данных, кодов и управления.

Регистры общего назначения – это регистры,

которые в разных ситуациях могут использоваться

по разному. В Intel процессорах РОН являются

функционально закрепленными.

Регистры данных : регистры в которые

записываются опереанды. Аккумулятор, если ЦП

простой то он один, больше для сложны ЦП.

Уменьшает длину команды.

Регистры адреса : связаны с адресом

IP- программный счетчик (указатель команд)

разрядность регистра может быть разной

SP- указатель стека (безадресная память с точки

зрения пользователя, а с аппаратной нет)

Регистр базы –для адресации

Индексные регистры

Регистры

управлениядля

управления

процессором

Пример. Указатель стека – предназначен для

реализации памяти.А=А*В – если преобразование

кодов идет вот так, то резко уменьшается число

обращений во внешний мир. Но ухудшается

длительность программы. Программно-невидимый

программисту недоступен.

Буферная память 1)ассоциативная 2)магазинного

типа (стек)

Многие алгоритмы

опираются на стековую

память.

Общая идея обмана (как бы есть стековая

виртуальная память).

РА-регистр адреса. Имитация стековой памяти.

Устройство управления.

Устройство управления

- это управляющий

автомат.

УУ

вырабатывает

синхроимпульсы

в

нужное

время

в

нужные места.

yi={0,1}; x={0,1}

Задача УУ – выборка управляющих воздействий

на основе алгоритма и сигналов состояния объекта

Yt=yn,yn-1,...,y1,y0

- выходные сигналы

управления

_

X=xn,...,x0

УА – управляющий автомат. Т – тактовые

импульсы.

Управление автоматом можно реализовать

помощью автомата с жесткой логикой.

Управляющий автомат генерирует сигнал.

с

X – обратная связь, Y – сигнал управления, Т –

тактовые импульсы.

Память выходит во внешний мир группой

сигналов:

1) А – кодовая группа, которая

называет адресом. Разрядность А определяет число

адресуемых

ячеек

в

памяти.

Адресное

пространство в памяти = 2n.

Набор сигналов (проводников) А называют шиной

адреса (ША).

2)Данные – кодовая группа, которая извлекается из

памяти. Может быть шина данных входных и

выходных (DI и DO) сигналов. m – ширина шины

даннх.

В классической модели (Фон Неймана) не может

быть выполнено много действий; их всего 3:

1. Хранение информации

2. Запись информации

3. Выдача информации

Т.е. здесь одновременно записи и чтения не может

быть,

следовательно

шина

может

быть

двунаправленной, но в каждый заданный момент

времени она передает данные лишь в одном

направлении.

Те линии по которым передаются

данные

называются шиной данных(ШД).

3)

Набор сигналов управления, которые

поступают на модуль (С) – их не меньше

чем 2 провода: один провод – чтение и

запись, другой сигнализация или сигнал

чтения и сигнал записи. И еще

дополнительный третий провод сигнал

разрешения работы.

Временная диаграмма: сначала адрес, данные,

сигнал работы.

2 фазы работы ЭВМ (цикла команд).

1)Чтение команды

2)Выполнение команды

Эти фазы замкнуты между собой

Цикл команды – временной отрезок, в течение

которого выполняется цикл алгоритма. Цикл

команды, скорее всего величина переменная.

Можно построить системы с постоянными

циклами команд (управление будет проще, набор

команд будет не любой). Первый адрес (пусковой

адрес) должен быть где-то заложен (запаян на

этапе изготовления), либо задается извне на

внешних выводах процессора. Цикл команды

процессора - время выполнения одной команды.

Совокупность сигналов, которыми процессор

выходит во внешний мир, называется шиной. Цикл

процессорной шины - некоторое законченное

действие по взаимодействию с внешней средой.

Циклов шины может быть много. Цикл шины

(магистрали) – это совокупность служебных

операций передатчика и приемника, необходимых

для реализации конкретной процедуры обмена по

ОМ

между

двумя

устройствами

ЭВМ..Длительность цикла шины (магистрали) –

это интервал времени, необходимый для

реализации конкретной однократной процедуры

обмена по ОМ между двумя устройствами ЭВМ.

Основные циклы : чтение памяти, запись в память.

Возможные циклы: чтение ввода-вывода, запись в

ввод-вывод и т.д.

4Система команд ЦП: основные типы и

форматы.

Система команд – набор команд, который

процессор умеет выполнять. Считывание команд

должно выполнять ряд условий:

1.

функциональная полнота (система

команд должна позволить

реализовать любой алгоритм)

2.

ввод команд должен быть удобным

(эффективный)

Функциональный набор команд для фон

Неймановской архитектуры:

1.

Изменения ячейки памяти на 1

2.

Пересылка кода из одной ячейки

памяти в другую

3.

Команда ветвления по равенству 0 к

содержимому ячейки памяти

(условный переход)

Все команды можно разделить на 3 группы:

1.Команды преобразования кода.

(лог. и арифм. операции пр-я кодов, реализация

функций (сильно зависит от орентации

процессора))

2.Команды изменения положения (перемещ-я)

информации внутри системы.

(пересылка из одной ЯП в др., команда обмена

данными м\д внутренним регистром и памятью,

пересылка регистр<->регистр, работа с ВУ: с

регистрами I\O.)

3.Команды управления (влияют на работу

процессора, не изменяя и не перемещая данные).

3.1. Арифметика (4 или более команды).

Логические команды. Команды,

связанные с представление чисел.

3.2. Команды перемещения по памяти. Пересылки

между регистрами из памяти в регистр и т.д.

3.3. Команды управления:

команды изменения порядка выборки:

безусловные команды (действие команд не

зависит ни от чего).

условие (действие зависит от условия).

команды изменения режима работы процессора

(HALT,STOP-ожидает прерывание ,WAIT). Режим

пользователя (вып. привилегиров. команд, режим

системы (вып. все команды).

команды перехода

команды перехода с возвратом

(программные прерывания и команды обращения к

процедурам (CALL)).

команды цикла

Программа представленная в виде кодов

называется машинной командой. Формат команды

- структура, привязанная к разрядной сетке.

КОП

Что делать

Адресная часть

Над чем делать

Бывают одноадресные и двухадресные команды.

3-х адресаня : A=B*C

2-х адресная : A=A*B

1-адресная : ФМ=ФМ*A

Способ адресации – способ указания операндов в

команде. Базовыми являются:

Помимо перечисленных имеются и более сложные

способы адресации:

индексная, относительная и др., однако в

простейших МП они не используются .

Адресация может быть абсолютной или

неабсолютной. При абсолютной адресации

обратиться к ячейке памяти или ВУ можно только

по одному-единственному адресу. При

неабсолютной адресации для ячейки памяти или

ВУ можно выделить некоторую зону адресов.

Иными словами, абсолютная адресация требует

полного декодирования адреса, а неабсолютная —

частичного, что упрощает схемы декодирования

Относительная (базовая) адресация

При этом способе адресации исполнительный

адрес определяется как сумма адресного кода

команды и базового адреса, как правило

хранящегося в специальном регистре — регистре

базы.

Относительная адресация позволяет при меньшей

длине адресного кода команды обеспечить доступ

к любой ячейке памяти. Смещение определяет

положение операнда относительно начала массива,

задаваемого базовым адресом.

•скрытая (неявная) (когда вообще нет адресного

поля, есть только что делать? Но это обман)

•Думаю подробно про способы адресации можно

прочитать в любом учебнике по ассемблеру. В

двух словах (из Зубкова):

1. Регистровая адресация - операнды

располагаются в любых регистрах общего

назначения или сегментных регистрах

mov bx, ax

mov es, ax

2. Непосредственная адресация в команде

содержится сам операнд.

mov ax, 2

add ax, 2

3. При прямой адресации код адреса содержится в

команде, подлежащей выполнению. Прямая

адресация удобна, но удлиняет команды В случае

прямой регистровой адресации, адрес является малоразрядным, поскольку число таких регистров

мало. В этом случае прямая адресация проявляет

все свои достоинства. Прямая адресация - если

известен адрес операнда располагающегося в

памяти

mov ax,es:0001

mov ax, es:word_var

В последнем случае ассемблер сам заменит слово

word_var на соответствующий адрес

4. При косвенной адресации в команде явно или

неявно указывается регистр процессора,

содержащий адрес операнда. Команда сохраняет

компактность, мо для ее выполнения требуется

предварительная настройка — загрузка адреса в

регистр (регистр косвенного адреса). Косвенная

адресация удобна при обработке списков, когда

настройка производится однократно, а очередной

адрес получается модификацией предыдущег.

Косвенная адресация - адрес операнда в памяти

можно не указывать непосредственно, а хранить в

любом регистре

mov ax, [bx]

5. Адресация по базе со сдвигом - комбинация

двух предыдущих методов адресации

mov ax, [bx+2]

mov ax, [bp]+2

6. Косвенная адресация с масштабированием

mov ax,[esi*2]+2 - этот метод адресации полностью

идентичен предыдущему, за исключением того,

что с его помощью можно прочитать элемент

массива слов, двойных слов или учетверенных

слов, просто поместив номер элемента в регистр

множитель, может быть равен 1, 2, 4 или 8 соответствует размеру элемента массива — байту,

слову, двойному слову, учетверенному слову

соответственно

7. Адресация по базе с индексированием - в этом

методе адресации смещение операнда в памяти

вычисляется как сумма чисел, содержащихся в

двух регистрах, и смещения, если оно указано

Все следующие команды — это разные формы

записи одного и того же действия:

mov ax,[bx+si+2]

mov ax,[bx][si]+2

mov ax,[bx+2][si]

mov ax,[bx][si+2]

mov ax,2[bx][si]

8. Адресация по базе с индексированием и

масштабированием - это самая полная возможная

схема адресации, в которую входят все случаи,

рассмотренные ранее, как частные

mov eax, ds:[eax+ebx*2+2]

5RISC и CISC процессоры с точки зрения

системы команд: общие идеи и сравнительные

характеристики.

RISC – процессор с сокращенным набором команд

CISC – процессор с расширенным набором

команд.

Требования к RISC:

Любая операция, независимо от ее типа

выполняется за 1 такт.

Система команд содержит минимальный

набор наиболее часто используемых

простых команд одинаковой длины.

3.

Операции обработки данных реализуются

только в формате «регистр- регистр».

Пересылка данных между регистрами и

оперативной памятью осуществляется с

помощью специальных команд

загрузки/записи.

4.

Состав система команд должен быть удобен

для написания трансляторов с языков

высокого уровня.

Такие микропроцессоры уникальны по

показателю «число команд в единицу времени».

Достижение максимально возможной

производительности стало целью разработки RISC

процессоров.Практически высокая

производительность достигается использованием

полно разрядной обработки; конфейерной

организуемой арифметики; суперскалярной

архтектурой процессора; уменьшением частоты

обращения к внешней памяти.В настоящее время

полноразрядноым словом как для плавающей так и

для фиксированной запятой при выполнении

арифметических операций считается 64 двоичных

разряда. Конвейерная организация арифметики т.е.

разбиение операций на последовательность

элементарных действий выполняемых в различные

моменты времени позволяет поднять тактовую

частоту и включать в состав команд процессора

сложные команды, такие как операции с

плавающей запятой и др. Использование

арифметических конвейеров привело к изменению

требований к RISC.

Дальнейшее повышение производительности

возможно только на пути распараллеливания

операций. Так появились процессора с так

называемой суперскалярной обработкой. Смысл

суперскалярности закдючается в том, что в

аппаратуру микропроцессора закладываются

средства позволяющие одновременно выполнять

несколько скалярных операций т.е. команд

обработки пары чисел. Такой подход позволяет

увеличить производительность пропорционально

числу одновременно выполняемых операций.

Проблемы заключаются в том как осуществить

поиск и группировку несвязных команд,

параллельно запускаемых на исполнение.В RISC

процессорах пока в основном используется

аппаратный механизм выборки из буфера команд

несвязанных команд и запуск их на параллельное

исполнение. Другой способ реализующий загрузку

суперскалярной архитектуры заключается в

изменении всего процесса компиляции и

исполнения. На этапе трансляции компилятор

группирует несвязные операции в пакеты,

содержимое которых соответствует структуре

процессора, его возможности параллельного

выполнения команд различного типа. В пакете

содержатся команды, которые процессор может

выполнить параллельно. Сформированные пакеты

операций преобразуются компилятором в

командные слова получившие название VLIW –

Very Large Instruction Word – очень широкое

командное слово.По идее такой подход должен

привести к упрощению схем процессора т.к. не

надо искать независимых команд и повышение

производительности.Процессоры, использующие

такой подход получили название процессоров с

VLIW архитектурой.

1.

2.

Существуют два пути решения проблемы

компоновки программ:

Сделать

систему,

которая

сама

распараллеливает (разделяет команды)

между ветвями (процессорами) - это

аппаратный способ. Аппаратура должна

уметь подготовить любую программу путем

предварительного

просмотра

команд

(программы). Лучше иметь компилятор,

который все это делает.

Динамическое использование команд – значит есть

устройство

(буфер),

которое

формирует

араллельно выполняющиеся блоки.

2. Чтобы это выполнял программист программный

путь.

Возложить

функцию

формирования на систему подготовки. (система

подготовки это компилятор и программист).

Технология процессора с длинным машинным

словом.

VLIW (Very Long Instruction Word) – очень

длинное командное слово.

Архитектура процессора с VLIW – проще (все

перекладывается на программиста).

Системы со сцепленными конвейерами.

Блок обработки данных состоит из конвейера.

Получается длинный конвейер.

В этом случае можно начинать обработку во

втором конвейере, не дожидаясь окончания

обработки в первом.

Исторически процессор и память конкурируют по

производительности.

Сейчас резкое отставание процессора и памяти

(внутреннего мира) от внешнего мира.

Время

прохождения

сигнала

проводника

становится очень мало, возникает расщепление

сигнала (в одном проводнике возникают 2 сигнала)

при выключенном приемнике. Приемник еще не

принял, а передатчик уже перестал передавать.

Идеологический подход к решению проблемы:

У высокочастотных ЦП к 1 ГГц внешняя среда

(память, плата и т.д.) не успевает за ЦП.

Нужно уменьшить число обращений к внешнему

миру, тогда

внутренние скорости будут

определять работу.

Пути решения:

Как сделать, чтобы внешняя среда успевала за ЦП,

1.Надо из внешней среды брать больше чем тебе

надо, т.е. как можно больше за один раз, т.е.

увеличить разрядность внешних шин ЦП.

Допустим внутри у ЦП 32 разряда, а внешне шину

делаем 6 разряда (пример Pentium). За раз

обрабатывается 2 по 32 разряда

2.Установка внутренней памяти на ЦП (она может

быть программно доступна – это набор регистров).

Нужно иметь буферную память и отдельную

обработку от загрузки, т.е. буфер ждет, а затем

передает.

3.Установка КЭШ памяти – это буферная память с

автоматическим накоплением наиболее часто

используемой

информации.

КЭШ

–

она

программно не доступна.

Повышение внутренних тактовых частот

неминуемо порождает проблему взаимодействия с

внешней по отношению к процессору памятью.

Для того чтобы все рассмотренные ранее в

процессоре работали, надо постоянно иметь в

процессоре необходимую информацию – набор

команд и данных. Достигается это введением в

схему средств обеспечивающих безостановочную

работу арифметических устройств:

большого количества оперативных

регистров (>32 (138))

встроенной КЭШ памяти одного или

нескольких уровней

управления внешней КЭШ

механизм предвыборки команд и

прогнозирования ветвлений.

Эти средства позволяют резко сократить число

обращений к внешней памяти, тем самым снижены

общие требования по быстродействиювнешних

схем.

Структура RISC процессора

КЭШ 2-го уровня предназначен для общения с

внешним уровнем.

БОД - блок обработки данных.

-

Основные достоинства RISC- процессоров:

1.

2.

3.

1.

Повышение производительности

обработки программ

вычислительных задач.

Благодаря использованию простых

команд и минимума их форматов

сокращается время разработки RISCпроцессора.

Улучшение технологичности RISCпроцессоров благодаря большей

свободе в размещении их элементов

на кристалле интегральной схемы и

повышение вероятности выхода

годных схем.

Недостатки RISC- процессоров:

1.

2.

Нарушение основных принципов

программирования:

1.

Минимум длины

исполняемого кода

программы.

2.

Снижение

семантического

разрыва между

исходным описание и

машинным кодом.

Сложность построения компилятора,

поскольку программа с языка

3.

высокого уровня должна

транслироваться в микрокод с

оптимизацией использования

регистров.

Высокие требования к

быстродействию памяти

CISC (англ. Complex instruction set computing,

или англ. complex instruction set computer —

компьютер с комплексным набором команд) —

концепция проектирования процессоров, которая

характеризуется следующим набором свойств:

нефиксированное значение длины

команды;

арифметические действия кодируются в

одной команде;

ЗУМК – ЗУ микрокоманды, в ЗУ лежат

микрокоманды. РАМК – регистр адреса

микрокоманды.

ФАдМК – формирование адреса микрокоманды.

С точки зрения формирования адреса все автоматы

делятся на:

1) автоматы построенные на базе счетчика

(автомат с естественной адресацией)

2) автомат на базе регистра (с принудительной

адресацией)- микропрограмма имеет 2 поля: Y –

операционное, А – адресное (адрес след.команды).

небольшое число регистров, каждый из

которых выполняет строго определённую

функцию.

Для CISC-процессоров характерно: сравнительно

небольшое число регистров общего назначения;

большое количество машинных команд, некоторые

из которых нагружены семантически аналогично

операторам высокоуровневых языков

программирования и выполняются за много

тактов; большое количество методов адресации;

большое количество форматов команд различной

разрядности; преобладание двухадресного

формата команд; наличие команд обработки типа

регистр-память

Типичными представителями являются

процессоры на основе команд x86 Наиболее

распространённая архитектура современных

настольных, серверных и мобильных процессоров

построена по архитектуре Intel x86 (или х86-64 в

случае 64-разрядных процессоров). Формально,

все х86-процессоры являлись CISC-процессорами,

однако новые процессоры, начиная с Intel Pentium

Pro, являются CISC-процессорами с RISC-ядром.

Они непосредственно перед исполнением

преобразуют CISC-инструкции процессоров x86 в

более простой набор внутренних инструкций

RISC.В микропроцессор встраивается аппаратный

транслятор, превращающий команды x86 в

команды внутреннего RISC-процессора. При этом

одна команда x86 может порождать несколько

RISC-команд (в случае процессоров типа P6 — до

четырёх RISC-команд в большинстве случаев).

Исполнение команд происходит

на суперскалярном конвейере одновременно по

несколько штук.Это потребовалось для увеличения

скорости обработки CISC-команд, так как

известно, что любой CISC-процессор уступает

RISC-процессорам по количеству выполняемых

операций в секунду. В итоге, такой подход и

позволил поднять производительность CPU.

Недостатки CISC архитектуры

Автомат с мягкой(программируемой) логикой.

Идея построения автомата с микропрограммой:

высокая стоимость аппаратной части;

сложности с распараллеливанием

вычислений.

Методика построения системы команд CISC

противоположна другой методике - RISC.

Различие этих концепций состоит в методах

программирования, а не в реальной архитектуре

процессора. Практически все современные

процессоры эмулируют наборы команд как RISC

так и CISC типа.

6,7,8Микропрограммные автоматы с

принудительной адресацией: общая структура,

реализация механизма ветвлений.

Микрооперация – операция (действие) при

подаче 1 микроимпульса. Объект управления

может допускать одновременное выполнение

нескольких микроопераций. Набор

микроопераций, выполняемых параллельно

называется микрокомандой.

Автоматы с жесткой логикой, т.е. алгоритм

работы задается внутренними связями между

элементами, т.е. если мы хотим изменить

алгоритм, то нужно изменить внутренние связи.

(Положительные свойства: обладает наивысшей

скоростью).

Структура цифрового автомата.

(2+триггера - одиночная скорость для любого

автомата. 2 - так как имеется 2 ступени

(минимум) И или ИЛИ, и наоборот из ИЛИ в И).

Программа она в памяти. Как выбрать нужную

команду. Пришем в команде следующую и нет

безусловных переходов все хорошо. Тот кто пишет

программу знает какой должен быть следующий

адрес. Т.е где регистр там принудительная.

Проблемы возникают с ветвлением.

С точки зрения команд разные адреса Если адрес 1

и 2 ставим.

Ветвление по одной переменной

Если проверяемых значений много, то нужно

отвести поле, в котором будет номер проверяемого

условия (i). i - для номера проверяющего условия.

1-й недостаток – нерациональное использование

памяти. Так как используем дополнительное поле

которое ненужно

2-й недостаток – если результат зависит от

нескольких переменных, то для n переменных

нужно организовать (n-1) холостых циклов.

БФАМК – блок формирования адреса

микрокоманды.

РАМК – регистр адреса микрокоманды

Естественная адресация.

Считаем что идем подрят, то ставим щетчик. Т.е в

команде у нас нет явного указания следующей.

Загружаем в счетчик значение ветвления и

перебираем, хорошо когда 1, но когда много.

X1x2x3 это не есть хорошо. Хотим за раз. Введем

понятие по нескольким переменным.

i – выбирает какую переменную проверять

(x0,…,xn). После ее выбора выритается адрес

ветвления A1;A2.

Решение 2-го недостатка:

Организовать ветвление по нескольким

направлениям, этот способ намного

эффективнее, но возникает проблема с

реализацией. Обычно выбирают 4-5 разрядов

ветвления. x0,x1…x4(x3)

Ветвление по нескольким переменным.

Т.е используем базу. А Адреса А1!=А2!=А3!=А4

различны

А1!=А2!=А3!=А4

Аисп.=f(Aбаза Х1 Х2)

Х1 Х2

А

8 вопрос)Устройство управления – ЦА,

выполняющий посл-ность обрабатывающих кодов

в соотв-и с алгоритмом.

В старых ЦП около 250 разрядов.

Больше за 1 такт Цп может обрабатывать 5

опереций и это не эффективно. Решили записывать

не по месту операции а по номеру.

Идея собрать коды из памяти в соотвецтвии с

алгоритмом она универсальная. Но такой подход

делает УС практически невозможным т.к за ( 1

такт микрокоманды.) Вообщем сделали несколько

таких схем.

Подход хороший но избыточный т.к если 1

операция записанная в поле остальные свободны .

Т.е надо уменьшить. И в одно поле надо записать

кот будут выполнятся одновременно. Записываем

в поля но размер у них разный . При разделения на

группы используется этот подход.

Вместо всех разрядов будем хранить номера.

В каждом поле микрокоманды хранится отдельная

микрооперация. Получается, что могут храниться

одни и те же микрооперации.

В управляющем коде мы храним адреса команд.

Что-то около 200. Если у нас есть 200 команд, то

нам надо 8 разрядов для их однозначного

декодирования.

Для сокращения длины упр. слова надо все

микрооперации разбить на группы по принципу

несовместимости:

1) физически несовместимые, например, операции

над регистрами: нельзя сдвигать регистр

одновременно в две стороны, поэтому все 4

команды будут в одной группе – для однозначной

кодировки. На каждую группу ставим дешифратор,

который и выбирает из группы нужную

микрооперацию. Потребуется столько групп,

сколько получится совместимых операций, тогда в

полях будет разное кол-во операций, которое надо

выровнять.

2) логически несовместимые, т.е. эти команды не

должны выполняться вместе. Например, mov

a,mem и mov b,a несовместимы (нельзя их

выполнять одновременно).

Микрооперация – действие при подаче одного

управляющего сигнала.

В каждой микрокоманде надо писать адрес

следующей.

Микрокоманда - набор нескольких

микроопераций.

Ячейка – это группа несовместных операций.

При оптимизации длины управляющие слова

разделяются на подгруппы несовместных

микропрограмм по времени, затем реализуем эту

схему для каждой группы.

При разбиении микроопераций на группы, нужно,

чтобы они имели одинаковое число разрядов.

9Память ЭВМ: классификация и

основные типы ЗУ.

Основные сведения. Система

параметров. Классификация

Важнейшие параметры ЗУ находятся в

противоречии. Так, например, большая

информационная емкость не сочетается с высоким

быстродействием, а быстродействие в свою

очередь не сочетается с низкой стоимостью.

Поэтому системам памяти свойственна

многоступенчатая иерархическая структура, и в

зависимости от роли того или иного ЗУ его

реализация может быть существенно различной.

Запоминающие устройства (ЗУ) служат для

хранения информации и обмена ею с другими ЦУ.

Системам памяти свойственна многоступенчатая

иерархическая структура, и в зависимости от роли

того или иного ЗУ его реализация может быть

существенно различной.

В наиболее развитой иерархии памяти ЭВМ можно

выделить следующие уровни:

1. регистровые ЗУ, находящиеся в составе

процессора или других устройств (т. е.

внутренние для этих блоков), благодаря

которым уменьшается число обращений к

другим уровням памяти, реализованным вне

процессора и требующим большего времени

для операций обмена информацией;

2. кэш-память, служащая для хранения копий

информации, используемой в текущих

операциях обмена. Высокое быстродействие

кэш-памяти повышает производительность

ЭВМ;

3. основная память (оперативная, постоянная,

полупостоянная), работающая в режиме

непосредственного обмена с процессором и по

возможности согласованная с ним по

быстродействию. Исполняемый в текущий

момент фрагмент программы обязательно

находится в основной памяти;

4. специализированные виды памяти,

характерные для некоторых специфических

архитектур (многопортовые, ассоциативные,

видеопамять и др.);

5. внешняя память, хранящая большие объемы

информации. Эта память обычно реализуется

на основе устройств с подвижным носителем

информации (магнитные и оптические диски,

магнитные ленты и др.). В настоящем пособии

устройства внешней памяти не

рассматриваются.

Важнейшие параметры ЗУ

Информационная емкость — максимально

возможный объем хранимой информации.

Организация ЗУ— произведение числа хранимых

слов на их разрядность. Быстродействие

(производительность) ЗУ оценивают временами

считывания, записи и длительностями циклов

чтения/записи.

Рис. 4.1. Типичные

сигналы ЗУ (а) и их

временные диаграммы (б)

А — адрес,

разрядность которого n

определяется числом ячеек

ЗУ, т. е. максимально возможным числом

хранимых в ЗУ слов.

CS — (Chip Select) или СE (Chip Enable),

который разрешает или запрещает работу

данной микросхемы;

R/W — (Read/Write) задает выполняемую

операцию (при единичном значении —

чтение, при нулевом - запись);

DI и DO (Data Input) и (Data Output) -—

шины входных и выходных данных,

разрядность которых m определяется

организацией ЗУ (разрядностью его ячеек).

В некоторых ЗУ эти линии объединены.

Классификация ЗУ

Для классификации ЗУ важнейшим признаком

является способ доступа к данным.

При адресном доступе код на адресном входе

указывает ячейку, с которой ведется обмен. Все

ячейки адресной памяти в момент обращения

равнодоступны.

Адресные ЗУ делятся на RAM (Random Access

Memory) u ROM (Read-Only Memory).

RAM-ОЗУ. Оперативные ЗУ хранят данные, участвующие в обмене при исполнении текущей

программы, которые могут быть изменены в

произвольный момент времени. Запоминающие

элементы ОЗУ, как правило, не обладают

энергонезависимостью.

ROM-ПЗУ, содержимое либо вообще не

изменяется, либо изменяется, но редко и в

специальном режиме. Для рабочего режима это

"память только для чтения".

RAM делятся на статические и динамические. В

первом варианте запоминающими элементами

являются триггеры, сохраняющие свое состояние.

пока схема находится под питанием и нет новой

записи данных. Во втором варианте данные

хранятся в

виде зарядов

конденсаторов,

образуемых

элементами

МОП-структур.

Саморазряд конденсаторов ведет к разрушению

данных, поэтому они должны периодически

(каждые

несколько

миллисекунд)

регенерироваться. В то же время плотность

упаковки динамических элементов памяти в

несколько раз превышает плотность упаковки,

достижимую в статических RAM.

Регенерация данных в динамических ЗУ

осуществляется

с

помощью

специальных

контроллеров. Разработаны также динамические

ЗУ со встроенную систему регенерации. Такие ЗУ

называют квазистатическими.

Статические ЗУ называются SRAM (Static RAM),

а динамические — DRAM (Dynamic RAM).

Статические ОЗУ можно разделить на

асинхронные, тактируемые и синхронные

(конвейерные).

В

асинхронных

сигналы

управления могут задаваться как импульсами, так

и уровнями. В тактируемых ЗУ некоторые

сигналы обязательно должны быть импульсными.

В конвейерный тракт передачи данных, синхронизируемый от тактовой системы процессора,

что дает повышение темпа передач данных в

несколько

раз.

Динамические

ЗУ

характеризуются наибольшей информационной

емкостью и невысокой стоимостью, поэтому

именно они используются как основная память

ЭВМ.

Постоянная память типа ROM (М)

программируется при изготовлении методами

интегральной технологии с помощью одной из

используемых при этом масок. Присутствие Р(от

Programmable). Ее содержимое записывается либо

однократно (в PROM), либо может быть заменено

путем стирания старой информации и записи

новой (в EPROM и EEPROM). В EPROM стирание

выполняется с помощью облучения кристалла

ультрафиолетовыми лучами. В EEPROM стирание

производится электрическими сигналами.

Пам

ять типа

Flash по

запомина

ющему

элементу

подобна

памяти

типа

EEPROM,

но

схемотехн

ика

отличаетс

я, поэтому

ее

выделили

в

отдельну

ю группу.

В ЗУ

с

последова

тельным

доступом

некоторую

записываемые данные образуют

очередь.

Прямой порядок считывания имеет место в

буферах FIFO (First In — First Out), а также в

файловых и циклических ЗУ.

Разница между памятью FIFO и файловым

ЗУ состоит в том, что в FIFO запись в пустой

буфер сразу же становится доступной для чтения,

т. е. поступает в конец цепочки (модели ЗУ). В

файловых ЗУ данные поступают в начало цепочки

и появляются на выходе после некоторого числа

обращений, равного числу элементов в цепочке.

Записываемые данные объединяют в блоки,

обрамляемые специальными символами конца и,

начала (файлы). В циклических ЗУ слова доступны

одно за другим с постоянным периодом,

определяемым емкостью памяти. К такому типу

среди

полупроводниковых

ЗУ

относится

видеопамять (VRAM).

Считывание в обратном порядке свойственно

буферным стековым ЗУ, LIFO (Last In — First Out).

Ассоциативный доступ реализует поиск

информации по некоторому признаку, а не по ее

расположению в памяти (адресу или месту в

очереди).

На

выход

выдаются

слова,

удовлетворяющие признаку. Основная область

применения ассоциативной памяти в современных

ЭВМ — кэширование данных.

Основные типы ЗУ на интегральных

микросхемах.

Память в настоящее время делится выполняется на

интегральных микросхемах

Для классификации ЗУ важнейшим признаком

является способ доступа к данным.

При адресном доступе код на адресном входе

указывает ячейку, с которой ведется обмен. Все

ячейки адресной памяти в момент обращения

равнодоступны.

Адресные ЗУ делятся на RAM (Random Access

Memory) u ROM (Read-Only Memory).

RAM-ОЗУ. Оперативные ЗУ хранят данные, участвующие в обмене при исполнении текущей

программы, которые могут быть изменены в

произвольный момент времени. Запоминающие

элементы ОЗУ, как правило, не обладают

энергонезависимостью.

ROM-ПЗУ, содержимое либо вообще не

изменяется, либо изменяется, но редко и в

специальном режиме. Для рабочего режима это

"память только для чтения".

RAM делятся на статические и динамические. В

первом варианте запоминающими элементами

являются триггеры, сохраняющие свое состояние.

пока схема находится под питанием и нет новой

записи данных. Во втором варианте данные

хранятся в виде зарядов конденсаторов,

образуемых элементами МОП-структур.

Саморазряд конденсаторов ведет к разрушению

данных, поэтому они должны периодически

(каждые несколько миллисекунд)

регенерироваться. В то же время плотность

упаковки динамических элементов памяти в

несколько раз превышает плотность упаковки,

достижимую в статических RAM.

Регенерация данных в динамических ЗУ

осуществляется с помощью специальных

контроллеров. Разработаны также динамические

ЗУ со встроенную систему регенерации. Такие ЗУ

называют квазистатическими.

Статические ЗУ называются SRAM (Static RAM),

а динамические — DRAM (Dynamic RAM).

Статические ОЗУ можно разделить на

асинхронные, тактируемые и синхронные

(конвейерные). В асинхронных сигналы

управления могут задаваться как импульсами, так

и уровнями. В тактируемых ЗУ некоторые

сигналы обязательно должны быть импульсными.

В конвейерный тракт передачи данных, синхронизируемый от тактовой системы процессора,

что дает повышение темпа передач данных в

несколько раз. Динамические ЗУ

характеризуются наибольшей информационной

емкостью и невысокой стоимостью, поэтому

именно они используются как основная память

ЭВМ.

Постоянная память типа ROM (М)

программируется при изготовлении методами

интегральной технологии с помощью одной из

используемых при этом масок. Присутствие Р(от

Programmable). Ее содержимое записывается либо

однократно (в PROM), либо может быть заменено

путем стирания старой информации и записи

новой (в EPROM и EEPROM). В EPROM стирание

выполняется с помощью облучения кристалла

ультрафиолетовыми лучами. В EEPROM стирание

производится электрическими сигналами.

Интегральные ПЗУ выпускаются трех видов:

масочные ПЗУ (ROM), программируемые в

процессе изготовления с помощью

индивидуальных фотошаблонов (масок) по заказам

потребителя;

однократно программируемые ПЗУ (ППЗУ,

PROM), в которых запись информации

производится потребителем путем избирательного

нарушения однородности исходной матрицы ЭП

импульсами электрического тока;

препрограммируемые ПЗУ (^ РПЗУ, EPROM,

EEPROM), в которых запись информации может

изменяться неоднократно электрическим

способом.

Микросхемы ПЗУ построены также по принципу

матричной структуры накопителя. Функции ЭП в

микросхемах ПЗУ выполняют перемычки в виде

проводников, диодов или транзисторов межжу

шинами строк и столбцов в накопителе. В такой

матрице наличие перемычки соответствует,

например, 1, а ее отсутствие – 0. Микросхемы ПЗУ

имеют словарную организацию, и поэтому

информация считывается в форме

многоразрядного кода, т.е. словом. Совокупность

ЭП в матрице накопителя, в которой размещается

слово, называют ячейкой памяти (ЯП). Число ЭП в

ЯП определяет ее разрядность n. Каждая ЯП имеет

свой адрес, и для обращения к определенной ЯП

нужно подвести сигналы кода, соответствующего

данной ячейке адреса. Число ячеек памяти равно

2m, а информационная емкость микросхемы – 2m

n бит.

Занесение информации в микросхемы ПЗУ, т.е. их

программирование, осуществляют, в основном,

двумя способами. Один способ заключается в

формировании в накопителе перемычек в местах

пересечения строк и столбцов матрицы через

маску на заключительной технологической стации

изготовления микросхемы ПЗУ. Такие

микросхемы ПЗУ называют масочными. Другой

способ программирования микросхемы ПЗУ

основан на пережигании легкоплавких перемычек

в тех пересечениях шин строк и столбцов, куда

должен быть записан 0 или 1, в зависимости от

принятого кодирования. В исходном состоянии

такая микросхема имеет в матрице перемычки во

всех пересечениях строк и столбцов.

Программирование осуществляет пользователь

электрическими импульсами с помощью

устройства для программирования, называемого

программатором.

Существует разновидность микросхем ПЗУ,

допускающая неоднократное

перепрограммирование (репрограммирование).

Элементом памяти в микросхемах

репрограммируемых ПЗУ (РПЗУ) является МДПтранзистор, обладающий свойством переходить в

состояние проводимости под воздействием

импульса программирующего напряжения и

сохранять это состояние длительное время (тысячи

часов). Данный эффект обусловлен накоплением

электрического заряда в подзатворном

диэлектрике. Если на транзистор не

воздействовать импульсом программирующего

напряжения, то он сохранит закрытое для

электрического тока состояние. Для стирания

информации перед новым циклом

программирования необходимо вытеснить

накопленный под затвором заряд. В зависимости

от способа выполнения этой операции микросхемы

РПЗУ разделяют на два вида: со стиранием

электрическим сигналом (РПЗУ-ЭС) и

ультрафиолетовым светом (РПЗУ-УФ), которым

полупроводниковый кристалл облучают через

специальное окно в крышке корпуса. Микросхемы

РПЗУ сохраняют информацию длительное время

без питания, т.е. являются энергонезависимыми.

ПЗУ делится на: масочные, программируемые

(ППЗУ, PROM), перепрограммируемые

(EFROM) – могут быть с ультрафиолетовым и

электрическим стиранием (перезаписью), ПЛМ

– программируемые логические матрицы.

Флэш-память

Флэш-память (Flash-Memory) по типу

запоминающих элементов и основным принципам

работы подобна памяти типа E2PROM, однако ряд

архитектурных и структурных особенностей

позволяют выделить ее в отдельный класс.

В схемах Флэш-памяти не предусмотрено

стирание отдельных слов, стирание информации

осуществляется либо для всей памяти

одновременно, либо для достаточно больших

блоков. Понятно, что это позволяет упростить

схемы ЗУ

Термин Flash по одной из версий связан с

характерной особенностью этого вида памяти —

возможностью одновременного стирания всего ее

объема. Одновременное стирание всей

информации ЗУ реализуется наиболее просто, но

имеет тот недостаток, что даже замена одного

слова в ЗУ требует стирания и новой записи для

всего ЗУ в целом. Для многих применений это

неудобно. Поэтому наряду со схемами с

одновременным стиранием всего содержимого

имеются схемы с блочной структурой, в которых

весь массив памяти делится на блоки, стираемые

независимо друг от друга. Объем таких блоков

сильно разнится: от 256 байт до 128 Кбайт.

Число циклов репрограммирования для Флэшпамяти хотя и велико, но ограничено, т. е. ячейки

при перезаписи "изнашиваются". Чтобы увеличить

долговечность памяти, в ее работе используются

специальные алгоритмы, способствующие

"разравниванию" числа перезаписей по всем

блокам микросхемы.

11 Особенности построения и работы

микросхем ОЗУ динамического типа.

Внутренняя структура в динамических элементах

памяти выполнена в виде матрицы.

Одна половина – адрес строки, другая столбцов.

Адрес идущий на дешифратор обеспечивает

выборку, прием и передачу данных. При

выполнении любой операции обращения к такой

памяти будет происходить регенерация строки.

Для экономии числа внешних выводов в

динамической памяти используется раздельная

адресация столбцов и строк. Для выполнения

операций регенерации адрес столбца подавать не

обязательно.

Обязательным

условием

эксплуатации является перебор всех строк за

допустимое время регенерации.

Регенерация может быть : открытого и скрытого

типа.

Открытая: за время обязательно все ячейки

должны быть перебраны.

Трег - цепи регенерации

Трег – в течение этого времени надо

регенерировать Регенерация работа все ячейки

памяти.

В системе реального времени мы будем терять

какую-то информацию в течение времени

регенерации. Эта система недоступна. Для того,

чтобы этого не было используют механизмы

скрытой регенерации.

Скрытая регенерация.

1. Процессорно-зависимые методы (системно

ориентированные) – во временном расписании

работы процессора можно найти цикл, когда

происходит обращение к системной шине, а

память уже не используется. Такой подход уже не

используется.

2.

Процессорно-независимые

методы

(независимая) – незаметна для простых запросов

из вне.

Ставим аппарат, который непрерывно перебирает

адреса строк со скоростью предельно допустимой

и так идет регенерации. Далее приходит запрос из

вне, перебор адресов заканчивает внешний цикл,

по окончании происходит перебор адресов, с того

адреса, на котором он остановился.

Первые используют особенности организации

циклов процессора. (ША никто не использует).

Преимущество: нет промежутков времени, когда

система не реагирует с внешним миром.

Недостаток: только под определенный процессор.

Вторые. Сделать так, чтоб никто не знал, что идет

регенерация. Постоянная регенерация при запросе

извне останавливается и обращение из внешнего

адреса после окончания внешнего запроса

продолжается регенерация.

Адрес стоки и Адрес столбца передаются

поочередно, поэтому адрес подается в два приема.

Схема сопряжения при такой организации

матрицы памяти должна содержать дешифратор

адреса строк и обеспечивать выборку сигналов

управления таким образом, чтобы происходило

обращение только к одной строке при чтении или

записи информации. Модуль сопряжения должен

обеспечивать сопряжение системных интерфейсов

и вырабатывать сигналы (адрес, DI, управляющие

сигналы). Если микросхемы ЗУ динамического

типа, то имеет смысл предусмотреть обращение ко

всем микросхемам матрицы одновременно в

циклах регенерации. Это значительно сократит

время на регенерацию памяти. Если нужно

построить память 1М*16, а микросхемы 1М*8, то

Память работает в режиме запроса, т.к. внешний

запрос имеет внешний приоритет, то как только он

приходит, то выполняется регенерация. Этот

аппарат может находиться снаружи,

И тогда схема регенерации будет внешней или

может находиться на кристалле памяти.

При обращении с микросхеме, т.е. для

чтения/записи необходимо подать код адреса

строки или сигнал RAS (строб адреса строки),

затем с нормированными задержками должен быть

код адреса столбца и сигнал стробирования

столбца CAS. К моменту подачи кода адреса

столбца на вход данных должен быть подан

записываемый код, который сигналом CAS

фиксируется в микросхеме. Причем время

удержания данных относительно сигнала CAS

нормируется. Для увеличения скорости работы в

микросхемах

используются

приемы

для

уменьшения времени передачи данных.

12Построение модулей памяти ЭВМ на

интегральных микросхемах.

Память вычислительной системы обычно состоит

из одного или нескольких модулей. Каждому

модулю в адресном пространстве отводится

некоторое место. Конструктивно модуль памяти

может представлять отдельное устройство, плату

или находиться на той же плате что и ЦП. Со

структурной точки зрения можно указать

достаточно общую структурную схему модуля

памяти – состоит из 2-ч частей: системная шина

(или контроллер памяти), устройство сопряжения

и массив микросхем ЗУ.

Набор микросхем ЗУ

Обычно массив микросхем ЗУ организуетсяв виде

матрицы, размер которой определяется емкостью

модуля памяти и микросхемами, из которых этот

модуль строится. Будем считать, что емкость

микросхем ЗУ записывается выражением:M=N*n ,

где N - число адресных элементов n - число

разрядов (бит) в адресе элемента

Емкость модуля ЗУ: Mзу=Nзу*nзу

Число микросхем в строке и столбце матрицы

определяется из выражений:

число микросхем в строке матрицы: m=nзу/n

число микросхем в столбце матрицы: k=Nзу/N

Логика соединения и управления микросхем в

такой

матрице

соответствует

следующим

правилам:

1) адресные цепи всех микросхем соединяются

параллельно

2) входы и выходы данных микросхем

соединяются параллельно в рамках одного столбца

матрицы, образуя некоторую разрядную группу

3) линии управления микросхемами соединяются

параллельно в рамках строки матрицы, с целью

обеспечения независимого обращения к строке в

режимах чтения и записи.

Структура:ША

Структура устройства сопряжения зависит от

большого числа факторов, представить ее для всех

ситуаций сложно. Основные факторы, которые

придется учитывать при разработке устройства

сопряжения, следующие:

1.Число

магистралей,

к

которым

будет

подключаться модуль памяти одновременно

(много портовая память).

2.Тип магистралей, к которым будет подключаться

модуль памяти.

3.Тип памяти (ее адресация)

4.Емкость и организация

отдельных

микросхем

памяти.

5.Использование

или

наличие схем контроля и

помехозащищенного

кодирования.

6.Наличие

средств

реконфигурации

7.Наличие

средств

повышения

производительности

Обобщенная структура устройства сопряжения

Всегда возникает проблема, сколько ставить

памяти.

Наращиваемая (масштабируемая) память – чтобы

память была дешевле.

Наращиваемая память реализуется двумя путями:

1)

Увеличение емкости памяти установкой

нескольких независимых модулей памяти

Достоинства – независимая подсистема, работают

параллельно=>преимущества по

структурной

организации системы и надежности (при выходе

из строя одного модуля, его заменит другой и т.д.)

и производительности.

Недостатки – большая стоимость.

Модуль ЗУ имеет выход для подсоединения точно

такого же модуля для увеличения памяти.

2) Дублирование матриц памяти. Устройство

сопряжения одно, а к нему можно подключать

несколько модулей. Устройство сопряжения

делается с запасом для большого размера памяти.

Хуже структурная организация, надежность, но

дешевле. В дешевых системах и в персональных

компьютерах.

В промышленности модули памяти выпускались

отдельно, применяется 1-ый подход, я для

персональных – 2-ой подход.

13Структурные методы повышения

производительности ЗУ.

99,9% систем соответствуют Фон-неймановской

модели (процессор и память задают скоростные

характеристики системы)

Способы повышения производительности

отдельно взятой памяти.

Уменьшать временные издержки не подходит, т.к.

мы не делаем микросхему.

Структурное решение:

1.

Вводить параллельность (в пространстве и

времени). В пространстве - ставится несколько

работников, делающих одно и тоже. Во времени –

строим конвейер, т.е. параллелим действия на

разных этапах.

Память делается из нескольких модулей

способных работать независимо и самостоятельно.

При организации доступа используется механизм

чередования, который осуществляет передачу

подряд идущих запросов к разным модулям.

1.Расслоение памяти.

Допустим, имеем модуль памяти, который состоит

из нескольких модулей.

М1, М2, М3 – три модуля памяти, которые могут

работать параллельно и независимо. Каждый

модуль обладает конечным быстродействием.

τ – время обращения цикла к памяти.

Нужна наибольшая вероятность попадания

адресов. Предложем механизм обработки по

разделу адреса т.к ЦП идет по подряд идущим

адресам. Т.е используем механизм чередования по

кратному числу модулей. При этом эффективность

КЭШа возрастает т.к вероятность выбора по

каждоидущим адресам увеличивается.

Реализация 2 подхода к реализации метода

расслоения:

построение памяти с буферизацией

адресов.

построение памяти с буферизацией

данных.

Буферизация адресов.

Перед модулями памяти ставится буфер адресов

(БА). В простейшем случае это регистр в сложном

очередь адресов (несколько регистров).

Как сделать так, чтобы обращение было к разным

модулей? Это делается за счет разделения

адресного пространства: адреса модуля делятся

поочередно, (если два модуля, то чередование

через 1, 4 модуля – 0,4, - в первом модуле, 1,5 – во

втором и т.д.)

УУ анализирует занятость буфера. Если он

пустой, то цикл обр-я фиксируется в нем, если

нет, т.е. туда приходит адрес и выдается сигнал

на выполнение. Адреса ячеек нумеруют так,

чтобы модули памяти были как единое целое, т.е.

подряд идущие адреса разным модулям.ШФ шинный формировательТакая организация требует

усложнения устройств управления.

Буферизация данных.

Модули памяти

включены

параллельно по

ША, и работают

параллельно

(обращение ко

всем модулям

происходит

одновременно).

Если число

модулей =2n, то часть разрядов общая, а часть

разрядов задают номер модуля, т.е. память с

широким выборным УУ анализирует адрес,

который поступил.

На входе буферный регистр памяти (только за

одно обращение из памяти забирается не одно

(допустим слово), а два и затем нам не надо лезть в

память за вторым словом, а берем его и буфера

данных).

Модули памяти работают синхронно. Считывается

длинное машинное слово, следующее можно

извлекать из буфера, а не из памяти.

Такая память будет давать выигрыш, если

обращение будет по подряд идущим адресам, но

зато дёшево.

Такая схема будет работать если считывание

ведется по подряд идущим адресам

2.Для повышения производительности часто

используют особенности построения микросхем

ОЗУ. Наращивание числа накопителей (для

дешевых машин или для машин реализованных на

одной плате). При таком подходе устройство

управления изначально делается с запаслм по упрю блоками накопителя. Исп-ся в промышленных

сферах.

А далее существуют проблемы синхронизации.

Число изменения синхросигнала в 2 раза быстрее,

чем данных. Высокочастотные гармоники

формируют фронты т.е если ширина пропускания

меньше ширины импульса

14.КЭШ память: общие идеи и проблемы.

1)Конвейерный прием

2)Принцип локальности

Принцип

локальности

и

иерархическая

организация памяти как компромисс между

скоростью и производительностью.

Идея: В данный момент времени нам вся

информация не нужна. Разные блоки информации

используются с разной частотой (какая-то чаще,

какая-то реже).

Создается иллюзия, что количество памяти как у

нижнего, а скоростькак у верхнего.

Эта штуковина двигается в информационном

пространстве. Память надо делать в соответствии с

этой идеологией.

1-й уровень – ОЗУ, 2-й уровень – магнитная лента.

Идеология подключения:

Такая система работает эффективнее чем чаще

будет обращаться к СОЗУ. Необходимо, чтобы в

СОЗУ была та информация, которая нам нужна в

данный момент.

Управление СОЗУ:

Буферная

память

делается

программно видимая, т.е. адресуема

и тогда все лежит на совести

программиста. Управляет человек –

программист.

Программно невидимая память, т.е.

содержимое

формируется

автоматически и характеристики

будут зависеть от алгоритмов.

Автоматическое управление.

1.Один из механизмов – регистр общего

назначения (РОН) доступен программисту.

2. Один из механизмов – КЭШ.При заполнении

буферной памяти автоматически, надо решить ряд

проблем. Наиболее приемлемый путь к решению

проблем это построение КЭШ памяти.

Организация КЭШ памяти.

Проблемы:

1.

Что писать в КЭШ и когда.

2.

Как узнать есть ли в КЭШ то, что

нам необходимо.

3.

Когда производить запись в КЭШ?

4.

Как сделать, чтоб объем КЭШ и ОЗУ

были

бы

равны.

(Проблема

когерентности (согласования) КЭШ

и ОЗУ).

5.

Задача удаление из КЭШа.

Организация КЭШ памяти

Структура:

ЦП и ОЗУ не знают о существовании КЭШ.Только

сама КЭШ знает, есть она или нет.

1.) В КЭШ надо писать до того когда нам данные

понадобятся и, и что понадобится. В КЭШ в

основном используется механизм записи по

запросу, если со стороны запросов есть, то в КЭШ

переводится.

Что писать: используется принцип локальности

Принцип

временной

локальности.

Принцип

пространственной

локальности.

Временная локальность – наиболее вероятными

данными к использованию являются те, которые

использовались в данный момент.

Пространственная локальность – в следующий

момент времени будут обрабатываться те данные,

которые лежат рядом в памяти.

Побочные проблемы:

- как выбирать эту окрестность если пишем

пошаговую программу, то лучше выбирать эту

окрестность в сторону увеличения адресов.

Критерий выбора: простота построения системы –

проще, чтобы эта окрестность была равна 2n.

Можно расположить в любом месте адресного

пространства, но если начальный адрес этой

области сделаем кратным 2n, то адрес памяти будет

состоять из двух частей:

2.) Как определить наличие в КЭШ необходимой

информации?

Можно сделать КЭШ память ассоциативной.

Кроме адресной возможно построение безадресной

памяти, т.е. памяти при обращении к которой

адрес не нужен.

Безадресная память бывает двух типов:

Магазинного типа.

Делится в свою очередь также на 2 типа: магазин

1-го типа и магазин 2-го типа, т.е. формируется

принцип очередности: 1) FIFO, 2)LIFO

Ассоциативного типа.

Имеется 2 блока памяти, которые взаимосвязаны.

Запись данных берется на любое свободное место:

и записываются признаки и данные. Чтение

информации: извне подается признак, который

сравнивается со всеми записями признаков и там

где есть совпадение, производится выборка

данных.В адресной памяти при обращении идет

привязка к месту, а в ассоциативной – привязка к

признаку.

Ассоциативная память более дорогая.

В признаке записывается № области (адрес).

Возможны два способа записи в КЭШ память:

1)метод сквозной записи;

2)метод обратной записи.

Первый метод предполагает наличие двух копий

данных: одной в КЭШ памяти, а другой в ОЗУ.

Запись выполняется одновременно и в КЭШ и в

ОЗУ. В результате системная шина и процессор

работают с большой нагрузкой, поскольку на

каждую операцию изменения данных приходится

две операции записи. Метод сквозной записи

имеет преимущество в том, что ОЗУ всегда имеет

свежую копию данных, что важно в

мультипроцессорных системах и при организации

ввода-вывода данных. Кроме того сквозная запись

имеет простую схемную реализацию.

При использовании метода обратной записи цикл

записи происходит только в КЭШ памяти, если в

КЭШе находится строка, к которой идет

обращение (КЭШ попадание). Если адресуемой

строки в КЭШ нет, то информация записывается

сразу в ОЗУ. При КЭШ попадании запись в ОЗУ

происходит только при замещении строки КЭШа.

Для сокращения частоты копирования строк

запись в ОЗУ происходит только в том случае,

если замещаемая строка КЭШа была

модифицирована, то есть изменена. Для

определения факта изменения строки с каждой

строкой КЭШа связывают так называемый «бит

модификации». Если строка в КЭШ не

модифицирована, то обратное копирование

отменяется, поскольку ОЗУ содержит туже самую

информацию, что и КЭШ память.

Преимущество данного метода заключается в том,

что запись выполняется со скоростью КЭШ

памяти. А несколько записей на одну и туже

строку КЭШа требует только одной записи – в

ОЗУ, что снижает загрузку системной шины.

15.КЭШ память прямого отображения:

алгоритм работы и структурная схема.

Адресное пространство памяти разбивается на

модули одинакового размера, равного объему

КЭШ. При такой организации адрес ячейки памяти

внутри ОЗУ может быть представлен следующим

образом.

Адрес распадается на 3 части:

СС – степень сравнения.

Строка переписывается в тот же адрес в КЭШ, где

она была в ЗУ.

Данные – обычная однородная память.

Тэги – обычная адресная память.При записи в одни

адреса, старое содержимое стирается. В тэгах

хранятся

номера

блоков.Используют

многоуровневые

КЭШ

и

естественно

многоассоциативные КЭШ (для того чтобы не

затирать

предыдущую

информацию

по

одинаковым адресам)

Структурная схема

3.) Обеспечение связанности данных КЭШ и ОЗУ.

Наличие КЭШ приводит к тому, что в КЭШ и в

ОЗУ имеются одинаковые данные под одним

идентификатором, но если производятся какие-то

вычисления, то результат записывается не в ОЗУ, а

в

КЭШ.

Таким

образом,

под

одним

идентификатором в КЭШ и в ОЗУ разные данные

(в ОЗУ нет результатов вычисления).

Обеспечение когерентности работы с данными в

случае записи со стороны второго активного.

Приемы:

#Запрет работы второго активного с Кэшируемой

областью памяти.

#При каждой операции внешней записи в память

производится очистка КЭШ.

#Прозрачность аппаратуры – группа методов.

Делается попытка анализировать запросы к

памяти.

1)Слежение за адресами записи в память и

спулирование соответствующих записей в КЭШ.(в

486 и выше). Это самый простой вариант.

2)Аппаратура не только сбрасывает строки в КЭШ,

но и изменяет его содержимое при записи в ОЗУ

Кэш прямого отображения

Кэш прямого отображения представляет собой

наиболее простой с точки зрения аппаратных

затрат вариант решения задачи быстрого

определения того, имеется ли в данный момент в

кэш-памяти

информация,

затребованная

очередным обращением к оперативной памяти.

При

такой

организации

кэш-памяти

вся

кэшируемая

оперативная

память

(условно

разбивается на равные страницы, размер которых

равен емкости кэш-памяти, что показано на рис.

40. Кэш, в свою очередь, разбивается на строки по

32 байта, соответствующие одному стандартному

пакетному циклу обращения к динамической