НИИЭТ

реклама

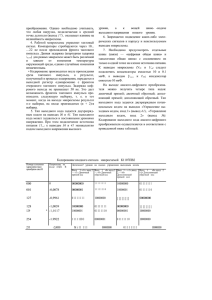

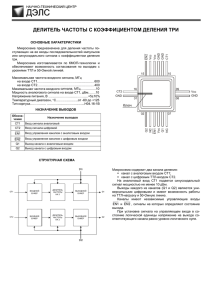

НИИЭТ 14-разрядный ЦАП с токовым выходом 1273ПА5У Корпус Н16.48-1В Быстродействующий ЦАП. Предназначен для применения в передающих каналах средств связи, базовых станциях, широкополосных системах и контрольно-измерительной аппаратуре • • • • • • • Частота подачи входных данных 160 МГц Частота обновления выходных данных 400 МГц Интерфейс – параллельный Время установления (до 0,025 %) ….11 нс (тип.) 2-х интерполяционный фильтр Источник опорного напряжения 1.2 В Внутренний умножитель частоты 2х/4х Основные параметры Параметр Интегральная нелинейность Дифференциальная нелинейность Выходное опорное напряжение Напряжение питания цифровой и аналоговой части Потребляемый ток по выводу #VCC Общие гармонические искажения на частоте fIN = 65 МГц и fOUT = 1 МГц Выходной шум Потребляемая мощность Диапазон рабочих температур Обозначение INL DNL UREFIO Единица Величина измерения ± 3.5 ЕМР ± 2.0 ЕМР от 1.14 В до 1.26 U#VCC U∩VCC 3.3 ± 0.2 В IO#VCC не более 44.0 мА ТНD - 70 дБ ON PD ТА 80 300 - 60/+ 85 пА/ Гц мВт ˚С НИИЭТ 1273ПА5У Структурная схема ЦАП CLKGND CLKVCC SLEEP RESET PLLLOCK DIV0 DIV1 LPF CLK+ Умножитель частоты PLLVCC CLK-# PLLGND ЦАП IOUTA IOUTB Цифровой КИХ Источник опорного напряжения и управляющий усилитель фильтр #VCC #GND MOD0 MOD1 ∩VCC ∩GND REFIO Схема расположения выводов в корпусе Н16.48-1В REFLO FSADJ НИИЭТ 1273ПА5У Условное графическое изображение микросхемы 45 46-48, 1-9 DB13 DB12-DB1 10 DB0 11 MOD0 12 MOD1 20 RESET 21 DIV1 22 DIV0 23 CLK+ 24 CLK-# 29 LPF 30 SLEEP 32 REFLO 34 DAC IOUTB 36 IOUTA 37 PLLLOCK 19 NC 17, 18 REFIO 33 FSADJ #GND 13, 14, 43, 44 25 CLKGND #VCC 15, 16, 41, 42 26 CLKVCC 27 PLLGND ∩GND 31, 35, 38 28 PLLVCC ∩VCC 39, 40 НИИЭТ 1273ПА5У Функциональное назначение выводов Номер вывода 45 46–48, 1–9 10 11 Обозначение вывода DB13 DB12–DB1 DB0 MOD0 Функциональное назначение вывода Старший сигнальный бит (MSB) Биты данных 12–1 Младший сигнальный бит (LSB) Вход включения фильтра высокой частоты (активный высокий – «1») 12 MOD1 Вход включения режима заполнения нулями (активный высокий – «1») 20 RESET Сброс внутреннего делителя ФАПЧ 21, 22 DIV1, DIV0 Входы выбора коэффициента деления делителя ФАПЧ 23 CLK+ Прямой вход дифференциального тактового сигнала 24 CLK-# Инверсный вход дифференциального тактового сигнала 29 LPF Вход фильтра ФАПЧ 30 SLEEP Вход включения режима низкого потребления энергии 32 REFLO Управление внутренним ИОН (высокий – «1» – отключение внутреннего ИОН) 34 FSADJ Вход установки тока полной шкалы 19 PLLLOCK Вывод индикации захвата фазы ФАПЧ 33 REFIO Вход/выход ИОН 36 IOUTB Дополнительный токовый выход ЦАП 37 IOUTA Прямой токовый выход ЦАП 13, 14, 43, #GND Общий вывод цифровой части микросхемы 44 15, 16, 41, #VCC Вывод питания цифровой части микросхемы 42 25 CLKGND Общий вывод тактового сигнала 26 CLKVCC Вывод питания тактового сигнала 27 PLLGND Общий вывод ФАПЧ 28 PLLVCC Вывод питания ФАПЧ 31, 35, 38 ∩GND Общий вывод аналоговой части микросхемы 39, 40 ∩VCC Вывод питания аналоговой части микросхемы 17, 18 NC Выводы не задействованы