PDF файл с описанием регистров

реклама

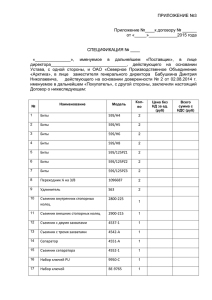

Регистры ЦАП STM32L15x DAC control register (DAC_CR) Смещение адреса: 0x00 Значение после сброса: 0x0000 0000 Биты 31:30 зарезервированы Бит 29 DMAUDRIE2: Разрешение прерывания в канале 2 при отставании запроса DMA. Устанавливается и очищается программно. 0: Прерывание запрещено 1: Прерывание разрешено Бит 28 DMAEN2: Разрешение запроса DMA в канале 2. Устанавливается и очищается программно. 0: Режим DMA запрещен 1: Режим DMA разрешен Биты 27:24 MAMP2[3:0]: Выбор маски/амплитуды канала 2 Эти биты записываются программно для выбора маски в режиме генерации шума или амплитуды в режиме генерации треугольных импульсов 0000: Немаскирован бит 0 LFSR/амплитуда треугольных импульсов равна 1 0001: Немаскированы биты [1:0] LFSR/ амплитуда треугольных импульсов равна 3 0010: Немаскированы биты [2:0] LFSR/ амплитуда треугольных импульсов равна 7 0011: Немаскированы биты [3:0] LFSR/ амплитуда треугольных импульсов равна 15 0100: Немаскированы биты [4:0] LFSR/ амплитуда треугольных импульсов равна 31 0101: Немаскированы биты [5:0] LFSR/ амплитуда треугольных импульсов равна 63 0110: Немаскированы биты [6:0] LFSR/ амплитуда треугольных импульсов равна 127 0111: Немаскированы биты [7:0] LFSR/ амплитуда треугольных импульсов равна 255 1000: Немаскированы биты [8:0] LFSR/ амплитуда треугольных импульсов равна 511 1001: Немаскированы биты [9:0] LFSR/ амплитуда треугольных импульсов равна 1023 1010: Немаскированы биты [10:0] LFSR/ амплитуда треугольных импульсов равна 2047 ≥1011: Немаскированы биты [11:0] LFSR/ амплитуда треугольных импульсов равна 4095 Биты 23:22 WAVE2[1:0]: Разрешение генерации шума/треугольного сигнала в канале 2 Устанавливаются и сбрасываются программно 00: генерация запрещена 01: Разрешена генерация шума 1x: Разрешена генерация треугольного сигнала Примечание: используется, если бит TEN2=1 (разрешен запуск в канале 2) Биты 21:19 TSEL2[2:0]: Выбор источника запуска для канала 2 Эти биты задают внешнее событие, используемое для запуска канала 2 ЦАП 000: Таймер 6 001: Зарезервирован 010: Таймер 7 011: Таймер 9 100: Таймер 2 101: Таймер 4 110: Внешняя линия 9 111: Программный запуск Примечание: Используется только если бит TEN2=1 (разрешен запуск в канале 2) Бит 18 TEN2: Разрешение запуска в канале 2 Этот бит устанавливается и очищается программно для разрешения/запрета запуска в канале 2 0: Запуск в канале 2 запрещен и данные, записанные в регистр DAC_DHRx, передаются в регистр DAC_DOR2 через один такт APB1 1: Запуск в канале 2 разрешен и данные из регистра DAC_DHRx передаются в регистр DAC_DOR2 через 3 такта APB1 Примечание: когда выбран программный запуск, передача данных из DAC_DHRx в DAC_DOR2 займет всего один такт APB1 Бит 17 BOFF2: Выходной буфер канала 2 Бит устанавливается и очищается программно для разрешения/запрета использования выходного буфера канала 2 0: Буфер подключен 1: Буфер отключен Бит 16 EN2: Разрешение работы канала 2 Бит устанавливается и очищается программно для разрешения/запрета работы канала 2 0: Канал 2 отключен 1: Канал 2 включен Биты 15:14 Зарезервированы Бит 13 DMAUDRIE1: Разрешение прерывания в канале 1 при отставании запроса DMA. Устанавливается и очищается программно. 0: Прерывание запрещено 1: Прерывание разрешено Бит 12 DMAEN1: Разрешение запроса DMA в канале 1. Устанавливается и очищается программно. 0: Режим DMA запрещен 1: Режим DMA разрешен Биты 11:8 MAMP1[3:0]: Выбор маски/амплитуды канала 1 Эти биты записываются программно для выбора маски в режиме генерации шума или амплитуды в режиме генерации треугольных импульсов 0000: Немаскирован бит 0 LFSR/амплитуда треугольных импульсов равна 1 0001: Немаскированы биты [1:0] LFSR/ амплитуда треугольных импульсов равна 3 0010: Немаскированы биты [2:0] LFSR/ амплитуда треугольных импульсов равна 7 0011: Немаскированы биты [3:0] LFSR/ амплитуда треугольных импульсов равна 15 0100: Немаскированы биты [4:0] LFSR/ амплитуда треугольных импульсов равна 31 0101: Немаскированы биты [5:0] LFSR/ амплитуда треугольных импульсов равна 63 0110: Немаскированы биты [6:0] LFSR/ амплитуда треугольных импульсов равна 127 0111: Немаскированы биты [7:0] LFSR/ амплитуда треугольных импульсов равна 255 1000: Немаскированы биты [8:0] LFSR/ амплитуда треугольных импульсов равна 511 1001: Немаскированы биты [9:0] LFSR/ амплитуда треугольных импульсов равна 1023 1010: Немаскированы биты [10:0] LFSR/ амплитуда треугольных импульсов равна 2047 ≥1011: Немаскированы биты [11:0] LFSR/ амплитуда треугольных импульсов равна 4095 Биты 7:6 WAVE1[1:0]: Разрешение генерации шума/треугольного сигнала в канале 1 Устанавливаются и сбрасываются программно 00: генерация запрещена 01: Разрешена генерация шума 1x: Разрешена генерация треугольного сигнала Примечание: используется, если бит TEN1=1 (разрешен запуск в канале 1) Биты 5:3 TSEL1[2:0]: Выбор источника запуска для канала 1 Эти биты задают внешнее событие, используемое для запуска канала 1 ЦАП 000: Таймер 6 001: Зарезервирован 010: Таймер 7 011: Таймер 9 100: Таймер 2 101: Таймер 4 110: Внешняя линия 9 111: Программный запуск Примечание: Используется только если бит TEN1=1 (разрешен запуск в канале 1) Бит 2 TEN1: Разрешение запуска в канале 1 Этот бит устанавливается и устанавливается программно для разрешения/запрета запуска в канале 1 0: Запуск в канале 1 запрещен и данные, записанные в регистр DAC_DHRx, передаются в регистр DAC_DOR1 через один такт APB1 1: Запуск в канале 1 разрешен и данные из регистра DAC_DHRx передаются в регистр DAC_DOR1 через 3 такта APB1 Примечание: когда выбран программный запуск, передача данных из DAC_DHRx в DAC_DOR1 займет всего один такт APB1 Бит 1 BOFF1: Выходной буфер канала 1 Бит устанавливается и очищается программно для разрешения/запрета использования выходного буфера канала 1 0: Буфер подключен 1: Буфер отключен Бит 0 EN1: Разрешение работы канала 1 Бит устанавливается и очищается программно для разрешения/запрета работы канала 1 0: Канал 1 отключен 1: Канал 1 включен DAC software trigger register (DAC_SWTRIGR) Смещение адреса: 0x04 Значение после сброса: 0x0000 0000 Биты 31:2 Зарезервированы Бит 1 SWTRIG2: программный запуск канала 2 Устанавливается и очищается программно для запуска преобразования 0: Никаких действий не производится 1: Программный запуск преобразования в канале 2 Примечание: Этот бит очищается аппаратно (через один такт APB1) после загрузки содержимого DAC_DHR2 в DAC_DOR2 Бит 0 SWTRIG1: программный запуск канала 1 Устанавливается и очищается программно для запуска преобразования 0: Никаких действий не производится 1: Программный запуск преобразования в канале 1 Примечание: Этот бит очищается аппаратно (через один такт APB1) после загрузки содержимого DAC_DHR1 в DAC_DOR1 DAC chanel1 12-bit right aligned data holding register (DAC_DHR12R1) Смещение адреса: 0x08 Значение после сброса: 0x0000 0000 Биты 31:12 Зарезервированы Биты 11:0 DACC1DHR[11:0]: 12-разрядные данные, выровненные вправо Эти биты записываются программно и содержат 12-разрядные данные для канала 1 DAC chanel1 12-bit left aligned data holding register (DAC_DHR12L1) Смещение адреса: 0x0C Значение после сброса: 0x0000 0000 Биты 31:16 Зарезервированы Биты 15:4 DACC1DHR[11:0]: 12-разрядные данные, выровненные влево Эти биты записываются программно и содержат 12-разрядные данные для канала 1 Биты 3:0 Зарезервированы DAC channel1 8-bit right aligned data holding register (DAC_DHR8R1) Смещение адреса: 0x10 Значение после сброса: 0x0000 0000 Биты 31:8 Зарезервированы Биты 7:0 DACC1DHR[7:0]: 8-разрядные данные, выровненные вправо Эти биты записываются программно и содержат 8-разрядные данные для канала 1 DAC chanel2 12-bit right aligned data holding register (DAC_DHR12R2) Смещение адреса: 0x14 Значение после сброса: 0x0000 0000 Биты 31:12 Зарезервированы Биты 11:0 DACC2DHR[11:0]: 12-разрядные данные, выровненные вправо Эти биты записываются программно и содержат 12-разрядные данные для канала 2 DAC channel2 12-bit left aligned data holding register (DAC_DHR12L2) Смещение адреса: 0x18 Значение после сброса: 0x0000 0000 Биты 31:16 Зарезервированы Биты 15:4 DACC2DHR[11:0]: 12-разрядные данные, выровненные влево Эти биты записываются программно и содержат 12-разрядные данные для канала 2 Биты 3:0 Зарезервированы DAC channel2 8-bit right aligned data holding register (DAC_DHR8R2) Смещение адреса: 0x1С Значение после сброса: 0x0000 0000 Биты 31:8 Зарезервированы Биты 7:0 DACC2DHR[7:0]: 8-разрядные данные, выровненные вправо Эти биты записываются программно и содержат 8-разрядные данные для канала 2 Dual DAC 12-bit right aligned data holding register (DAC_DHR12RD) Смещение адреса: 0x20 Значение после сброса: 0x0000 0000 Биты 31:28 Зарезервированы Биты 27:16 DACC2DHR[11:0]: 12-разрядные данные канала 2, выровненные вправо. Записываются программно. Биты 15:12 Зарезервированы Биты 11:0 DACC1DHR[11:0]: 12-разрядные данные канала 1, выровненные вправо. Записываются программно. Dual DAC 12-bit left aligned data holding register (DAC_DHR12LD) Смещение адреса: 0x24 Значение после сброса: 0x0000 0000 Биты 31:20 DACC2DHR[11:0]: 12-разрядные данные канала 2, выровненные влево. Записываются программно. Биты 19:16 Зарезервированы Биты 15:4 DACC1DHR[11:0]: 12-разрядные данные канала 1, выровненные влево. Записываются программно. Биты 3:0 Зарезервированы Dual DAC 8-bit right aligned data holding register (DAC_DHR8RD) Смещение адреса: 0x28 Значение после сброса: 0x0000 0000 Биты 31:16 Зарезервированы Биты 15:8 DACC2DHR[7:0]: 8-разрядные данные канала 2, выровненные вправо. Записываются программно. Биты 7:0 DACC1DHR[7:0]: 8-разрядные данные канала 1, выровненные вправо. Записываются программно. DAC channel1 data output register (DAC_DOR1) Смещение адреса: 0x2С Значение после сброса: 0x0000 0000 Биты 31:12 Зарезервированы Биты 11:0 DACC1DOR[11:0]: выходные данные канала 1 Эти биты только для чтения, они содержат выходные данные для канала 1 DAC channel2 data output register (DAC_DOR2) Смещение адреса: 0x30 Значение после сброса: 0x0000 0000 Биты 31:12 Зарезервированы Биты 11:0 DACC2DOR[11:0]: выходные данные канала 2 Эти биты только для чтения, они содержат выходные данные для канала 2 DAC status register (DAC_SR) Смещение адреса: 0x34 Значение после сброса: 0x0000 0000 Биты 31:30 Зарезервированы Бит 29 DMAUDR2: Флаг отставания запроса DMA в канале 2 Этот бит устанавливается аппаратно и очищается программно (записью 1) 0: Ошибка отставания запроса DMA в канале 2 не появлялась 1: В канале 2 произошла ошибка отставания запроса DMA (частота запуска преобразования выше, чем возможность обслуживания запроса DMA) Биты 28:14 Зарезервированы Бит 13 DMAUDR1: Флаг отставания запроса DMA в канале 1 Этот бит устанавливается аппаратно и очищается программно (записью 1) 0: Ошибка отставания запроса DMA в канале 1 не появлялась 1: В канале 1 произошла ошибка отставания запроса DMA (частота запуска преобразования выше, чем возможность обслуживания запроса DMA) Биты 12:0 Зарезервированы Карта размещения регистров ЦАП в пространстве памяти