Схемотехника ЭВМ - Корпоративный портал ТПУ

реклама

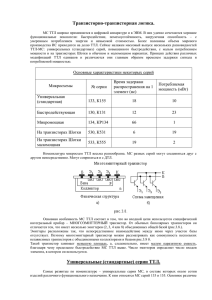

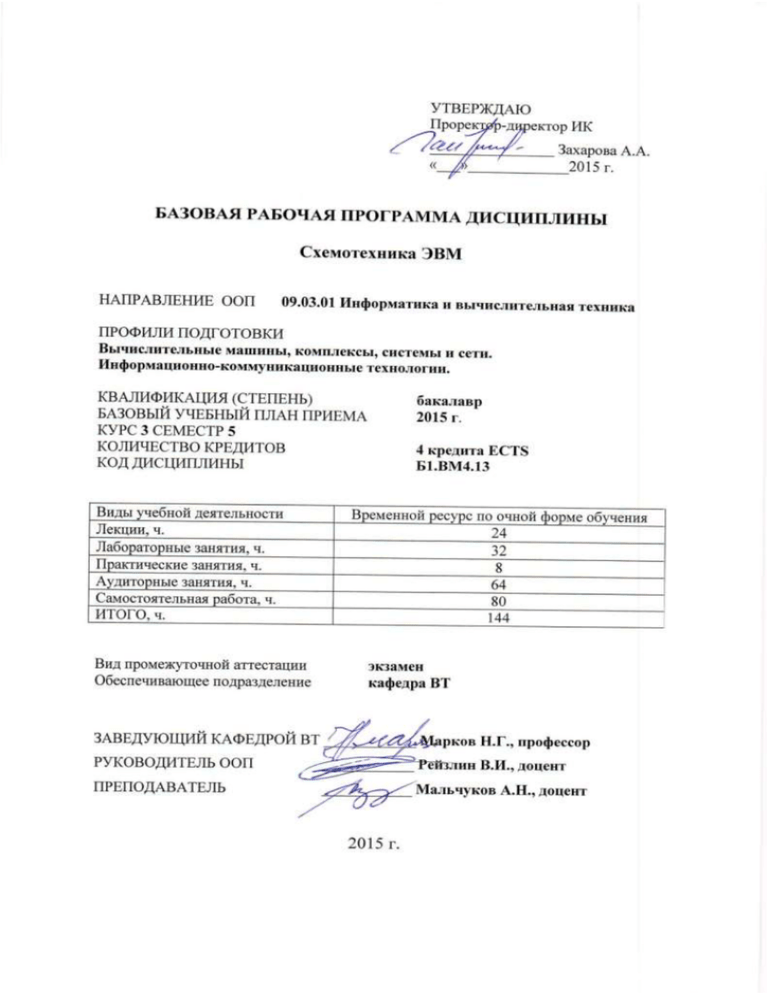

УТВЕРЖДАЮ Проректор-директор ИК ________________ Захарова А.А. «___»_____________2015 г. БАЗОВАЯ РАБОЧАЯ ПРОГРАММА ДИСЦИПЛИНЫ Схемотехника ЭВМ НАПРАВЛЕНИЕ ООП 09.03.01 Информатика и вычислительная техника ПРОФИЛИ ПОДГОТОВКИ Вычислительные машины, комплексы, системы и сети. Информационно-коммуникационные технологии. КВАЛИФИКАЦИЯ (СТЕПЕНЬ) БАЗОВЫЙ УЧЕБНЫЙ ПЛАН ПРИЕМА КУРС 3 СЕМЕСТР 5 КОЛИЧЕСТВО КРЕДИТОВ КОД ДИСЦИПЛИНЫ Виды учебной деятельности Лекции, ч. Лабораторные занятия, ч. Практические занятия, ч. Аудиторные занятия, ч. Самостоятельная работа, ч. ИТОГО, ч. Вид промежуточной аттестации Обеспечивающее подразделение бакалавр 2015 г. 4 кредита ECTS Б1.ВМ4.13 Временной ресурс по очной форме обучения 24 32 8 64 80 144 экзамен кафедра ВТ ЗАВЕДУЮЩИЙ КАФЕДРОЙ ВТ ____________ Марков Н.Г., профессор РУКОВОДИТЕЛЬ ООП ____________ Рейзлин В.И., доцент ПРЕПОДАВАТЕЛЬ ____________ Мальчуков А.Н., доцент 2015 г. 1. ЦЕЛИ ОСВОЕНИЯ ДИСЦИПЛИНЫ Целями освоения модуля являются формирование у обучающихся: знаний студентами вопросов теории и практики интегральной схемотехники с применением современных информационных технологий; готовности применять полученные знания для решения инженерных задач; способности ставить и решать схемотехнические задачи, связанные с выбором элементной базы при заданных требованиях и параметрах (временных, мощностных, габаритных и надёжностных); мотивации к самообразованию за счет активизации самостоятельной познавательной деятельности. Поставленные цели полностью соответствуют целям (Ц1-Ц5) ООП. 2. МЕСТО МОДУЛЯ В СТРУКТУРЕ ООП Дисциплина «Схемотехника ЭВМ» (Б1.ВМ4.13) является базовой профессионального цикла. Для успешного усвоения дисциплины «Схемотехника ЭВМ» необходимы знания базовых понятий информатики, форм представления и преобразования информации в компьютере, теорию булевых функций; умения применять вычислительную технику для решения практических задач, оперировать элементами алгебры логики, выполнять синтез автоматов, проводить анализ схем управляющих автоматов. Владеть навыками работы на персональном компьютере. Модулю «Схемотехника ЭВМ» предшествует освоение дисциплин (ПРЕРЕКВИЗИТЫ): «Информатика 1.2» (Б1.БМ2.4). «Дискретная математика» (Б1.ВМ4.8). «Электротехника 1.3» (Б1.БМ3.4). «Электроника 1.3» (Б1.БМ3.5). Содержание разделов дисциплины «Схемотехника ЭВМ» согласовано с содержанием дисциплин, изучаемых параллельно (КОРРЕКВИЗИТЫ): «Основы теории передачи данных» (Б1.ВМ5.1.1). «Теория автоматов» (Б1.ВМ5.1.2). 3. Результаты освоения модуля В соответствии с требованием ООП освоение модуля направлено на формирование у студентов следующих компетенций (результатов обучения), в т. ч. в соответствии с ФГОС (табл. 1). 2 Таблица 1 Составляющие результатов обучения, которые будут получены при изучении данной дисциплины Результаты обучения (компетенции из ФГОС) Р4 (ОК-7, ОПК-2, 4 ПК- 1, 2) Составляющие результатов обучения Код Умения Код Код Знания З.4.4 Принципы построения, параметры и характеристики цифровых и аналоговых элементов ЭВМ, функциональные узлы комбинационного и последовательностного типа. У.4.4 Ставить и решать В.4.4 схемотехнические задачи, связанные с выбором системы элементов при заданных требованиях и параметрах (временных, мощностных, габаритных и надёжностных). Владение опытом Владеть методами выбора элементной базы для построения различных архитектур вычислительных средств. В результате освоения модуля «Схемотехника ЭВМ» студентами должны быть достигнуты следующие результаты (табл. 2): Таблица 2 Планируемые результаты освоения дисциплины № п/п РД1 РД2 РД3 РД4 Результат Знать основные параметры интегральных схем. Уметь пользоваться справочной научнотехнической литературой. Знать системы элементов ТТЛ, ТТЛШ, р-МОП, n-МОП, КМОП, оптоэлектронные ИС. Уметь производить проверку работоспособности разработанных схем с помощью физического моделирования и моделирования с помощью пакета Multisim. Знать триггерные устройства и функциональные узлы последовательностного типа: регистры, счетчики. Уметь производить согласование различных систем элементов при их совместном использовании. Знать функциональные узлы комбинационного типа: дешифраторы, шифраторы, мультиплексоры, демультиплексоры, сумматоры, преобразователи кодов, компараторы, АЛУ, схемы контроля. Уметь проектировать устройства на основе МИС, СИС комбинационного и последовательностного типов, обеспечивая требуемые быстродействия, помехоустойчивость и надежность; разрабатывать устройства на основе БИС/СБИС с программируемой структурой с помощью САПР Quartus II. 4. Структура и содержание модуля Раздел 1. Основные характеристики и классификация интегральных схем Понятие интегральной схемы (ИС). Классификации ИС. Понятие серии микросхем, типа микросхем. Уровень интеграции. Условное обозначение микросхем согласно ГОСТ. Перечень лабораторных работ по разделу: 1. Изучение системы Multisim. 3 Раздел 2. Элементная база серий малых, средних, больших ИС и микропроцессоров Классификация цифровых схем по принципу схемотехнического построения. Элементы транзисторно-транзисторной логики (ТТЛ). Микросхемы ТТЛ с транзисторами Шотки (ТТЛШ). Элемент с открытым коллектором, элемент с тремя состояниями выхода, использование этих элементов. Цифровые ИМС на униполярных транзисторах (р-МОП, n-МОП, КМОП). Элемент КМОП с тремя состояниями выхода. Сопряжение микросхем ТТЛШ и КМОП. Оптроны и оптоэлектронные интегральные схемы, их применение. Перечень лабораторных работ по разделу: 2. Изучение базовых элементов ИС ТТЛ, КМОП. Раздел 3. Триггерные устройства Классификация триггерных устройств. Основные типы триггеров: RS, D, T, DV, TV, JK. Асинхронные триггеры, синхронные триггеры, тактируемые уровнем (статические); триггеры, тактируемые фронтом (динамические); одноступенчатые и многоступенчатые триггеры. Перечень лабораторных работ по разделу: 3. Изучение учебно-лабораторного комплекса SDK 6.1. 4. Исследование работы триггеров на макете SDK 6.1. Раздел 4. Функциональные узлы последовательностного типа Регистры и регистровые файлы. Классификация регистров. Регистровые файлы. Счетчики. Классификация счётчиков. Двоичные и недвоичные счётчики. Счётчики прямого и обратного счётов. Реверсивные счётчики. Методы повышения быстродействия счётчиков. Двоично-кодированные счётчики с произвольным модулем счёта. Перечень лабораторных работ по разделу: 5. Исследование работы счётчиков на макете SDK 6.1. Раздел 5. Функциональные узлы комбинационного типа Мультиплексоры и демультиплексоры. Дешифраторы и шифраторы. Сумматоры. Схемы одноразрядного сумматора. Многоразрядные сумматоры с последовательным, параллельным переносом. Сумматоры групповой структуры. Арифметикологические устройства и блоки ускоренного переноса. Матричные умножители. Компараторы. Преобразователи кодов. Схемы контроля. Перечень лабораторных работ по разделу: 6. Исследование работы дешифраторов и шифраторов на макете SDK 6.1. 7. Исследование работы мультиплексоров на макете SDK 6.1. Раздел 6. Синхронизация в цифровых устройствах Переходные процессы в логических схемах. Временные состязания сигналов (эффект «гонок»). Назначение синхронизации. Система двухфазной синхронизации. Однофазная синхронизация. Понятие тактирования. Перечень лабораторных работ по разделу: 4. Исследование работы триггеров на макете SDK 6.1. 4 5. Исследование работы счётчиков на макете SDK 6.1. 5. Организация и учебно-методическое обеспечение самостоятельной работы студентов 5.1 Виды и формы самостоятельной работы Самостоятельная работа студентов включает текущую и творческую проблемно-ориентированную самостоятельную работу (ТСР). Текущая СРС направлена на углубление и закрепление знаний студента, развитие практических умений и включает: работу с лекционным материалом; подготовку к практическим; опережающую самостоятельную работу; изучение тем, вынесенных на самостоятельную проработку; выполнение домашних заданий; подготовку к экзамену. Творческая самостоятельная работа включает: поиск, анализ научных публикаций; выполнение индивидуального домашнего задания. 5.2 Контроль самостоятельной работы Оценка результатов самостоятельной работы организуется следующим образом: входной контроль; выполнение и защита лабораторных работ; рубежный контроль в виде одного коллоквиума по теоретической части; выполнение индивидуального задания и его защита. 6. Средства текущей и промежуточной оценки качества освоения дисциплины Оценка качества освоения дисциплины производится по результатам следующих контролирующих мероприятий: Контролирующие мероприятия Входной контроль Выполнение и защита 7 лабораторных работ Коллоквиум Индивидуальное домашнее задание Экзамен Результаты обучения по дисциплине РД1 – РД4 РД1 – РД2 РД1 – РД4 РД1 – РД4 Для оценки качества освоения дисциплины при проведении контролирующих мероприятий предусмотрены следующие средства: перечень вопросов для входного контроля; вопросы для коллоквиума; перечень вопросов для экзамена; пример экзаменационного билета. Вопросы входного контроля 5 1. Двоичная, восьмеричная, шестнадцатеричная системы счисления. Представление произвольного числа Х в указанных системах счисления в виде полинома. Таблица соответствия десятичных чисел от 0 до 17 числам в указанных системах. 2. Переведите из десятичной системы счисления в двоичную следующие числа: а) 623; б) 1455; 3. Переведите числа: а) 1111010102; – в восьмеричную, десятичную, шестнадцатеричную системы счисления; б) 3278; 7148 в двоичную, десятичную, шестнадцатеричную системы счисления; в) B816; AE16 в двоичную, восьмеричную десятичную системы счисления. 4. Алгоритм построения СовДНФ по таблице истинности функции. 5. Алгоритм построения СовКНФ по таблице истинности функции. 6. Не полностью определённые булевы функции, способы их задания, доопределение. Вопросы для коллоквиума 1. Понятие интегральной схемы. Типы интегральных схем (ИС) по технологическому признаку. Составляющие стоимости ИС и пути ее уменьшения. Классификация ИС по степени интеграции. 2. Схемы И, ИЛИ на диодах, их работа. Оптоэлектронные ИС. 3. Базовый элемент транзисторно-транзисторной логики (ТТЛ: принципиальная схема, работа элемента). Понятие нагрузочной способности элемента ИС ТТЛ, как она определяется? 4. Базовый элемент ИС диодно-транзисторных схем на диодах и транзисторах Шотки (принципиальная схема 530/531, 533/555, отличия от классических ТТЛ). Почему в выходном каскаде ТТЛ ИС возникают броски тока и как с ними бороться? 5. Схемы базовых элементов серий 1531, 1533.Отличие серий 1531, 1533 от 531 и 533. 6. Логические элементы ИС ТТЛ с тремя состояниями выхода. Подключение неиспользуемых логических элементов и входов ИС ТТЛ? 7. Логические элементы ИС ТТЛ с открытым коллектором. Получение монтажного «И» на элементах с открытым коллектором. Схемы подключения индикации и формулы расчёта RН. 8. Цифровые ИС на n-MOП структурах (принципиальная схема инвертора, работа; принципиальная схема базового элемента, его работа). Сформулировать отличия n-МОП от p-МОП структур. 6 9. Цифровые ИС на КМОП-стуктурах (принципиальная схема инвертора и его работа; принципиальная схема элемента ИЛИ-НЕ и его работа). Особенности применения ИС КМОП. 10. Достоинства и недостатки ИС КМОП. Согласование ИС ТТЛ-уровней с ИС КМОП, ИС КМОП с ИС ТТЛ-уровней. 11. Кроссбар-архитектуры. 12. Общие сведения об оптоэлектронных приборах, используемых в вычислительной технике. Обобщенная структурная схема оптрона. Оптопары (виды оптопар, некоторые параметры оптопар). 13. Изолирующие ИС на основе iCoupler. 14. Классификация триггеров. Асинхронный RS-триггер (схемы на элементах ИНЕ, ИЛИ-НЕ, таблицы функционирования и временные диаграммы, время задержки). 15. Синхронный (статический) одноступенчатый и двухступенчатый RSтриггеры (функциональная схема на элементах И-НЕ, ИЛИ-НЕ, работа, время задержки). 16. Синхронный (динамический) RS-триггер (функциональная схема на элементах И-НЕ, работа, время задержки). Построение D-, Т-, JK-триггеров на основе синхронных (одноступенчатых, двухступенчатых, динамических) RSтриггеров. 1. 2. 3. 4. 5. 6. 7. Перечень вопросов для экзамена Понятие интегральной схемы. Типы интегральных схем (ИС) по технологическому признаку. Составляющие стоимости ИС и пути ее уменьшения. Классификация ИС по степени интеграции. Схемы И, ИЛИ на диодах, их работа. Оптоэлектронные ИС. Базовый элемент транзисторно-транзисторной логики (ТТЛ: принципиальная схема, работа элемента). Понятие нагрузочной способности элемента ИС ТТЛ, как она определяется? Базовый элемент ИС диодно-транзисторных схем на диодах и транзисторах Шотки (принципиальная схема 530/531, 533/555, отличия от классических ТТЛ). Почему в выходном каскаде ТТЛ ИС возникают броски тока и как с ними бороться? Схемы базовых элементов серий 1531, 1533.Отличие серий 1531, 1533 от 531 и 533. Логические элементы ИС ТТЛ с тремя состояниями выхода. Подключение неиспользуемых логических элементов и входов ИС ТТЛ? Логические элементы ИС ТТЛ с открытым коллектором. Получение монтажного «И» на элементах с открытым коллектором. Схемы подключения индикации и формулы расчёта RН. 7 8. Цифровые ИС на n-MOП структурах (принципиальная схема инвертора, работа; принципиальная схема базового элемента, его работа). Сформулировать отличия n-МОП от p-МОП структур. 9. Цифровые ИС на КМОП-стуктурах (принципиальная схема инвертора и его работа; принципиальная схема элемента ИЛИ-НЕ и его работа). Особенности применения ИС КМОП. 10. Достоинства и недостатки ИС КМОП. Согласование ИС ТТЛ-уровней с ИС КМОП, ИС КМОП с ИС ТТЛ-уровней. 11. Кроссбар-архитектуры. 12. Общие сведения об оптоэлектронных приборах, используемых в вычислительной технике. Обобщенная структурная схема оптрона. Оптопары (виды оптопар, некоторые параметры оптопар). 13. Изолирующие ИС на основе iCoupler. 14. Классификация триггеров. Асинхронный RS-триггер (схемы на элементах ИНЕ, ИЛИ-НЕ, таблицы функционирования и временные диаграммы, время задержки). 15. Синхронный (статический) одноступенчатый и двухступенчатый RSтриггеры (функциональная схема на элементах И-НЕ, ИЛИ-НЕ, работа, время задержки). 16. Синхронный (динамический) RS-триггер (функциональная схема на элементах И-НЕ, работа, время задержки). Построение D-, Т-, JK-триггеров на основе синхронных (одноступенчатых, двухступенчатых, динамических) RSтриггеров. 17. Счётчики (классификация, двоичные счётчики прямого и обратного счёта, таблицы функционирования и временные диаграммы работы). 18. Счётчики (методы повышения быстродействия двоичных счётчиков, недвоичные счётчики: Джонсона, 1 из N – схемы, временные диаграммы работы, таблицы функционирования). 19. Синхронизация в цифровых устройствах (понятия синхронизации, тактирования, синхронизация статических, динамических ЦУ). 20. Регистры (классификация, схемы сдвигающих регистров: DSL, DSR, реверсивные). 21. Регистровые файлы (описание, ИС К555ИР26: функциональная схема, таблица функционирования). 22. Построение памяти требуемого объёма на стандартных ИС 1К-1 (схемы: ЗУ 1К-4, 4К-1, 4К-4). 23. Реализация мультиплексоров (назначение, таблица функционирования, мультиплексная формула, реализация мультиплексора 4-1 на элементах И-НЕ, наращивание числа входов мультиплексора: реализовать мультиплексор 32-1 на мультиплексорах 8-1 с тремя состояниями выхода и дешифраторе). 8 24. Применение мультиплексоров для построения функциональных узлов. Демультиплексоры (описание, УГО, таблица функционирования). 25. Схемотехническая реализация двоичных дешифраторов (описание функционирования, обозначение на функциональной схеме, схема дешифратора 3-8 на элементах И, наращивание размерности дешифратора: реализовать схему двоичного дешифратора 5-32 на дешифраторах 2-4, 3-8 ТТЛШ-серий). 26. Двоичные и приоритетные шифраторы (назначение двоичного шифратора, его условное обозначение на функциональной схеме; функция, выполняемая приоритетным шифратором, таблица функционирования восьмиразрядного приоритетного шифратора, выражения для выходов приоритетного шифратора, обозначение на функциональной схеме приоритетного шифратора). 27. Наращивание размерности приоритетного шифратора. Указатели старшей единицы. 28. Компараторы (определение компаратора, выражения для компаратора: признак равенства разрядов, признак неравенства разрядов, признак равенства слов; принципиальная схема четырехразрядного компаратора на основе сумматора). 29. Наращивание разрядности сравниваемых слов ИС компараторов (схемы последовательного соединения, параллельного, таблица истинности ИС К555СП1, схема компаратора для сравнения 24-х разрядных слов на ИС К555СП1). 30. Синтез схемы одноразрядного сумматора (таблица функционирования, СДНФ функций суммы и переноса, принципиальная схема одноразрядного сумматора на элементах И-НЕ, обозначение на функциональной схеме). 31. Сумматоры групповой структуры (групповой сумматор с цепным переносом, сумматор с условным переносом, сумматор с параллельным и межгрупповым переносом). 32. АЛУ и блоки ускоренного переноса. 33. Матричные умножители (математические выражения, схема множительносуммирующего блока для четырехразрядных сомножителей). 34. Преобразователи кодов. 35. Организация контроля правильности функционирования устройств обработки данных. Пример экзаменационного билета ЭКЗАМЕНАЦИОННЫЙ БИЛЕТ № 2 1. Какую функцию в положительной логике выполняет логический элемент, имеющий приведенную ниже схему? (5 б.) 9 +UИ.П. EZ Вход Выход EZ Заполните таблицу функционирования схемы: Вход EZ 0 0 1 0 0 1 1 1 EZ 1 1 0 0 Выход 2. Определите функциональное назначение данной принципиальной схемы. (10 б.) 10 a0 1 b0 2 a1 4 b1 5 a2 9 b2 10 a3 12 b3 =1 1 3 1 6 3 8 5 11 9 =1 ◊ 2 ◊ 4 ◊ 6 ◊ 8 ◊ 10 ◊ 12 F 1 1 =1 =1 1 13 1к 1 11 +5В 1 13 3. Разработать функциональную схему цифрового автомата, выполняющего следующую функцию: а) в первом такте все разряды устанавливаются в состояние «1», кроме старшего разряда, который должен установиться в состояние «0». б) в следующих тактах в состояние «0» устанавливается предыдущий разряд, и, в зависимости от значения управляющего сигнала, изменяется/не изменяется состояние текущего разряда (перебор разрядов от старшего к младшему): • если управляющий сигнал равен «1», то состояние разряда не должно измениться; • если управляющий сигнал равен «0», то предыдущий разряд должен установиться в состояние «0». Примечание: разрядов в цифровом автомате – 9. Генератор тактовых сигналов начинает работу по сигналу «старт» (активный уровень нулевой), автоматически прекращает работу после выдачи 9-го импульса. Автомат должен быть синхронизирован передним фронтом тактового импульса. (15 б.) Устно, без предварительной подготовки: 4. Теоретический вопрос по выбору преподавателя из утверждённого списка. (10 б.) 7. Рейтинг качества освоения дисциплины Оценка качества освоения дисциплины в ходе текущей и промежуточной аттестации обучающихся осуществляется в соответствии с «Руководящими материалами по текущему контролю успеваемости, промежуточной и итоговой аттестации студентов Томского политехнического университета», утвержденными приказом ректора № 77/од от 29.11.2011 г. В соответствии с «Календарным планом изучения дисциплины»: 11 текущая аттестация, направленная на оценку качества усвоения теоретического материала (ответы на вопросы коллоквиума, работа на практических занятиях) и результатов практической деятельности (выполнение и защита отчетов по лабораторным работам и индивидуальных заданий), производится в течение семестра и оценивается в баллах (максимально 60 баллов), к моменту завершения семестра студент должен защитить все отчёты по лабораторным работам и набрать не менее 33 баллов; промежуточная аттестация (экзамен) производится в конце семестра и так же оценивается в баллах (максимально 40 баллов), на экзамене студент должен набрать не менее 22 баллов. Итоговый рейтинг по дисциплине определяется суммированием баллов, полученных в ходе текущей и промежуточной аттестаций. Максимальный итоговый рейтинг соответствует 100 баллам. 8. Учебно-методическое и информационное обеспечение дисциплины Основная литература: 1. Осокин, Александр Николаевич Схемотехника ЭВМ : учебное пособие / А. Н. Осокин, А. Н. Мальчуков; Национальный исследовательский Томский политехнический университет (ТПУ). — Томск: Изд-во ТПУ, 2013. — 166 с.: ил. — Библиогр.: с. 160-161. 2. Миленина, Светлана Александровна Электротехника, электроника и схемотехника : учебник и практикум для академического бакалавриата / С. А. Миленина; Московский государственный технический университет радиотехники, электроники и автоматики (МГТУ МИРЭА) ; под ред. Н. К. Миленина. — Москва: Юрайт, 2014. — 511 с. 3. Угрюмов Е.П. Цифровая схемотехника. 3-ое изд – СПб.: БХВ – Петербург, 2010, 816 с. Дополнительная литература: 4. Угрюмов, Евгений Павлович Проектирование элементов и узлов ЭВМ : учебное пособие / Е. П. Угрюмов. — Москва: Высшая школа, 1987. — 318 с.. 5. Зельдин, Евсей Аронович Цифровые интегральные микросхемы в информационно-измерительной аппаратуре / Е. А. Зельдин. — Ленинград: Энергоатомиздат, 1986. — 279 с.: ил.. — Библиогр.: с. 276-277 6. Оптоэлектроника / О. Н. Ермаков [и др.]. — М.: Янус-К, 2010 Ч. 2: Оптроника. — 2011. — 612 с.: ил.. — Библиогр.: с. 609.. — ISBN 978-58037-0506-2. 7. Нанотехнологии в электронике / под ред. Ю. А. Чаплыгина. Вып. 2. — Москва: Техносфера, 2013. — 686 с.: ил.. — Мир электроники. — Библиография в конце глав.. — ISBN 978-5-94836-353-0. 8. Райхлин, Вадим Абрамович Основы цифровой схемотехники : учебное пособие для вузов / В. А. Райхлин. — Казань: Изд-во Казанского ГТУ, 2000. — 352 с.. — ISBN 5-7579-0311-2 Internet-ресурсы: 1. Web-ресурс по адресу http://metod.vt.tpu.ru/edu/df/schem/guide/ 2. Кафедральный ftp-сервер: ftp://ftp.vt.tpu.ru/study/Malchukov/public/Schem/ 3. Осокин, Александр Николаевич Схемотехника ЭВМ [Электронный ресурс] : учебное пособие / А. Н. Осокин, А. Н. Мальчуков; Национальный исследова- 12 тельский Томский политехнический университет (ТПУ), Институт кибернетики (ИК), Кафедра вычислительной техники (ВТ). — 1 компьютерный файл (pdf; 4.4 MB). — Томск: Изд-во ТПУ, 2013. — Заглавие с титульного экрана. — Электронная версия печатной публикации. — Доступ из корпоративной сети ТПУ. — Системные требования: Adobe Reader. Схема доступа: http://www.lib.tpu.ru/fulltext2/m/2014/m052.pdf. 4. Дэвид М. Харрис и Сара Л. Харрис. Цифровая схемотехника и архитектура компьютера. 2-ое изд. — 1 компьютерный файл (pdf; 36.4 MB). — Системные требования: Adobe Reader. Схема доступа: ftp://ftp.vt.tpu.ru/study/Malchukov/public/Schem/Nashe_vse.pdf. Используемое программное обеспечение: 1. САПР Quartus II. 2. Программа Multisim. 9. Материально-техническое обеспечение дисциплины Лекционные и практические занятия проводятся в аудиториях с мультимедийным оборудованием. Лабораторные занятия проводятся в компьютерном классе на персональных компьютерах (12 рабочих мест). № п/п 1. 2. 3. Наименование оборудования Мультимедийное оборудование (компьютер, проектор, экран) ПК Intel Core 2 Е6320, 1,86 GHz Макеты SDK-6.1 Корпус, ауд., количество установок 10 корпус ТПУ, 307, 410 ауд. 10 корпус ТПУ, 408 ауд., 8 рабочих мест 10 корпус ТПУ, 408 ауд., 8 шт. Программа составлена на основе Стандарта ООП ТПУ в соответствии с требованиями ФГОС по направлению 09.03.01 «Информатика и вычислительная техника» и профилям подготовки «Вычислительные машины, комплексы, системы и сети», «Информационно-коммуникационные технологии». Программа одобрена на заседании кафедры вычислительной техники (протокол № 54 от « 22 » 06 2015 г.). Автор – доцент кафедры вычислительной техники Мальчуков Андрей Николаевич Рецензент – доцент, профессор кафедры вычислительной техники Ким Валерий Львович 13